今天我们来聊聊在计算机领域中非常关键的技术——DRAM(动态随机存取存储器)的内部结构和工作原理。

DRAM Arrays的基本结构

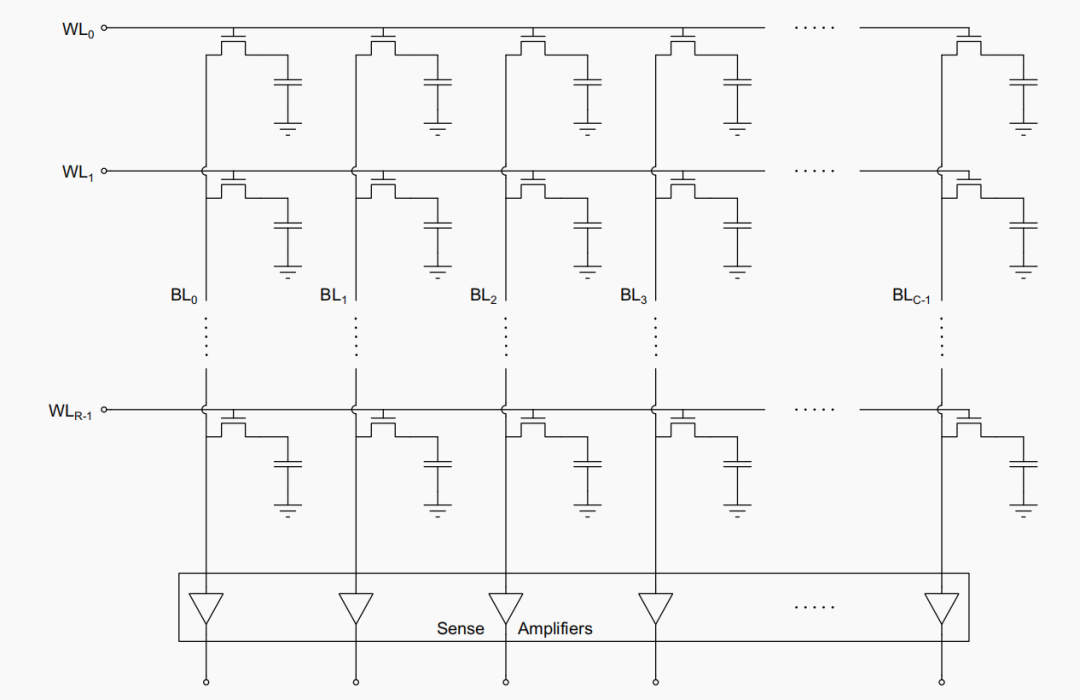

首先,DRAM通常被组织成一个矩形的存储单元阵列,这些存储单元按照行和列的方式排列。想象一下,就像一个巨大的表格,每个单元格都是一个存储cell。下图展示了一个简化的基本DRAM cell arrays结构,其中包含R行和C列的cell。一个典型的DRAM array可能会包含数百甚至数千个这样的cell。

访问DRAM cell

这些cell是如何被访问的呢?答案是通过行地址和列地址。行地址线(也就是我们常说的字线)连接到nMOS晶体管的栅极,而列线则连接到灵敏放大器。这种设计使得我们可以通过特定的行和列地址来定位并访问任何一个DRAM cell。

arrays大小的权衡

然而,arrays的大小并不是越大越好。更大的arrays虽然可以存储更多的信息,但它们也需要更长的字线和位线。更长的字线和位线意味着更高的电容,这会带来一些问题。首先,电容的增加会使得位线上的电压摆动在读取时变得非常微小,这使得检测变得困难。其次,更高的电容也意味着更大的arrays在操作时会更慢。

典型DRAM arrays的大小

在现代DRAM中,一个典型的arrays大小是8K字(行)乘以1024位(列)。这意味着每个DRAM芯片可以存储8192个数据单元,每个单元可以存储1024位数据。

DRAM banks的概念

你可能还听说过DRAM Banks。一个DRAM Banks通常包含4到16个DRAM arrays,这些arrays可以同时被访问。因此,每当内存控制器访问DRAM时,DRAM芯片会传输或接收与arrays数量相等的位数。每个array提供一个位到输出引脚。DRAM芯片被描述为xN,其中N指的是内存array和输出引脚的数量。例如,一个x8 DRAM表示DRAM至少有八个内存array,这意味着每次内存控制器访问DRAM时,DRAM会传输或接收8位。

8077

8077

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?