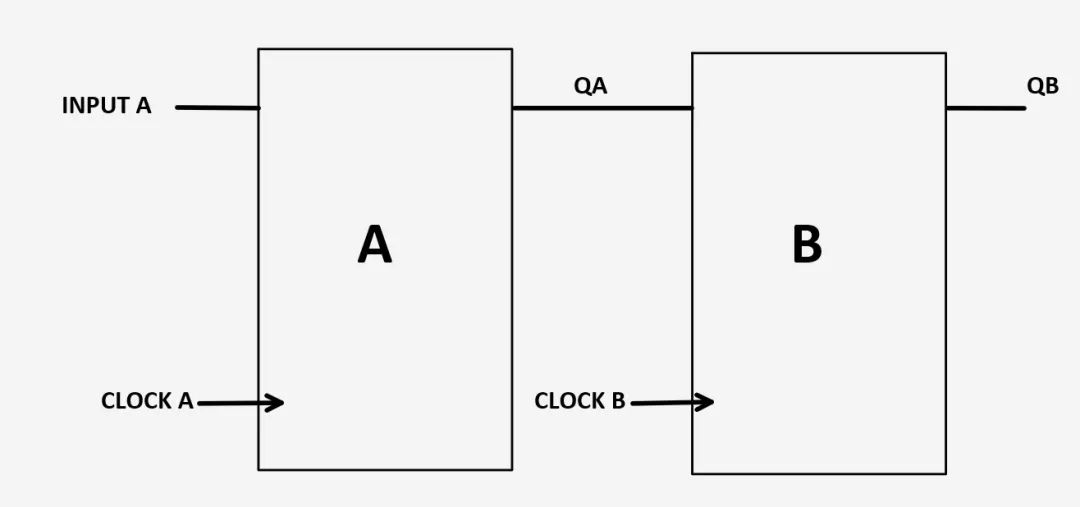

时钟域交叉(CDC)是指用于在ASIC IC或FPGA中管理数字系统内不同时钟域之间的数据传输的技术。下图1显示了CDC的场景。在这里,来自时钟域A的数据被传输到时钟域B。时钟A和时钟B可以具有不同的频率以及不同的相位。因此,两个时钟域彼此异步。

现代ASIC通常包含多个时钟域,每个时钟域都以其独立频率或相位运行。当数据信号在这些时钟域之间交叉时,确保数据传输可靠且无错误至关重要。CDC机制通过同步信号、管理时序约束和缓解亚稳态等问题来处理这项任务。

片上系统(SoC)中的不同子系统通常在不同的时钟上运行,并且可能具有不同的复位信号。例如,像SPI这样的外围子系统可能会在慢速的50 MHz时钟上运行,而高性能CPU集群最有可能在GHz范围内的时钟上运行。为了在这两个不同的时钟域之间传输数据,需要在时钟交叉边界上设置时钟(和复位)同步逻辑。

CDC的问题

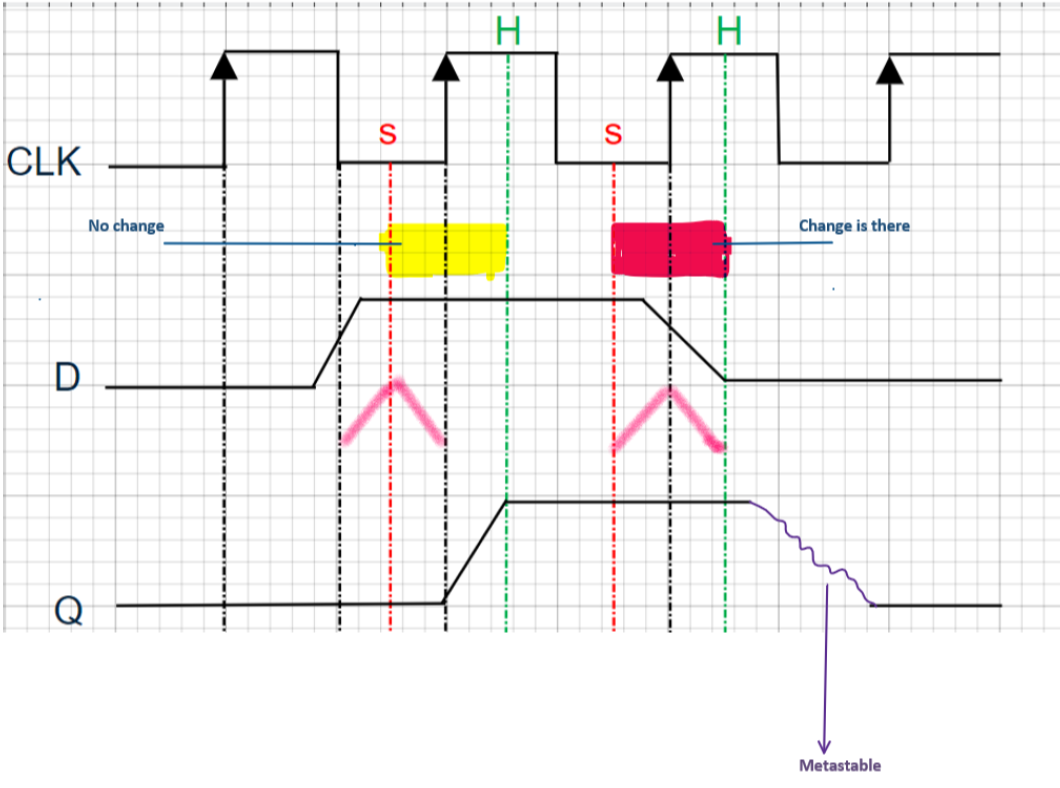

在ASIC中引入多个时钟域时,出现了不少问题。工程师面临的主要问题被称为亚稳态,如图2所示。亚稳态发生在使用多个时钟域的应用中。在深入研究这个话题之前,有几个重要的术语需要了解。

1)建立时间-它是时钟上升边缘之前的时间窗口。

2)保持时间-它是时钟上升边缘之后的时间窗口。

在上图中,CLK是时钟输入,D是数据输入,Q是输出。这里将考虑两个区域

黄色标记的区域

输入D给出准确的输出,因为数据在建立时间和保留时间上都没有变化

根据时钟信号上升边缘的D输入给出准确的输出

红色标记的区域

输入D在设置时间从1变为0

输出Q可以是0或1,这种不稳定状态称为亚稳态。这导致输出不准确。亚稳态对状态机具有巨大影响,因为错误可能导致状态机指向完全不同的状态,并破坏正在执行的进程。让我们讨论两个多个案例,在一个案例中,数据从慢时钟传输到快速时钟,在另一个案例中,数据从快时钟传输到慢时钟。

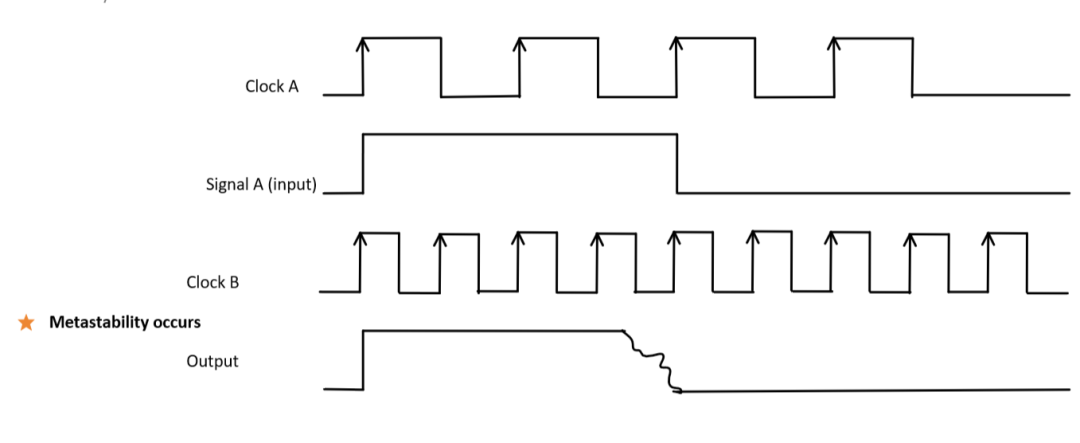

慢速时钟域到快时钟域

在这种情况下,源时钟比目标时钟慢。让我们考虑一个源时钟(时钟A)和目标时钟(时钟B)的例子。信号A由时钟B多次采样,因为假设由于之前讨论的不稳定的建立时间和保持时间而出现亚稳态,信号A的速度更快。输出不准确且使用无效。这种情况如下图3所示。

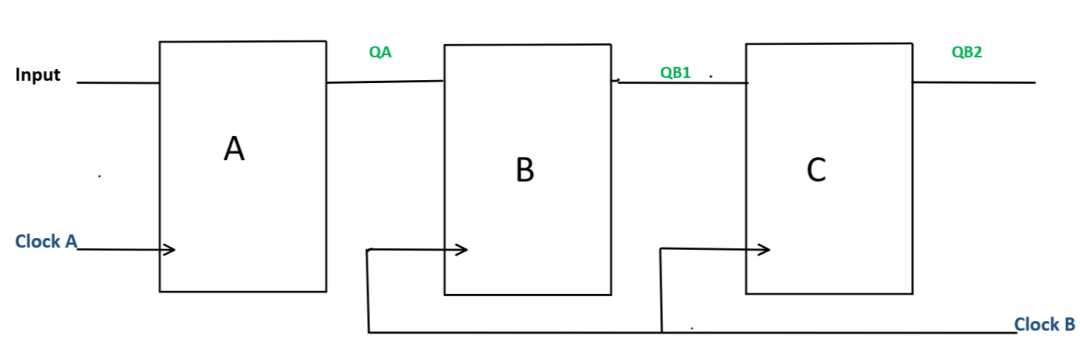

快时钟域到慢时钟域

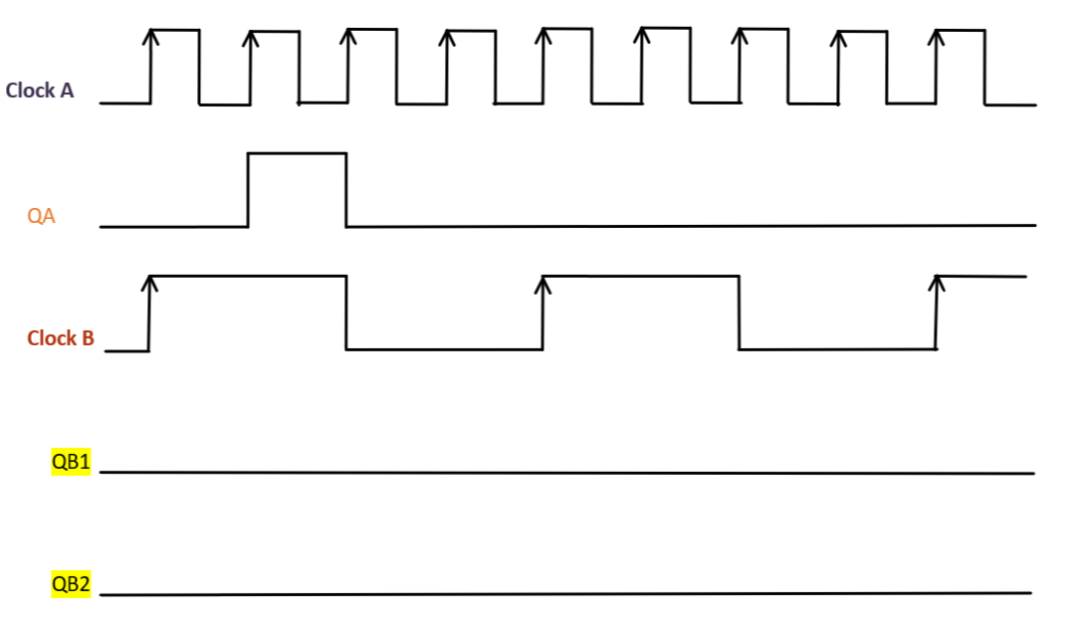

第二个条件是当系统在源处有一个快速时钟域,在目的地有一个慢时钟域。让我们考虑图4所示的这个电路。

较慢的时钟由于时钟较慢而错过输入信号QA,这导致了QB1和QB2的输出。数据完全丢失了。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?