#学习记录#

1 CDC跨时钟域

在同步设计中,整个设计都是使用同一个时钟源,所有的时钟的频率和相位都可以事先预知。在异步设计中有两个或以上的时钟,且时钟之间是同频不同相或不同频的关系异步时序设计的关键就是把数据或者控制信号正确的进行跨时钟域传输。

CDC:信号由一个时钟域传入另一个异步时钟域。

2 CDC产生的问题

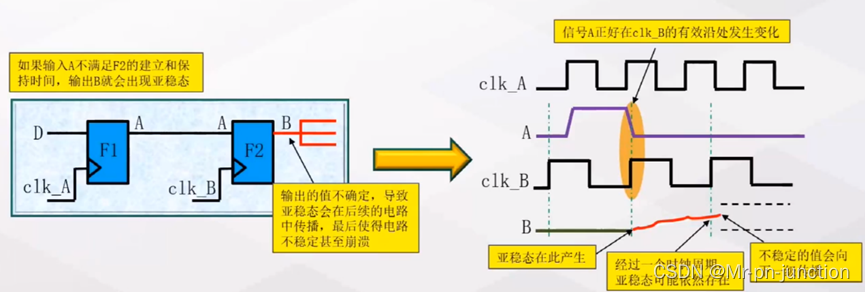

2.1 亚稳态

CDC会导致后续触发器的亚稳态,这也是绝大部分CDC问题的本质。

解决办法:

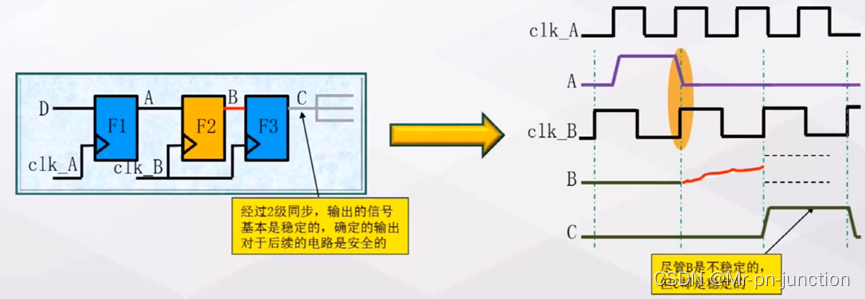

对于单信号来说,使用double ff构成同步器来进行信号的同步。

但使用double ff 只能保证c端结果的稳定,并不能保证c 端结果的正确性。

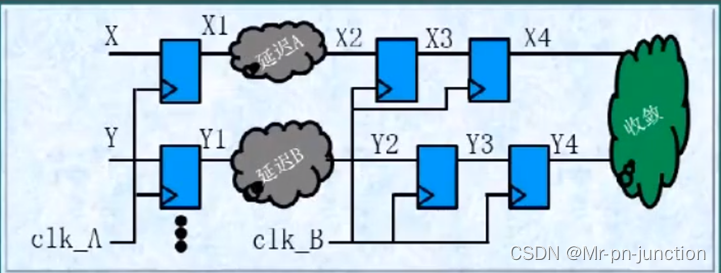

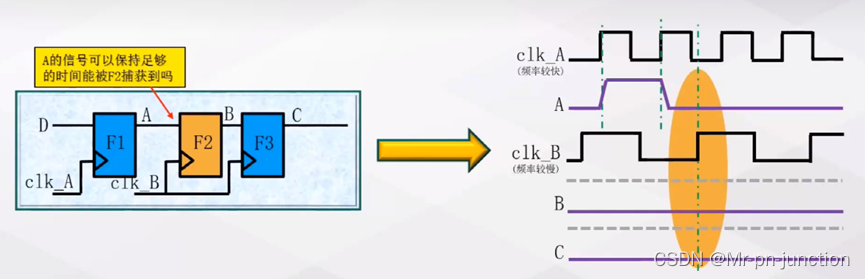

2.2 数据收敛

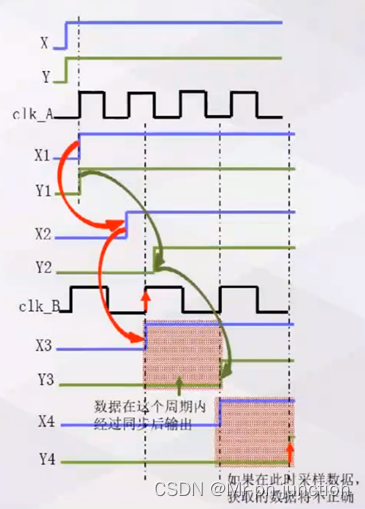

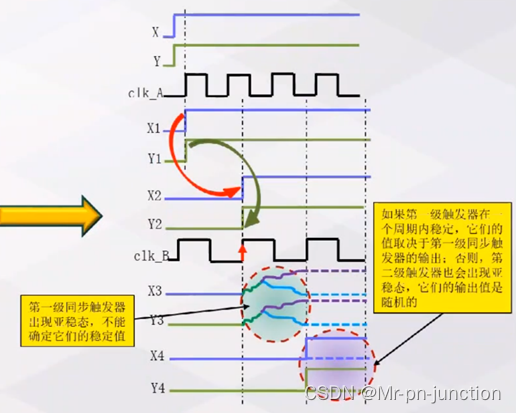

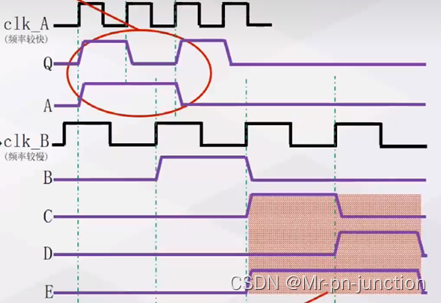

情况一:若不考虑CLKB时钟域的亚稳态问题,仅考虑延迟A与延迟B不同,则如下图所示:

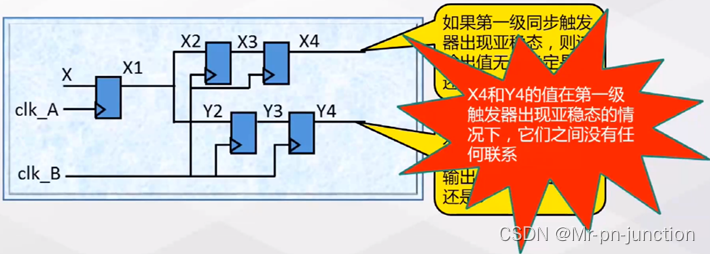

情况二:若考虑CLKB的亚稳态,不考虑延迟A与延迟B的不同则如下图所示:

解决方法:

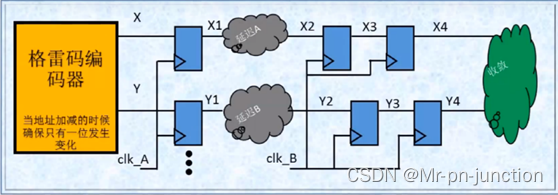

1、对于连续变化的信号如:FIFO的读写地址,可以采用格雷码编码。

2、对于无法使用格雷码编码的信号,可采用握手协议。

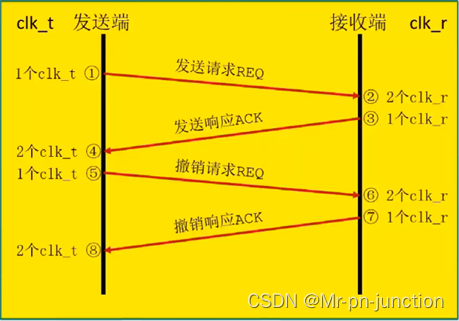

①发送端将并行的数据驱动到总线上,同时发出一个“数据有效”的请求信号REQ

②接收端识别到REQ有效,接收这组数据

③接收完毕之后向发送端返回一个响应信号ACK

④发送端识别响应信号ACK

⑤撤销请求信号REQ

⑥接收端检测请求信号REQ无效

⑦将响应信号ACK撤销

⑧发送端检测到应答信号ACK无效,开始新一轮的数据传输

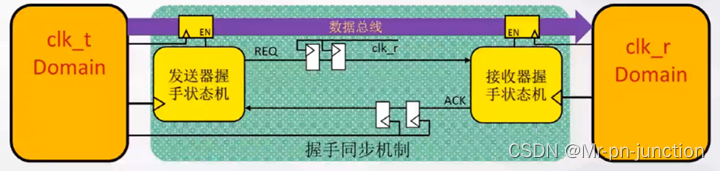

如图,REQ经过两级同步触发器传入接收端,ACK经过两级同步触发器传入发送端。握手协议有效期间,发送端必须保证数据总线上的数据稳定不变。

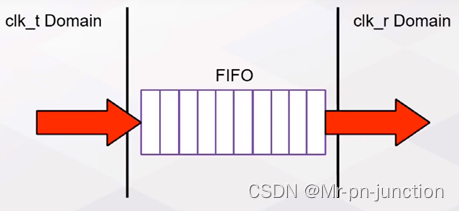

3、FIFO

发送端将数据写入FIFO中,接收端将数据读出,不存在跨时钟域问题。但是 数据在写入FIFO前需要检查FIFO是否满了,检查FIFO是否满需要将接收端读指针与发送端写指针对比,引入了读写指针的跨时钟域问题,同理数据在读出时也需要检查FIFO是否为空,同样存在此问题。但由于读写地址都是连续变化的,所以可以用格雷码编码的方式解决跨时钟域问题 。

①FSM用来实现对FIFO的读写功能

②比较器用来判断FIFO是否为空或者是否为满

③同步read_addr/write_addr用于将读写指针同步到相应的时钟域中

2.3 数据丢失

输入端信号不能保持足够的时间使得接收端不能采样到数据导致数据丢失。

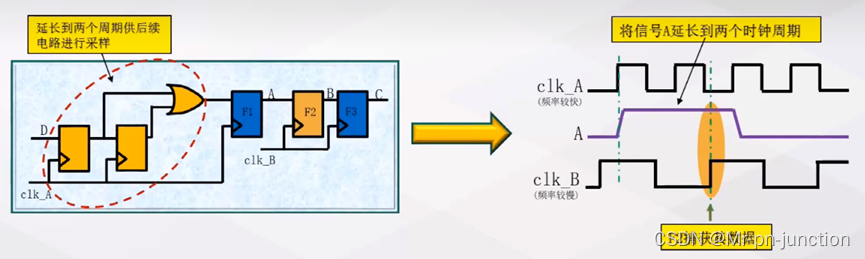

解决方法:

1、延长输入信号

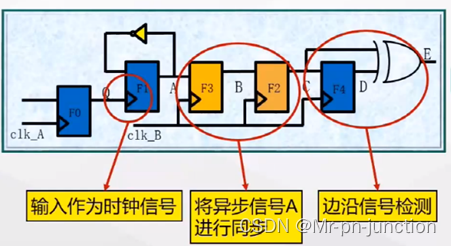

2、脉冲信号触发电路

无论Q持续多久,输出只有一个周期的高电平。

若Q变化太快则会导致输出的高电平连在一起。

2.4 多路扇出

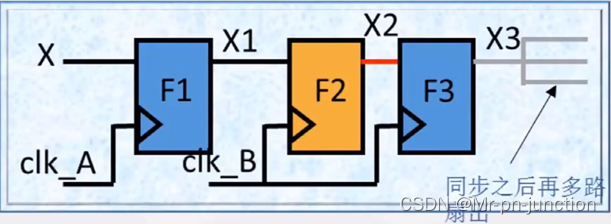

同一信号源经过不同的路径跨时钟域之后,多路扇出的值不一定相同。

解决办法:

将信号同步之后再多路扇出

2.5 异步复位

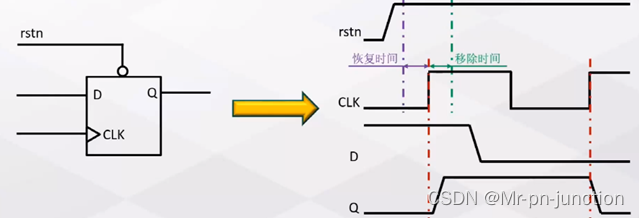

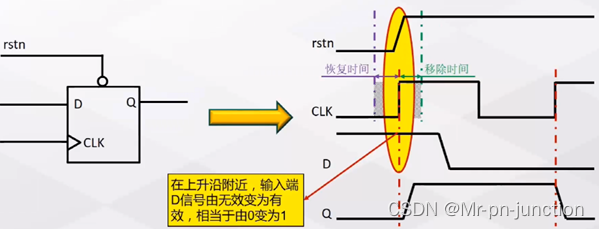

恢复时间:在有效的时钟沿到来之前,触发器的异步复位信号释放时所要提前释放的最小时间。

移除时间:在有效的时钟沿到来之后,触发器的异步复位信号释放时所要保持不变的最小时间。

异步复位信号释放时不满足恢复时间和移除时间。

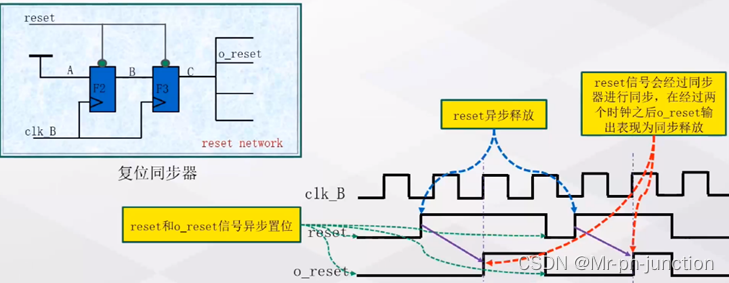

解决办法:

异步复位信号同步电路

参考文献

[1] CDC.CDC_哔哩哔哩_bilibili

1518

1518

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?