xilinx fpga千兆以太网+ddr内存读写测试代码

基于kcu105/kc705平台的10/100/1000m 以太网lwip通信+ddr4 内存读写测试 工程代码

ID:77500757867621066

喵了个哔哩哔哩哔

Xilinx FPGA千兆以太网+DDR内存读写测试代码

在现代计算机系统中,高速网络通信和高性能存储器是实现数据传输和处理的关键。而在一些特定的应用场景中,如数据中心、云计算、物联网等,对于高速以太网通信和DDR内存读写的需求更为迫切。为了满足这些需求,Xilinx FPGA平台提供了千兆以太网和DDR内存读写测试的代码。

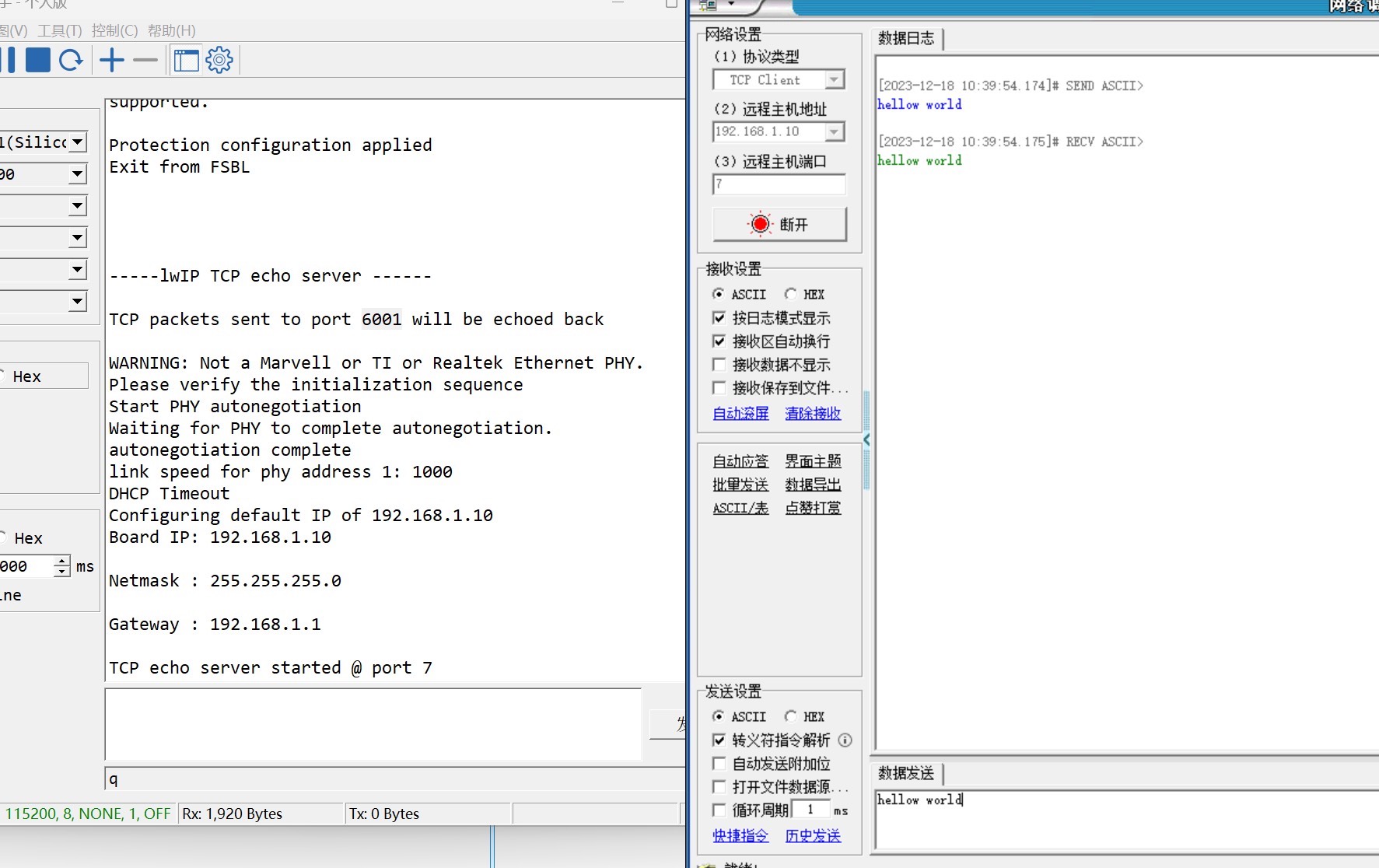

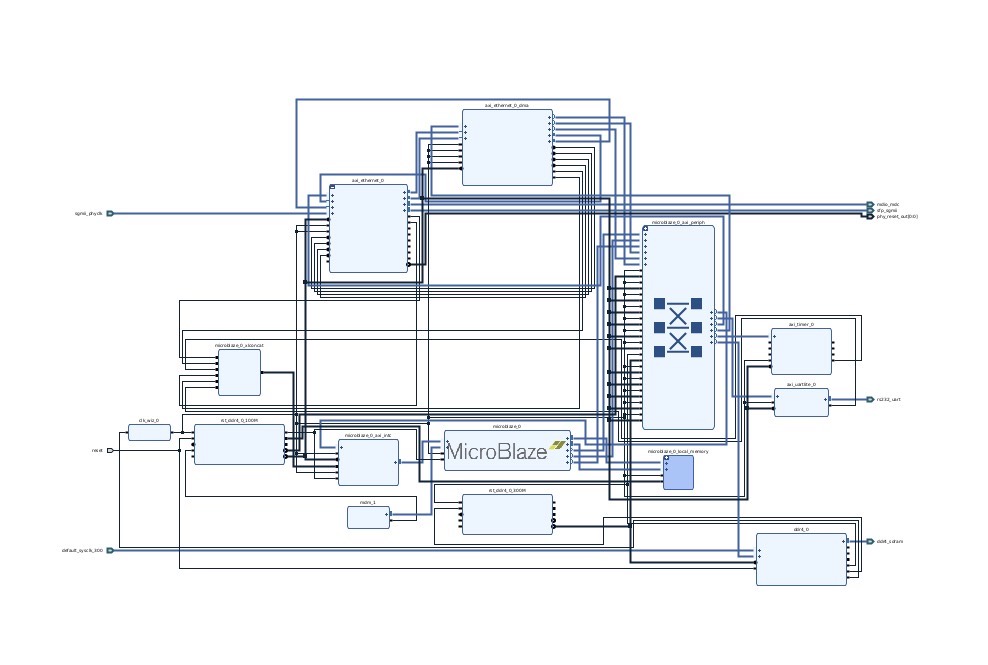

首先,我们来看一下基于KCU105和KC705平台的千兆以太网通信。以太网是一种标准的局域网通信协议,支持以太网的设备可以在一个局域网中进行数据的传输和通信。而在FPGA开发中,我们可以利用Xilinx提供的IP核来实现千兆以太网通信。通过使用Xilinx的KCU105和KC705平台,我们可以轻松地连接到千兆以太网,并实现数据的传输和通信。

其次,我们来讨论DDR内存读写测试。DDR内存是一种高速的随机存储器,常用于存储和读取大量数据。在FPGA开发中,我们可以利用Xilinx提供的DDR控制器和存储器IP核来实现DDR内存的读写操作。通过使用Xilinx的KCU105和KC705平台,我们可以向DDR内存中写入数据,并从中读取数据,以测试DDR内存的读写性能和稳定性。

基于以上两个关键技术,我们可以将千兆以太网和DDR内存进行结合,实现对DDR内存的高速读写测试。在测试过程中,我们可以通过千兆以太网将数据从外部设备传输到DDR内存,或者将DDR内存中的数据传输到外部设备。通过对数据的读写测试,我们可以评估DDR内存的性能和稳定性,并进行性能优化和问题排查。

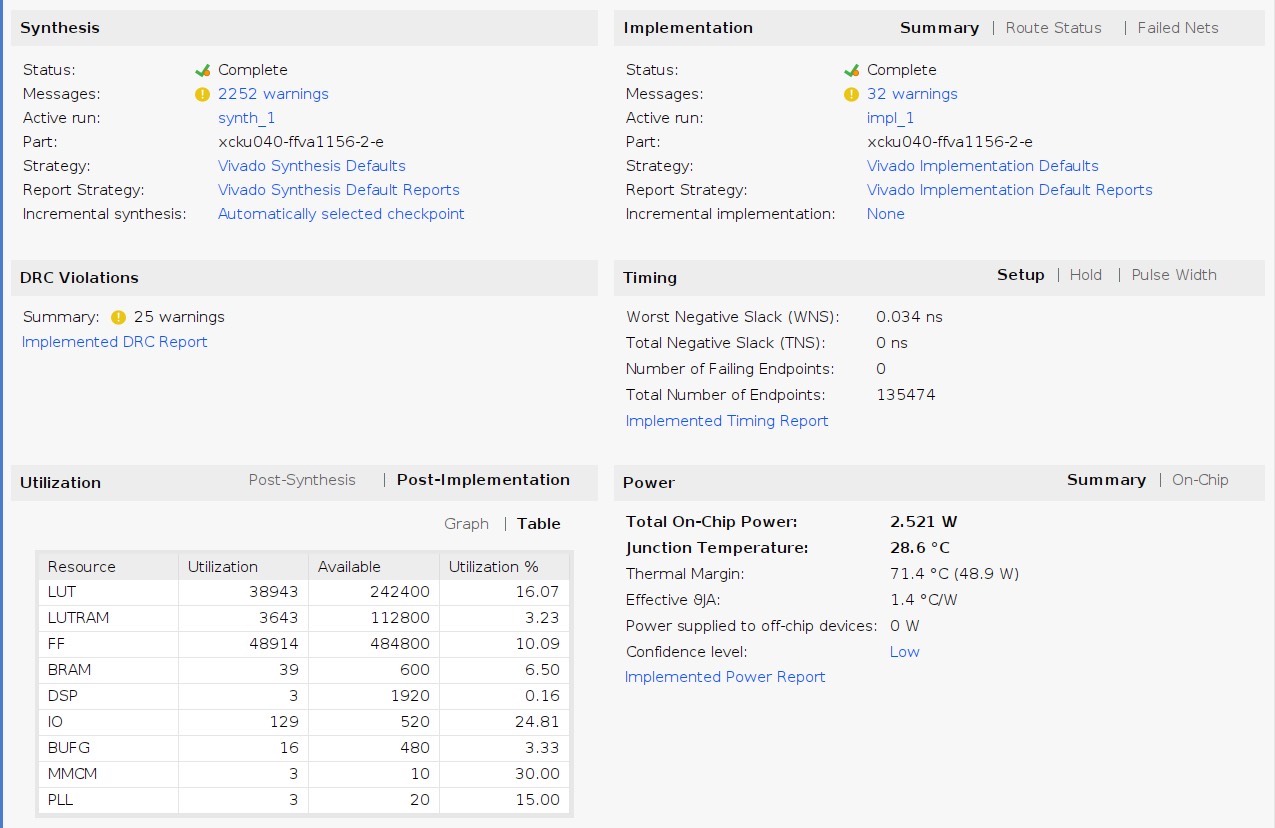

在实际的开发过程中,我们可以利用Xilinx的设计工具Vivado来编写和调试相应的代码。通过编写适当的硬件描述语言(HDL)代码和约束文件,我们可以将千兆以太网和DDR内存的功能集成到FPGA中,并进行仿真和实验验证。在验证过程中,我们可以通过观察数据传输和读写操作的结果,来评估系统的性能和功能的正确性。

总结起来,Xilinx FPGA千兆以太网+DDR内存读写测试代码提供了一种高效和可靠的方式来测试千兆以太网通信和DDR内存读写的性能和稳定性。通过利用Xilinx的KCU105和KC705平台,我们可以轻松地构建和验证相应的系统,并且进行性能优化和问题排查。这对于开发高速网络通信和高性能存储器的应用具有重要的意义,可以为相关领域的开发者和研究人员提供有力的支持。

(以上内容仅为示例,实际文章中请根据具体情况进行扩展和补充)

以上相关代码,程序地址:http://fansik.cn/757867621066.html

2698

2698

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?