电子技术——体效应和其他话题

本节我们简单介绍一些MOS管的体效应和其他话题。

底物的作用——体效应

在许多应用中,源极直接连接到底物(体极)B极,使得底物和沟道之间的pn结是零电压偏置。此时底物在电路中不发挥任何作用,可以被忽略。

在集成电路中,底物通常被大量的MOS所共用。为了保证底物和所有沟道之间的pn结都是截止状态,底物在NMOS中通常被连接到最小负电压源(在PMOS中连接到最大正电压源)。在这种情况下,反向偏置的pn结会对元器件造成影响。为了说明这一点,考虑一个NMOS并且让它的底物电压比源极电压低(此时pn结反向偏置)。反向偏置的电压将会扩大耗散区的体积,这回加深沟道的深度,这会导致 i D i_D iD 增大,为了使得MOS回到原来的状态上,就必须增大 v G S v_{GS} vGS 。

电压 V S B V_{SB} VSB 可以看做是改变了阈值电压 V t V_t Vt ,关系由下面的表达式给出:

V t = V t 0 + γ [ 2 ϕ f + V S B − 2 ϕ f ] V_t = V_{t0} + \gamma [\sqrt{2\phi_f + V_{SB}} - \sqrt{2\phi_f}] Vt=Vt0+γ[2ϕf+VSB−2ϕf]

在这里 V t 0 V_{t0} Vt0 是在 V S B = 0 V_{SB} = 0 VSB=0 条件下的阈值电压, ϕ f \phi_f ϕf 是一个物理参数一般情况是0.6V, γ \gamma γ 是制作工艺参数,由下面的表达式给出:

γ = 2 q N A ϵ s C o x \gamma = \frac{\sqrt{2qN_A\epsilon_s}}{C_{ox}} γ=Cox2qNAϵs

在这里 q q q 是电子电荷量, N A N_A NA 是p类型底物的掺杂浓度, ϵ s \epsilon_s ϵs 是硅的介电常数。

上式反应了增大 V S B V_{SB} VSB 会导致 V t V_t Vt 的增加,尽管 v G S v_{GS} vGS 保持恒定的情况下也会增大 i D i_D iD 。换句话说, V S B V_{SB} VSB 同样能控制 i D i_D iD 的大小,因此体极和栅极具有相同的控制 i D i_D iD 的能力,这个效应称为 体效应 。这里 γ \gamma γ 称为体效应参数。

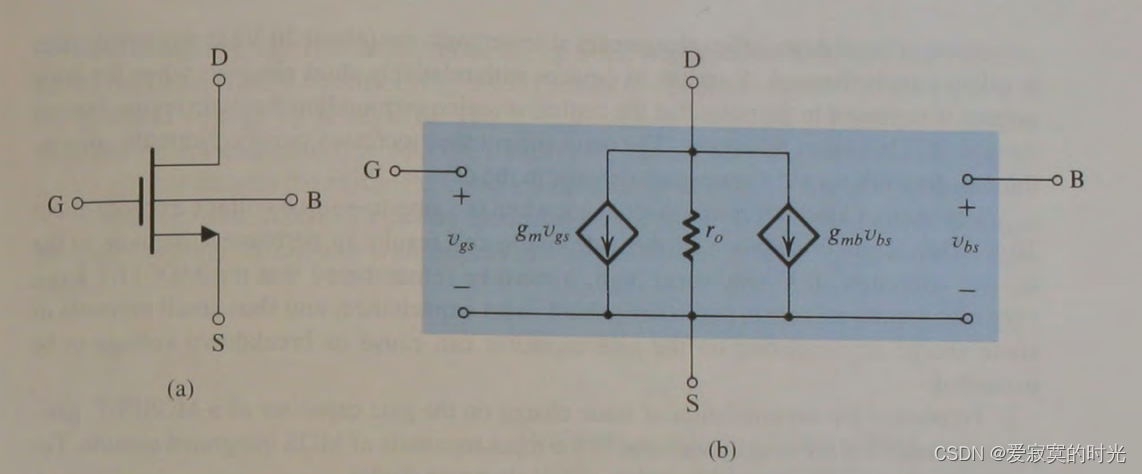

模型化体效应

在上面提到的将体极连接到电压源的情况下,在小信号模型分析中,体极作为一个AC地出现,这将会在体极和源极出产生电压 v b s v_{bs} vbs 。此时体极作为第二个栅极或是 背栅 出现在MOSFET中,因此信号 v b s v_{bs} vbs 同样出现在 i d i_d id 的表达式中作为一个分量出现。我们将此分量写作 g m b v b s g_{mb}v_{bs} gmbvbs 这里 g m b g_{mb} gmb 是 体极互导系数 定义为:

g m b ≡ ∂ i D ∂ v B S ∣ v G S = c o n s t , v D S = c o n s t g_{mb} \equiv \frac{\partial i_D}{\partial v_{BS}} |_{v_{GS} = const,v_{DS}=const} gmb≡∂vBS∂iD∣vGS=const,vDS=const

回想一下, i D i_D iD 通过 V t V_t Vt 和 V B S V_{BS} VBS 依赖于 v B S v_{BS} vBS ,也就是 g m g_m gm 取决于DC偏置, g m b g_{mb} gmb 依然取决于DC偏置,因此 g m g_m gm 和 g m b g_{mb} gmb 存在比例关系,这给出:

g m b = χ g m g_{mb} = \chi g_m gmb=χgm

这里:

χ ≡ ∂ V t ∂ V S B = γ 2 2 ϕ f + V S B \chi \equiv \frac{\partial V_t}{\partial V_{SB}} = \frac{\gamma}{2\sqrt{2\phi_f+V_{SB}}} χ≡∂VSB∂Vt=22ϕf+VSBγ

系数 χ \chi χ 在0.1到0.3左右。

上图给出了体效应的小信号模型,用于计算当体极不和源极相连的情况。然而在一些简单原型设计和分析中,体效应往往可以被忽略。

最后,尽管我们是在NMOS上分析的体效应,关于PMOS只需要将所有的电压量取负即可,分析方法一致。

温度效应

V t V_t Vt 和 k ′ k' k′ 都是对温度敏感的。大概每上升一摄氏度, V t V_t Vt 就会下降 2mv,会导致漏极电流增加。然而, k ′ k' k′ 才是温度效应中的主导参数,温度上升最终会引起的是漏极电流的减弱。这个特性使得MOS自带温度负反馈条件,因此在功率电源设计领域MOS十分受欢迎。

熔断和输入保护

当漏极电压增加到一定程度,可能会导致漏极和底物之间的pn结产生雪崩熔断,这个电压通常在20V到150V左右(弱雪崩),会导致漏极电流迅速增加。

另外一种熔断发生在低电压(20V)条件,称为 沟道穿通效应 。这发生在漏极电压增大,使得耗散区包围了源极和漏极区域,相当于直接将源极和漏极短路,漏极电流迅速增加。通常情况下,这个效应不会损坏MOS管。

还存在一种熔断,当栅极-源极电压超过30V的时候,这会造成栅极氧化物层被击穿。尽管30V看起来没那么大,但是必须考虑到MOSFET的栅极有相当高的阻抗,并且也存在一个极小的输入电容,当一些电荷聚集在栅极电容上的时候,MOS管的栅极氧化物层就会非常容易被击穿。

现在的MOS制作工艺都会在栅极引入保护电路以避免栅极氧化物层被静电击穿。通常由钳位二极管实现。

速度饱和

在一个纵向高电压电场中,载流子电荷的漂移速度有一个上限(大约在 1 0 7 c m / s 10^7 cm/s 107cm/s 对于电子和空穴在硅晶体中)。这个效应,通常发生在极小尺寸的MOS中,当 v D S v_{DS} vDS 低于1V的时候就可能发生,当速度饱和的时候,电流 i D i_D iD 就不再和 v G S v_{GS} vGS 是二次的关系了。而是, i D i_D iD 和 v G S v_{GS} vGS 成线性的关系,互导系数 g m g_m gm 变成常数和 V G S V_{GS} VGS 无关。

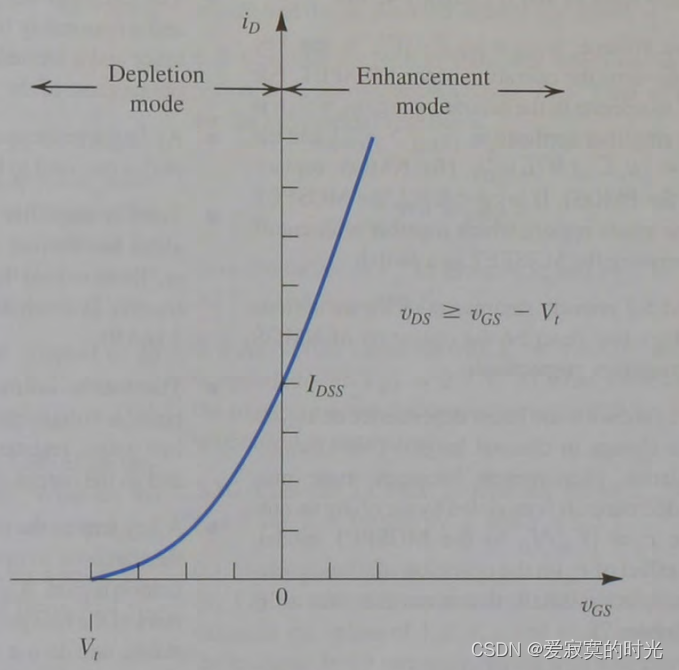

耗散型MOSFET

另外除了增强型MOSFET还存在一种耗散型MOSFET,结构和增强型MOSFET大致相似,只不过一点不同:耗散型MOSFET有一个提前物理注入的沟道。换句话说,耗散型NMOS本身在源极和漏极直接存在一个n类型的沟道。当 v G S = 0 v_{GS} = 0 vGS=0 的时候,沟道已经存在,因此源极和漏极之间可以导通,和增强型MOSFET不同,不需要手动创建沟道。

沟道的深度同样受到 v G S v_{GS} vGS 控制。增大 v G S v_{GS} vGS 同样会增加沟道的深度。但是我们可以在栅极加一个负电压 v G S v_{GS} vGS 来减小沟道的深度,这个负电压 耗散 了沟道中的载流子密度,这个负电压 v G S v_{GS} vGS 的工作区域称为 耗散区 。存在一个负数的阈值电压,使得当 v G S v_{GS} vGS 减小到阈值电压一下的的时候, i D = 0 i_D=0 iD=0 ,此时进入截止区。对于耗散型MOSFET的CV曲线,相当于将增强型MOSFET的CV曲线向左平移,如下图:

最终和增强型MOSFET,随着 v G S v_{GS} vGS 的继续增大,会变成一条水平的直线。

增强型MOS和耗散型MOS可以被制作在同一个芯片中,用来改善元器件的性能。

文章介绍了MOS管的体效应,包括底物的作用和体效应如何影响器件的阈值电压。在集成电路中,底物的电压控制着MOS管的导通状态,体效应参数γ和体极互导系数gm_b参与了电流i_D的调节。此外,文章还讨论了温度对阈值电压的影响,MOSFET的熔断机制以及速度饱和现象。最后提到了耗散型MOSFET,其在栅极电压为0时即存在沟道,可以通过负电压控制沟道的深度。

文章介绍了MOS管的体效应,包括底物的作用和体效应如何影响器件的阈值电压。在集成电路中,底物的电压控制着MOS管的导通状态,体效应参数γ和体极互导系数gm_b参与了电流i_D的调节。此外,文章还讨论了温度对阈值电压的影响,MOSFET的熔断机制以及速度饱和现象。最后提到了耗散型MOSFET,其在栅极电压为0时即存在沟道,可以通过负电压控制沟道的深度。

9025

9025

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?