亚阈值效应

import math # 导入数学库

# 定义公式中的参数

I0 = 1.0 # I0是一个常数,表示当VGS=0时的漏电流

VT = 0.026 # VT是热电压(thermal voltage),约为25mV在常温下

n = 1.5 # n是一个常数,被称为取决于器件的因子

VGS = 0.5 # VGS是栅极-源极电压(gate-source voltage)

# 使用公式计算ID

ID = I0 * math.exp(VGS / (VT * n))

print(ID)

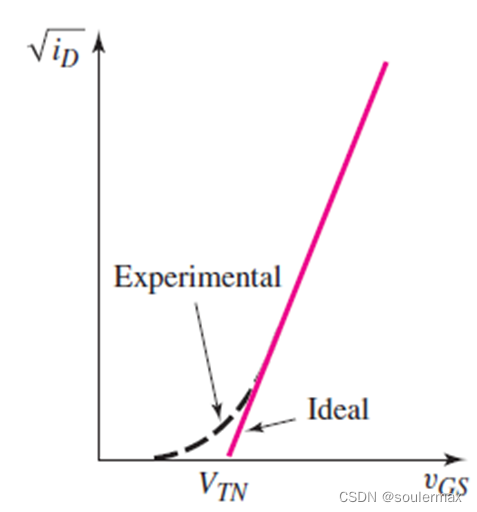

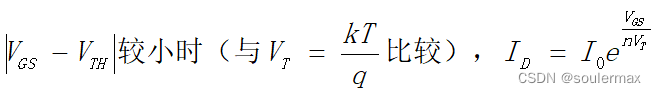

亚阈值效应是指在场效应晶体管(如MOSFET)中,**当栅极-源极电压低于阈值电压时,晶体管仍然会有一定程度的导通。**在这种情况下,晶体管的导通特性与传统的阈值以上的工作状态有所不同。

亚阈值效应对于低功耗电路设计和低电压操作至关重要,因为它允许晶体管在非常低的电压下工作。然而,这种效应也可能会导致一些设计上的挑战,因为它可能会引入不确定性和非线性。

在数字电路中,亚阈值效应可能会导致逻辑门的非线性响应,从而影响电路的稳定性和延迟特性。在模拟电路中,亚阈值效应可能会引起偏置电流的变化,从而影响放大器的增益和偏置点。

因此,在集成电路设计中,工程师们需要考虑和管理亚阈值效应,以确保电路在低电压和低功耗条件下仍能够可靠地工作。

I0:泄露电流常数

I_0 是晶体管在弱反转(亚阈值)区域工作时的电流参数,即当栅极电压 V_gs 小于阈值电压 V_th 时晶体管沟道的漏电流。这个漏电流被称为亚阈值漏电流(Subthreshold Leakage Current),在 V_gs = 0 时的值用 I_0 来表示。尽管此时栅极电压没有达到打开晶体管的阈值,但由于热活化等效应,部分电荷载流子仍然能够在源极和漏极之间形成一个微弱的电流。

I_0 是亚阈值模型中的一个关键参数,通常取决于以下因素:

晶体管的制造工艺

晶体管的几何尺寸

掺杂浓度

温度等影响

在实际电路运作中,人们通常期望 I_0 尽可能地小,以减少在非活动状态下的功耗,这在低功耗电子设计中非常关键。然而,I_0 的确切值会根据具体的晶体管设计和运行环境而变化。

亚阈值斜率因子(n)

n是一个非常重要的参数,它影响晶体管在亚阈值区间中电流相对于栅极电压的变化率。亚阈值斜率因子通常受以下因素影响:

晶体管的体效应(Body Effect):体效应导致阈值电压随着体电位(对应晶体管的衬底电压)的变化而变化。当体电位升高时,会导致阈值电压增加,这样亚阈值斜率因子n也会增加,因为需要更高的栅极电压来达到相同的电流水平。所以体效应和亚阈值斜率因子是正相关的。

衬底掺杂浓度(Substrate Doping Concentration):高掺杂浓度可以增大阈值电压,随之亚阈值斜率因子也会增大。衬底掺杂浓度与亚阈值斜率因子正相关。

氧化层电容(Oxide Capacitance):氧化层电容对亚阈值斜率因子的影响是反相关。氧化层电容更大会导致亚阈值斜率因子n减小,因为栅极电场对晶体管沟道的控制能力增强,电流可以在更低的栅极电压下产生。反过来,氧化层电容更小导致n值增加。

温度:温度升高时,亚阈值斜率因子通常会增加,其效应可以用下面的关系描述:

n = 1 + C_dep / C_ox

其中 C_dep 是耗尽区电容,C_ox 是氧化层电容。温度升高会导致耗尽区宽度变化,进而影响 C_dep。所以温度与亚阈值斜率因子是复杂相关,取决于 C_dep 和 C_ox 的相对改变。

亚阈值斜率因子n的大小很重要,因为它决定了晶体管在低电压操作时的负载和功耗性能。设计时需要仔细把握这些因素,以优化晶体管的功耗和速度。

本文详细探讨了MOSFET的亚阈值效应,包括泄露电流常数I0和亚阈值斜率因子n,以及沟道调制效应和体效应。此外,还介绍了体效应系数γ和沟道长度调制系数λ,以及温度对NMOS阈值电压和迁移率的影响。这些参数在低功耗设计和集成电路性能优化中至关重要。

本文详细探讨了MOSFET的亚阈值效应,包括泄露电流常数I0和亚阈值斜率因子n,以及沟道调制效应和体效应。此外,还介绍了体效应系数γ和沟道长度调制系数λ,以及温度对NMOS阈值电压和迁移率的影响。这些参数在低功耗设计和集成电路性能优化中至关重要。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1015

1015

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?