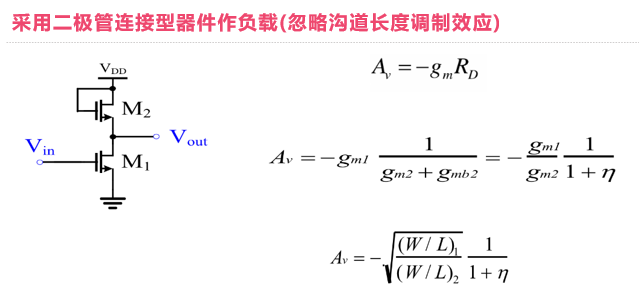

其中 =

= , 由于NMOS的Vbs随输出电压Vout的变化而变化 , 导致了增益的非线性变化

, 由于NMOS的Vbs随输出电压Vout的变化而变化 , 导致了增益的非线性变化

BUT , 我们可以利用PMOS管的在n阱中的隔离特性 , 即Vbs = 0 , 来消除衬偏效应的影响

由上式可得增益变为一个相对稳定的值 , 但这并不是"完美"的,高增益导致了(W/L)的不协调以及输出电压的摆幅 [具体原因详见<<模拟CMOS集成电路设计--- 拉扎维>>P52页有详细解释]

那么 , 为什么PMOS没有衬偏效应?

知乎作者其遇 - 知乎 (zhihu.com)已经做了回答 , 这里我直接搬运(侵权删)

原文链接:pmos为什么没有体效应? - 知乎 (zhihu.com)

首先体效应是因为衬底电压比源极电压更低之后导致沟道处的耗尽区宽度更宽从而导致阈值电压更高。如果说衬底的电压和源极的电压相同,那么就不存在体效应。

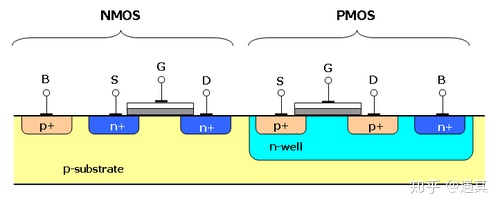

NMOS和PMOS的结构如下

现有的CMOS集成电路工艺中所有的NMOS是直接做到衬底上的(衬底为P掺杂),电路中不同位置NMOS因为连接的结构不同,所以源极的电压都不一样,这个时候就没办法把衬底跟所有的源极短接,那样就短路了是吧。

但是PMOS呢是需要先在衬底上做一块N阱,然后再做PMOS的结构,所以理论上每个PMOS的N阱都可以直接和每个PMOS的源极单独连接。因此PMOS可以做到消除体效应。

而在现在的一些工艺中,也有专门给NMOS添加一个深n well的做法(DNW)。如下图所示

一方面,使用这样的工艺之后,在保证DNW正确偏置时,NMOS的body可以与Source短接,从而消除其体效应,另一方面,增加DNW也可以阻断来自电路中其他MOS产生的噪声串扰。

所以综上所述,体效应的消除本质就是body和source短接,只不过对于PMOS和NMOS的实现手段不太一样罢了。

491

491

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?