一概述

设计锁相环(PLL)的IP核,并完成在ModelSim中的仿真测试。锁相环常用在调频和分/倍频设计中。

难点:在ModelSim中实现IP核的仿真。

二锁相环IP设计

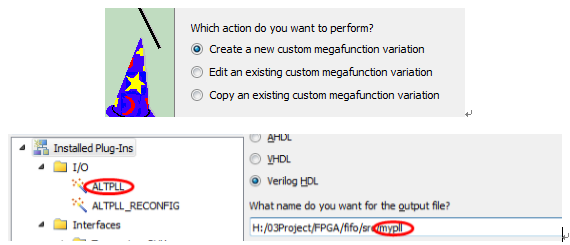

1 在Quartus -> Tools-> MegaWizard Plus-In Manager中创建IP核,选择I/O中的ALTPLL核,并输入文件名称后点“Next”。注意路径名不能有中文!

2 对锁相环进行常规设置

1为芯片的速度等级,如EP4CE15E22C8的速度等级为8。

2为输入的晶振频率,板上为50M晶振,则输入50。

3 其它配置选择默认,一直点Next,直到进入c0配置画面

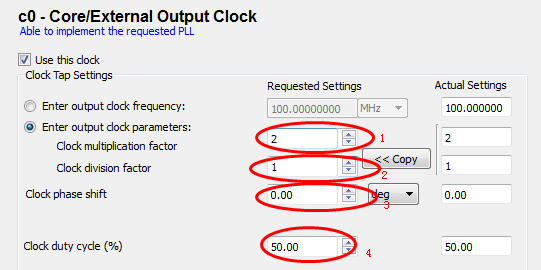

C0脚即为锁相环的输出,它可以倍频、分频和倍分频综合使用。

这里1为倍频系数,2为分频系数,3为相位差,4为占空比。

这里设c0为倍频,即2倍频,输出频率为100MHz。

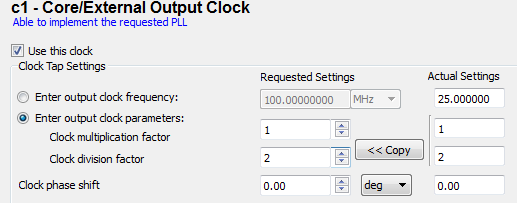

4 设置c1~c4输出

C0配置好后,点“Next”进入C1配置画面,选中“Use this clock”,并设置为分频,即2分频,25MHz。

同理c2设置相位差为90度,c3设置占空比为20,c4设置为混频。

5 生成源文件

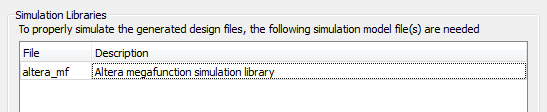

配置完c4脚后,点“Next”或“Finish”,则可看到仿真库文件。这个文件在ModelSim仿真中需要使用。

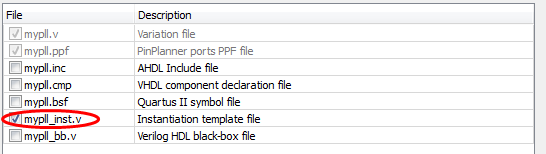

点击“Next”,点中_init.v文件。

选中“Finish”结束设计。

6 添加文件到工程中

设计结束后会自动弹出,点“Yes”

7 复制仿真库文件

将\altera\13.0\quartus\eda\sim_lib中的220model.v和altera_mf.v文件复制到工程目录。

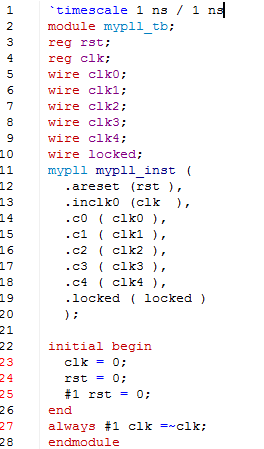

8 编写测试文件

打开myfifo_inst.v文件,另存为myfifo_tb.v,并改写成如下:

三ModelSim进行仿真

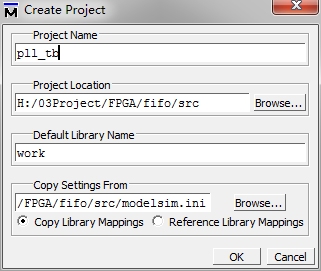

1 打开ModelSim,新建工程pll_tb。

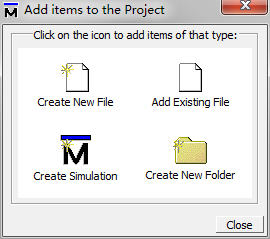

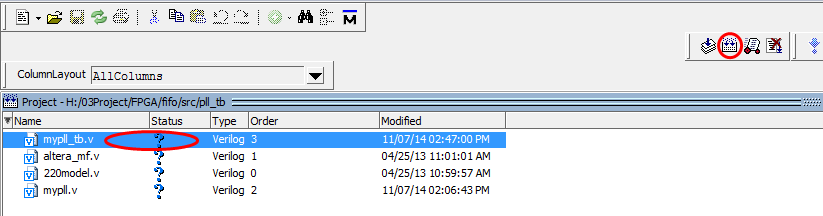

2 将目录下的4个文件添加到工程

3 选中其中一个文件,点编译

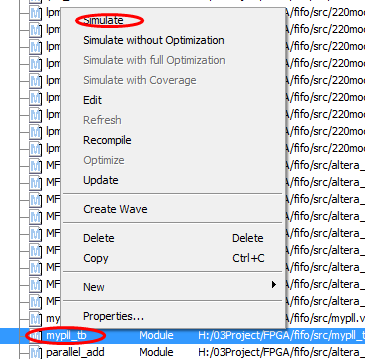

4 点“Library -> work”,找到mypll_tb.v,右键点击,选中仿真。

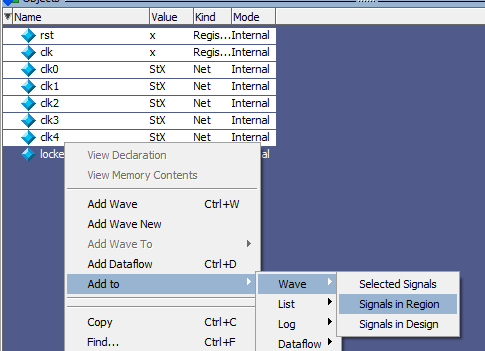

5 将要观察的数据添加到波形图中

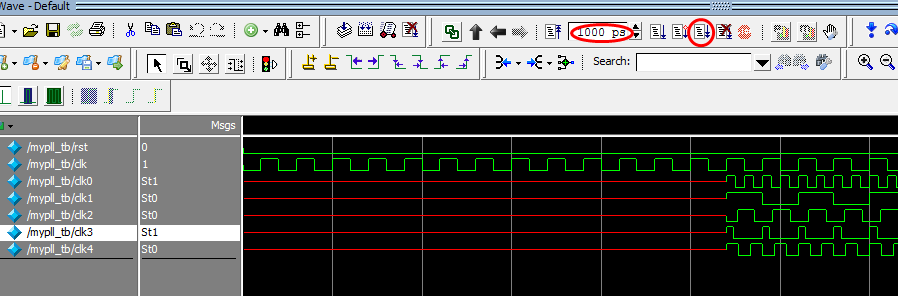

6 打开Wav窗口,点击运行。

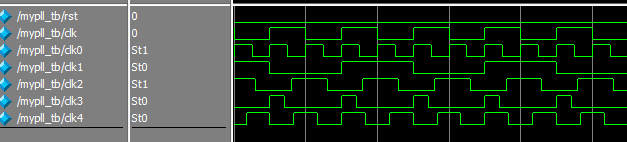

7 观察波形,发现与设计相符。

四总结

仿真的难点在于是基于IP核仿真,并且相关文档较少。调试时需注意:

1 PLL核需要一定的时钟周期进行初始化。

2 复位脚需设置成0。

3 仿真IP核时,需加入altera_mf.v和220model.v。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?