由于要对FPGA读写SDRAM的工程进行调试,第一步就是验证PLL模块的功能,故结合网上找的一些资料,进行了如下PLL仿真实验。

下面是仿真的全过程

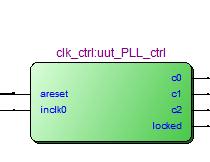

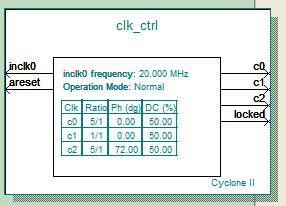

- 首先,看一下Quartus中的PLL模块:

从上面图中可以看出:我的FPGA输入时钟是20MHZ,该PLL有三个输出,其中

C0:5倍频,100MHZ

C1:1倍频,20MHZ

C2:5倍频,100MHZ,同时相对于C0延时2ns,也就是72度的相位差。

- 下面,新建一个Modelsim的工程。然后在工程目录下新建两个文件夹,分别为src以及modelsim,如图所示

本文介绍了如何使用ModelSim仿真FPGA中的PLL模块,以验证其5倍频和1倍频输出功能,并通过波形分析确认了相位差为2ns,从而完成PLL模块的功能验证。

本文介绍了如何使用ModelSim仿真FPGA中的PLL模块,以验证其5倍频和1倍频输出功能,并通过波形分析确认了相位差为2ns,从而完成PLL模块的功能验证。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1752

1752

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?