Quartus II 是一款综合性PLD/FPGA开发软件,原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware 支持Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器。如何进行仿真呢?

Quartus 中调用modelsim的流程:

一.设置仿真工具路径

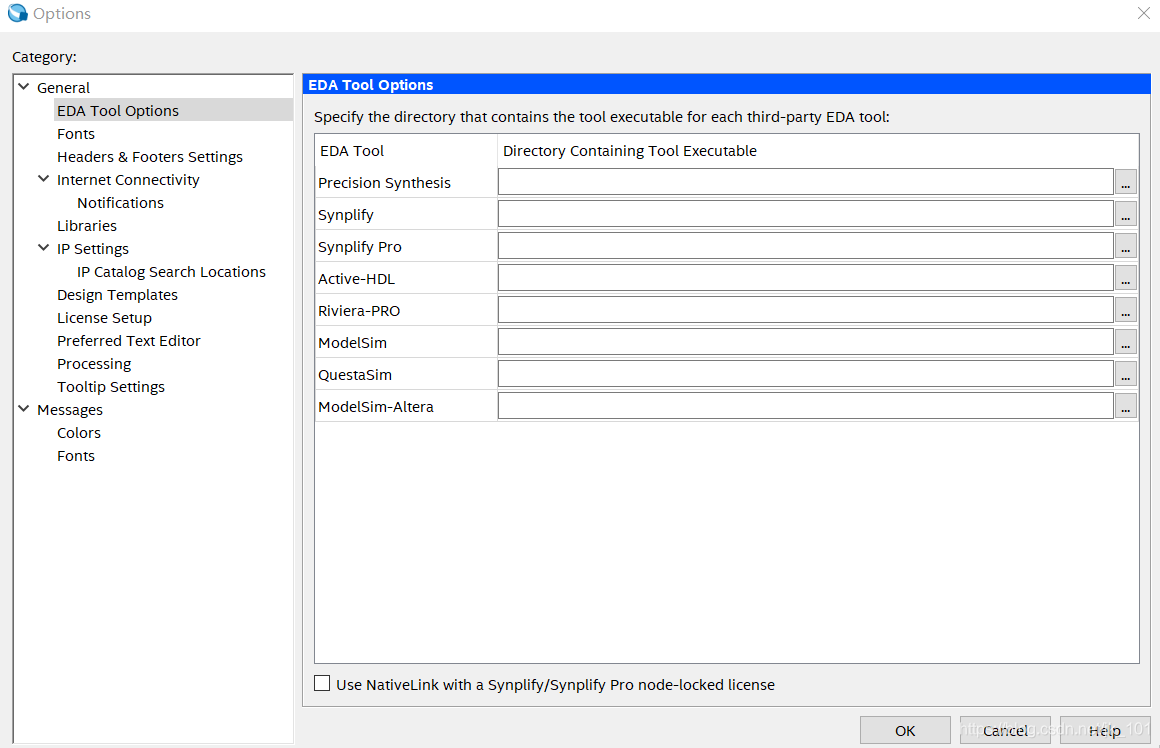

在进行仿真之前,需要进行仿真软件的路径设置,点击Tools->Options,打开界面,点击EDA Tool Options选项,如图所示:

出现了多种工具,一般我们进行仿真常用的两种是Modelsim和Modelsim-Altera,其中Modelsim需要我们安装其软件,而Modelsim-Altera是QuartusII软件内部自带的,用起来比较方便,我一般都会选择自带的(因人而异)。其中需要进行Modelsim-Altera的路径设置。

点击Modelsim-Altera一栏最右边的路径按钮,在弹出的界面中选择你安装QuartusII软件的位置,每个人安装的软件位置不一样,但是Modelsim-Altera的路径是一样的,即:

软件安装位置\modelsim\win32aloem

如图所示:

这样仿真软件的路径就设置好了,接着就可以做仿真了。

二.设置仿真工具

1.创建一个工程并完成工程文件之后,进行仿真文件的编写。一般仿真文件可以自己创建文件进行编写,也可以使用QuartusII软件自动生成仿真文件,在仿真文件里添加需要的仿真内容。

点击Processing -> Start -> Start Testbench Template Writer生成针对工程的Testbench模板文件。

接着使用File ->Open打开在工程的simulation目录下的Testbench文件工程名.vt。

最后在该模块中进行仿真内容的添加。

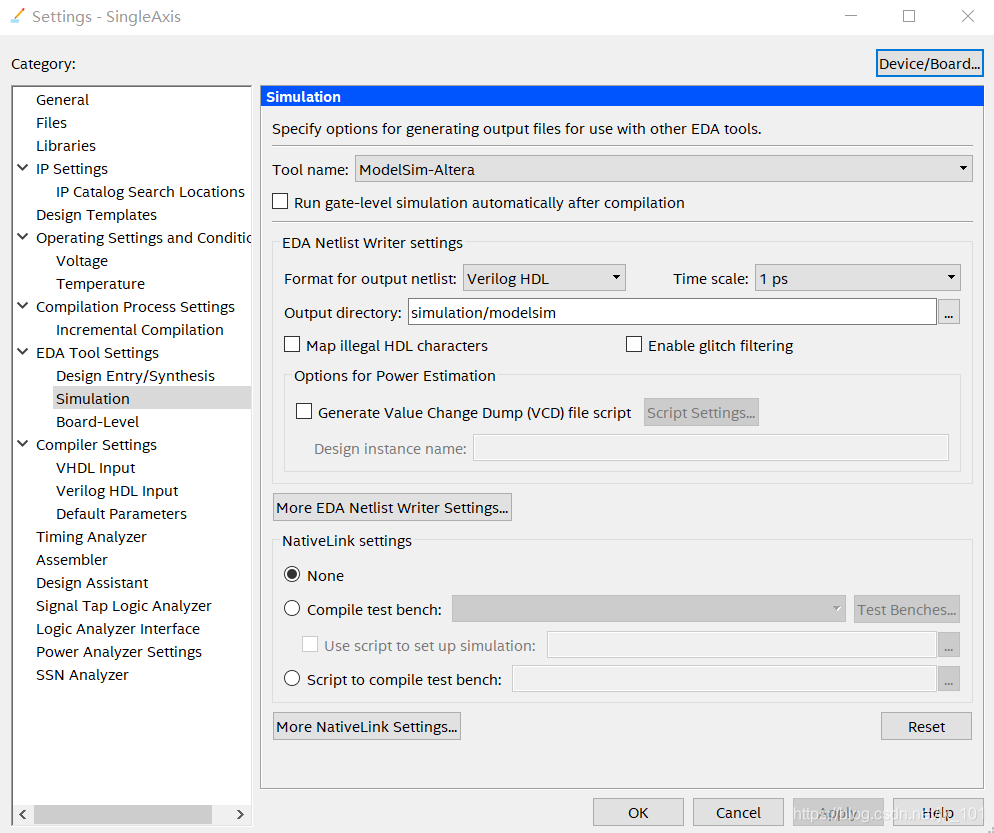

2.点击Assigments -> Settings -> EDA Tool Settings -> Simulation设置仿真参数,如图所示:

设置参数,Tool name选择Modelsim-Altera,也可以选择你自己熟悉的仿真工具;Format for output netlist一般选择Verilog HDL这个根据情况选定;Time scale根据你仿真文件中的设置而定;Output directory选择simulation/modelsim,其它的先不用设置。

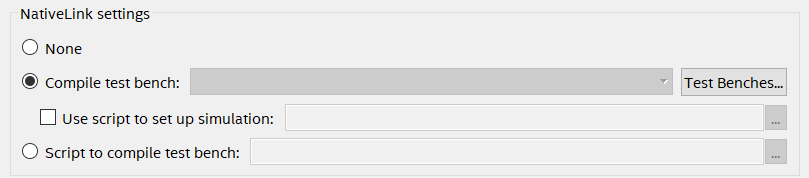

接着在NativeLink settings中选择Compile test bench选项,如图所示:

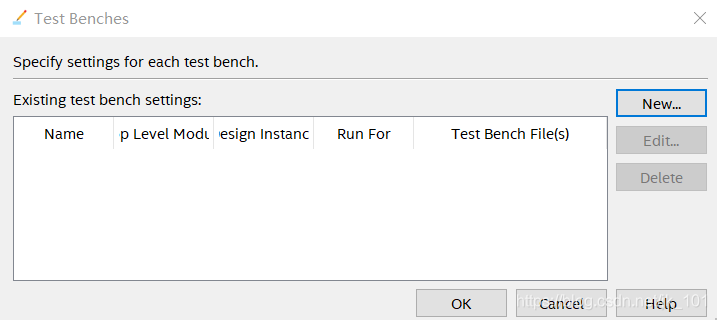

点击右边的Test Benches,弹出如图所示的Specify settings for each test bench对话框:

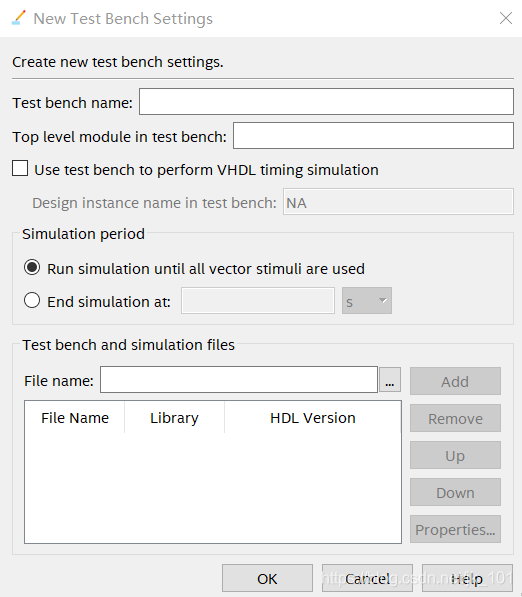

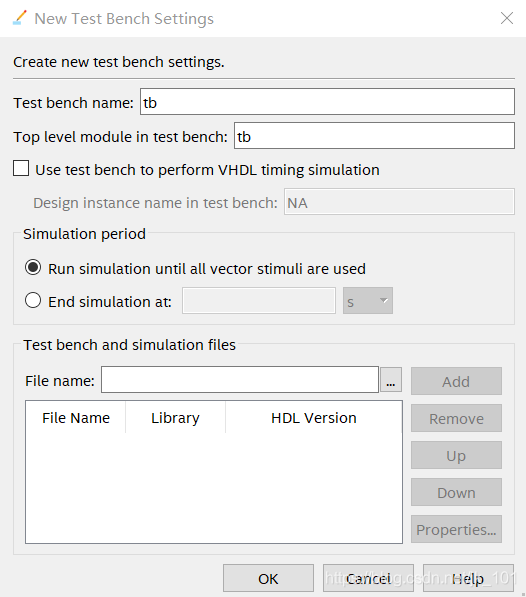

点击New选项,弹出Create new test bench settings对话框:

在Test bench name的对话框中输入一个名字”test_tb”, 我们将看到,在下面的Top level module in test bench对话框中也自动显示”test_tb”. 注意这个名字应该和你的test bench 中的module name一致,假如我们之前在编写的时候将test bench的module name已经改成了tb,所以我们这里应该把Top level module in test bench对话框中的名字改成tb。为了简单起见,我们最好在设置的时候将Test bench name和Top level module in test bench中的名字与我们之前编写的测试文件的模块名字取一样的,这样就不容易出现其他的错误。如图所示:

最后设置Test bench and simulation file(仿真文件),点击File name选项右边的按钮,在弹出的对话框中选择你的test bench仿真文件,点击OK。完成所有的仿真设置。

3.进行仿真任务

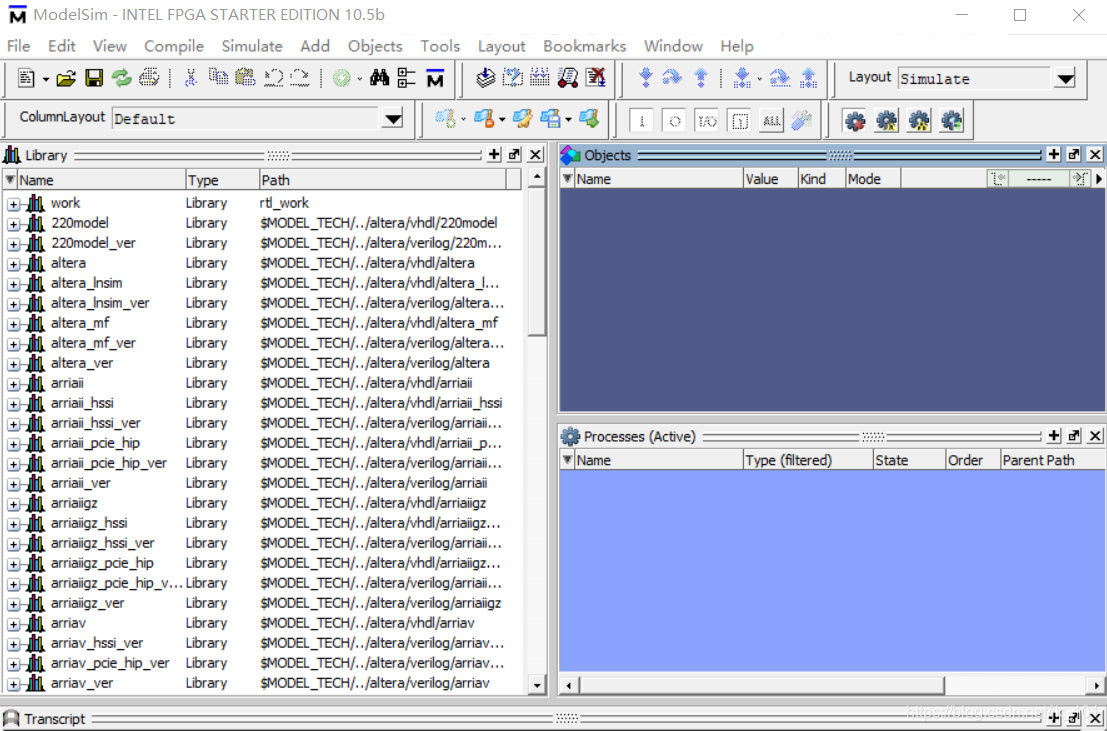

设置完以上步骤之后,点击Tools -> Run Simulation Tools -> RTL simulation则弹出Modelsim的仿真界面,自此就可以进行仿真分析了。

三.功能仿真和时序仿真

Quartus和Modelsim软件的仿真形式

- Quartus II有两种仿真形式:(1)功能仿真;(2)时序仿真。

- Quartus II调用Modelsim的两种仿真形式为:(1)RTL级仿真;(2)Gate-level仿真。

1.当在QuartusII中调用Modelsim-Altera进行RTL仿真时(前提是在第三方仿真工具中选择Modelsim-Altera),步骤如下:

(1)编写源文件和测试文件;

(2)Assignment->setting->EAD Tool Settings->simulation(不选中run gate leve simulation)。选中nativelink,添加测试文件,填写测试文件模块名,重复上述的仿真过程即可;

(3)start analysis&elabration;

(4)Tools->start RTL simulation;

2.当在QuartusII中调用Modelsim-Altera进行Gate-level仿真时(前提是在第三方仿真工具中选择Modelsim-Altera),步骤如下:

(1)编写源文件和测试文件;

(2)Assignment->setting->EAD Tool Settings->simulation->run gate leve simulation。选中nativelink,添加测试文件,填写测试文件模块名,重复上述的仿真过程即可;

(3)进行工程全编译;

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?