在平时工作中,经常会听到哪个FPGA或者某个芯片包含了几百万门,每次听到这种数字,很多FPGA工程师都会一愣一愣的,因为大家工作中,说的逻辑资源数量,一般是指CLB或者Slice的个数,没人会特指有多少逻辑门。而且现在的LUT都是4输入或者6输入,可以做成逻辑门的组合,跟普通的逻辑门个数肯定不会是一对一关系。今天我们来看下这个关系如果对应。

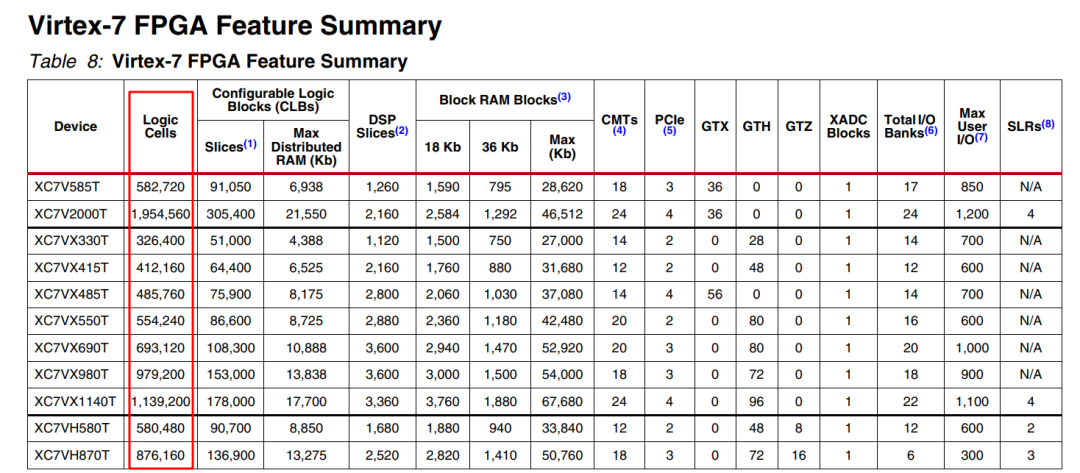

在查资源时,看到一个词-- logic cell,平时没太注意到,但器件手册中都会提到。

image-20221031201440575

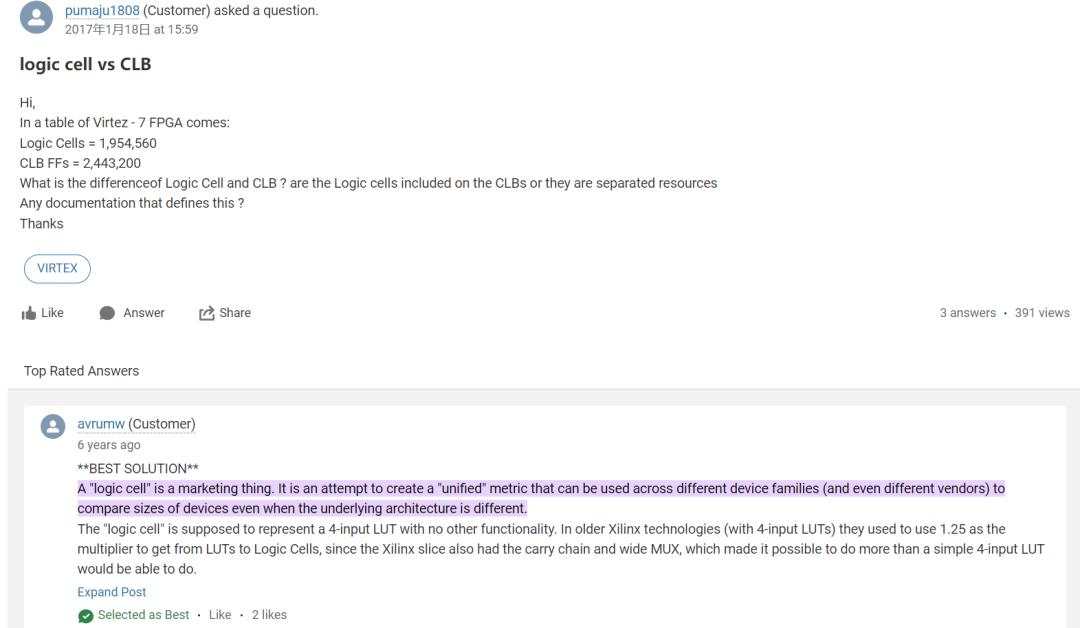

来看下官方的解释:

image-20221031201151101

在7系列的手册中,也可以看到:

The ratio between the number of logic cells and 6-input LUTs is 1.6:1

也就是说,对于7系列包含的6输入LUT来说,一个LUT等效于1.6个logic cell。

所以上面第一个图中,logic cell的个数与slice的个数比是6.4:1,因为一个Slice里面包含4个LUT,而一个LUT等效于1.6个logic cell,因此1.6*4 = 6.4.

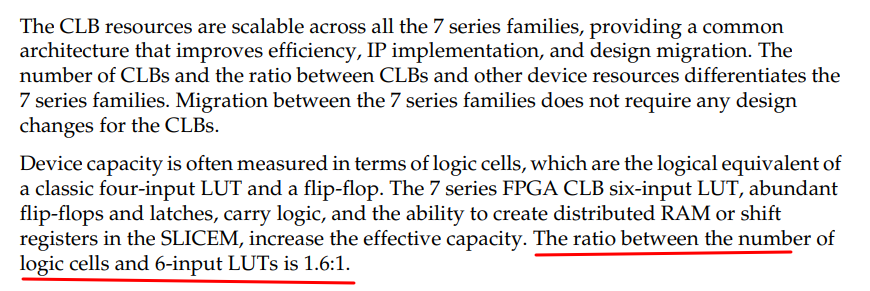

在xilinx的另一个手册中,提到一个Logic Cell大致等效于15个ASIC Gate,当然这种等效关系并不是很准确的,我们只能做个参考。

image-20221031203104770

所以,以XC7VX690T为例,有693120个Logic Cell,对应的ASIC Gate的个数为:693120*15=10,396,800,也就是一千万逻辑门。

756

756

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?