我讨论了为 2 层 PCB 准备布线规则以支持数字信号布线和布局的一些基本要点。特别是,我们研究了在 2 层 PCB 上支持 I2C 或 SPI 等数字接口所需的一些基本堆叠和布线规则。使用这些接口时,一些简单的指导原则可以帮助确保电路板中的信号完整性并减少 EMI。

那么像 USB 这样的阻抗控制接口呢?阻抗控制的必要性以及知道何时会违反阻抗控制是将 USB 等接口布线在 2 层 PCB 上的要点。在本文中,我将展示如何布线 USB 等高速协议。具体来说,我们将研究布线电路板所需的重要设计规则,特别是我们可以接受的用于承载 USB 数据的走线的长度限制。如果您尚未阅读本系列的上一篇文章,请阅读一下,因为它奠定了一些概念基础,有助于您理解 USB 布线要求的限制。

入门:USB 高速路由要求

在上一篇关于 2 层 PCB 布线的文章中,我们研究了一种无需应用阻抗匹配即可确定设计中可使用的最长线路长度的程序。我们发现长度限制取决于传输线长度上您可以容忍的输入阻抗偏差水平。具体来说,取决于您是否将信号传输距离的 10% 到 25% 视为限制走线长度的重要因素。

对于此演示,我想看看此板上在高速标准下的 USB 2.0 路由,我出于特定原因专注于此标准。USB 2.0(高速)仍在某些系统中使用,因为它提供与旧设备的连接以及快速的数据传输速率,并且仍在使用 B 型插头的 Arduino 等流行平台上使用。

为了说明两种可能的设计,我比较了两种 USB 2.0 规格(全速和高速)的数据速率和上升时间:

| 最小驱动器上升/下降时间 | - 500 ps(高速) - 4 - 20 纳秒(全速) |

| 最大差分对偏差 | - 100 ps(高速) - 1 至 5 纳秒(全速) |

| 阻抗目标 | - 90 欧姆差分 |

下面我将展示的过程是针对具有高速上升时间和偏移的 USB 2.0 信号进行的,但您可以将相同的过程应用于 USB 3.0 或任何其他高速接口。请记住:在 2 层板上布线并不适合每个接口。例如,我不知道有谁会建议在 2 层板上布线 DDR4,因为这些快速信号的长度限制很小,而且会产生辐射噪声。

临界长度

首先,我们想知道在典型的 2 层 PCB 上路由 USB 信号的临界长度。对于 Dk = 4.8 的FR4 材料芯,我们将获得大约 150 ps/英寸或大约 6 英寸/ns 的传播延迟。对于高速规格的 500 ps 上升时间,这在上升时间内给出了 3 英寸的信号传播距离。如果我们非常保守并对临界长度使用 10% 的限制,这将给出 0.3 英寸的临界长度!

我们在这里需要布线的拓扑只是带有差分对的串行线。因此,您有三个元素:

- 驱动程序组件,或者带有 USB 接口的处理器

- 终端电阻(请参阅下面相关部分)

- 固定 USB 电缆的连接器

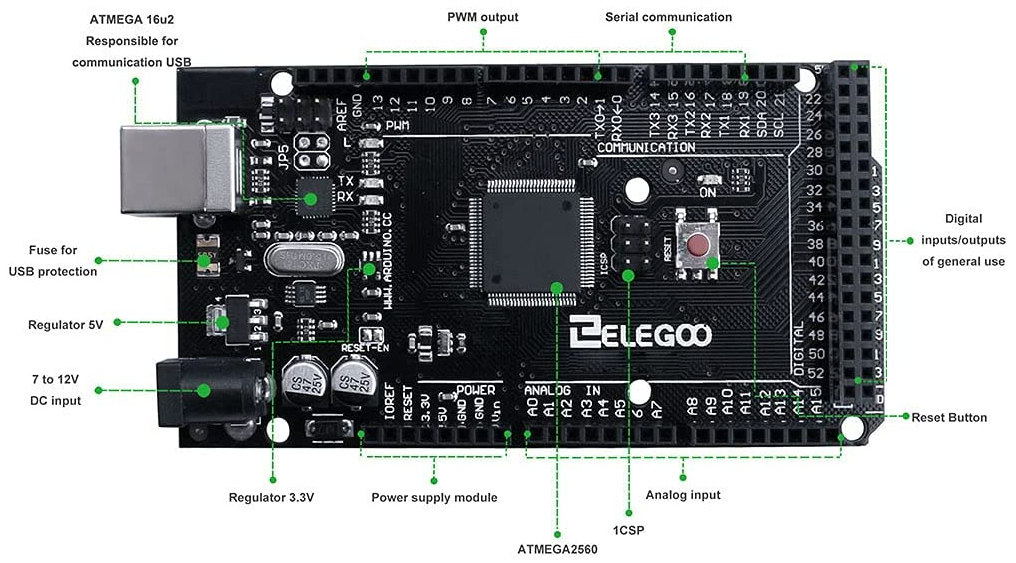

您可能想知道,在 Arduino 这样的平台上如何做到这一点?请看下面的 Arduino Mega 图片,您可以在亚马逊上购买。USB 控制器放置在靠近连接器的位置,并且绝对在 1 英寸以内。

Arduino Mega 示例板。请注意,USB 控制器芯片靠近 B 型连接器。

您会在其他 Arduino 板上发现类似的布局和布线。为了避免连接器、电缆和接收器的输入阻抗不匹配,我们希望遵循上述建议,并在我们的 2 层 PCB 上保持较短的布线。但是,我们不需要如此保守地应用 10% 的限制。相反,如果我们采用 25% 的限制,我们将获得更舒适的 0.75 英寸布线距离,这在 2 层 PCB 上更易于管理。

请注意,这是针对高速规格的。在全速规格下,对于 4 纳秒的上升时间,我们有更宽松的 2.4 英寸临界长度(10% 限制)或 6 英寸临界长度(25% 限制)。

需要注意的一点是:没有设定有效临界长度的限制(10%、25% 或其他),并且根据 PCB 的尺寸,您可能超出临界长度,现在需要设计正确的阻抗。限制取决于几个因素,确定临界长度的正确百分比需要计算多个阻抗值。与根据此临界长度制定规则相比,设计所需的 USB 阻抗总是更容易。

终端电阻

接下来,我们需要考虑如何终止驱动器输出。由于我们在这里专门讨论 USB,请注意 USB 2.0 规范要求在连接器附近的 D+ 和 D- 线上使用一些终端电阻来匹配阻抗。这些电阻可能集成到芯片上的 USB 收发器中,也可能作为外部组件需要。典型值为 15 欧姆、22 欧姆或 45 欧姆,尽管也可能使用其他值;请务必检查您的组件的数据表以了解需要什么终端。例如,TUSB2077APTR USB 集线器控制器使用 27 欧姆终端电阻。请务必检查数据表以检查是否需要这些外部电阻。

差分倾斜

高速标准中偏差限制为 100 ps,现在我们可以计算差分对两侧(D+ 和 D- 信号)之间允许的长度不匹配。取表面层布线的近似 6 ns/英寸传播延迟估计值,乘以偏差限制,我们得到 0.6 英寸(600 mil)的走线长度差异。这个差异非常大!我们可以自由地进行一定程度的走线长度匹配。但是,这里有一个重点:这包括互连的整个长度(电路板 + 电缆 + 接收电路板)。因此,为了安全起见,请尽最大努力通过将差分对布线在一起并在可能的情况下强制进行一定程度的长度匹配来尽可能地限制偏差。这非常容易,因为 USB 控制器芯片通常会将 D+ 和 D- 信号放在芯片的同一边缘。

当长度差异较小时,您可能不需要实施长度调整,因为它会占用 PCB 布局中的空间。只需查看其他功能系统会做什么,请查看下面显示的 Arduino UNO PCB 布局图像(注意:这是从 Eagle 文件转换而来的)。USB 线已在图像中突出显示。如果我们测量这些线的正极和负极的长度(跨越终端电阻的每一侧),我们会发现长度差异约为 180 mil。这就是为什么这些线在 Arduino 和 USB 连接器之间长度不匹配的原因。

在这个狭小的空间里,接口仍能正常工作,因为长度差异只有大约 180 密耳,这比偏差容差小得多。即使在最坏情况下纤维编织对松散玻璃编织层压板产生影响,总偏差(就长度而言)也只相当于小于大约 230 密耳,仍然比此接口的偏差容差小得多。

您的布线风格:耦合差分对或共面差分微带

正如我在上一篇博客中指出的那样,您不能使用与高速 USB 2.0 中的特性阻抗相对应的走线宽度,同时仍满足阻抗规格。请记住,标准厚度两层 PCB 上的走线宽度在 Dk - 4.8 下约为 110 mil。我们如何才能使用该走线宽度达到 USB 2.0 高速中的差分对阻抗规格?

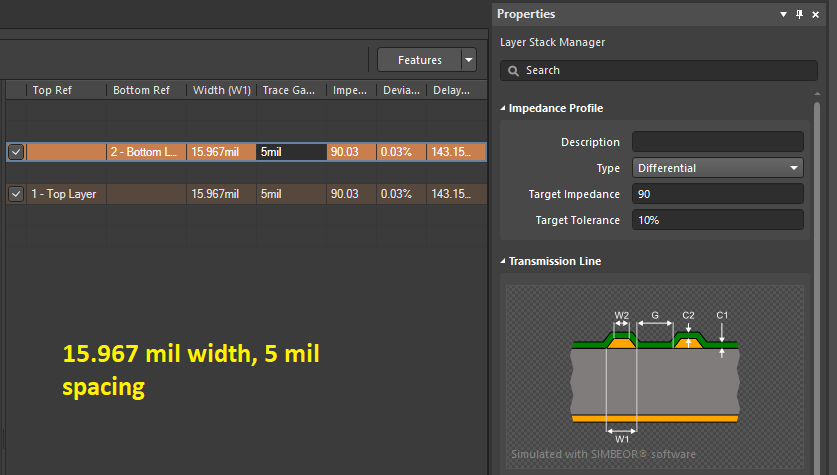

实际上,由于差分对中的走线会相互耦合,因此我们不需要使用该走线宽度。如果您使用带有厚 2 层电路板的层堆栈计算器来计算微带线的差分阻抗,您会发现实际所需的走线宽度要小得多,并且是间距的函数。对于 2 层 PCB 上的示例微带线,Altium Designer 中的层堆栈管理器告诉我们,对于 5 mil 间距,走线宽度约为 16 mil。

Altium Designer 的层堆栈管理器中的差分微带阻抗结果。

您可以使用更细的迹线与这些差分微带线,但您需要使用更小的间距。在此设计中,我们接近蚀刻的迹线到迹线间隙的极限,因此保持迹线之间的 5 mil 间隙是可以的,因为我们使用这些迹线宽度满足单端规格和差分规格。我们如何知道我们满足了规格的单端部分?这是因为:上面给出的迹线宽度是针对单个迹线的奇模阻抗,而不是特征阻抗!这就是为什么您需要坚持使用这个特定的迹线宽度值,而不是单独使用单个微带线的特征阻抗值。

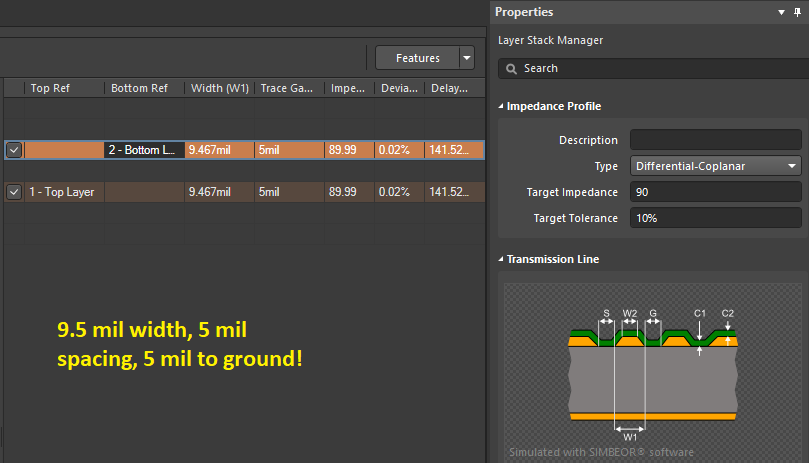

还有一个我们没有讨论的替代方案:使用共面微带差分对。通过将接地灌注线铺设到表面层的微带,并将接地灌注线放置在底层信号下方,您可以实现 90 欧姆差分阻抗,且迹线宽度为 9.5 mil,迹线间隙为 5 mil,接地间距为 5 mil。从下面的值可以看出,使用这些值,我们可以很好地达到 USB 2.0 规范中所需的 90 欧姆阻抗。

共面差分阻抗导致 Altium Designer 的层堆栈管理器。

通过这种安排,我们不必太担心 2 层电路板中的关键长度问题和走线宽度问题。但是,您需要注意,必须在整个布线长度上保持此宽度和间距。USB 布线将走线视为单独的单端走线,这些走线恰好承载差分信号,因此您可以单独布线它们。

PCB 布局内部

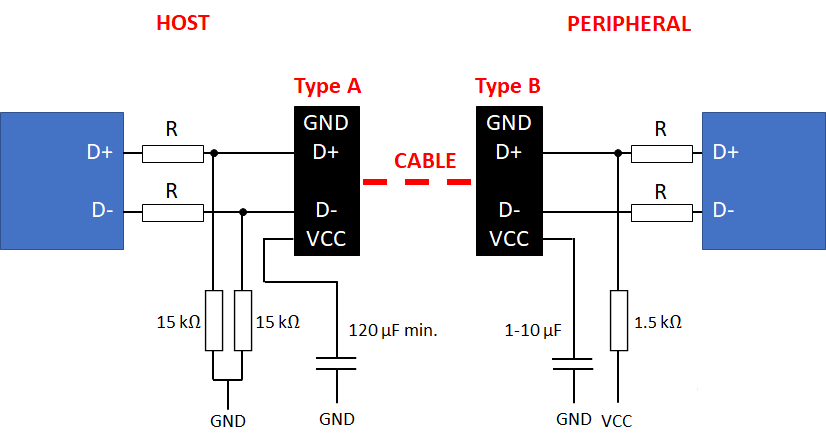

布线拓扑非常简单:从 USB 芯片布线到终端/上拉/下拉电阻,然后布线到连接器,全部作为差分对。下图显示了带有上拉和下拉电阻的高级布线拓扑。USB 2.0 标准下还需要一些电容器,如下所示。

全速和高速 USB 2.0 路由的路由拓扑。

布线相当简单:遵守系统各部分之间的标准差分对布线实践,您就不会遇到信号注册或阻抗匹配问题。保持短路线,从差分对线路直接连接,以便为下拉电阻和上拉电阻连接到 GND/VCC。请务必在数据表中检查设备的应用电路,因为 D+/D- 线路上可能有额外的外部电容器;您会在我上面提到的 TUSB2077A 设备上看到这一点。

我们将在即将发布的博客中展示 PCB 布局中的真实示例。现在,请亲自尝试一下,看看是否可以完成设计布线。

概括

在这篇博文和我们之前的博文中,我们介绍了在 2 层 PCB 上设置和布线 USB 等高速接口时应遵循的一些重要布线规则。以下是我们最终的布线指南:

- 如果您无法使用差分阻抗计算器,或者您不知道如何计算,那么只需将走线长度保持在 0.75 英寸以下,而无需进行阻抗控制

- 将差分对长度不匹配保持在 0.6 英寸以内 - 这很容易做到

- 如果您可以使用差分阻抗计算器,则使用差分微带或共面差分微带(均具有受控阻抗),并按照 90 欧姆差分阻抗规格进行设计

这里显示的布线指南并不总能保证 EMC,设计中还需要考虑其他方面,而这些方面有时在 2 层 PCB 中做得很差。但是,如果您使用全速规格,这些指南肯定会对 EMI 有所帮助。我个人倾向于使用 4 层 PCB 来处理串行数字总线和高速协议,特别是如果电路板较大或要批量生产时。

如果您使用的是 USB 3.0,那么由于边缘速率较快,您对长度匹配的要求就很严格,并且您应该将接口放置在靠近连接器的位置,就像我们对上面列出的全速规范所做的那样。

3615

3615

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?