英特尔 Stratix 10 FPGA 编程

随着微控制器的日益普及,工程师们越来越多地使用微控制器而不是 FPGA。微控制器因其成本低廉、支持良好、易于可用性、大型社区、多功能性、编程等优点而成为 FPGA 的主导地位。但除此之外,微处理器还有一些限制,例如指令集、程序的顺序执行(顺序处理)、缺乏灵活性和可重用性等。然而,FPGA可以克服这些限制,因为FPGA可以并行执行程序,而且它灵活且可重复使用,这意味着它可以一次又一次地为不同的任务重新编程。

什么是 FPGA 以及它与微控制器有何不同

现场可编程门阵列是一种集成电路硅芯片,具有逻辑门阵列,该阵列可以在现场编程,即用户可以用其新定义的配置覆盖现有配置,并可以在现场创建自己的数字电路。FPGA 可以被视为空白板。FPGA 本身不执行任何操作,而由 设计人员为 FPGA 创建一个通常称为 bit 文件的配置文件。一旦加载了 bit 文件, FPGA 将表现得像 digital circuit。

而在微控制器中,情况并非如此,因为微控制器无法在现场编程或重组。用户既不能覆盖其现有配置,也不能在现场创建任何数字电路。微控制器易于编程,社区也很广泛。微控制器是定制的微型计算机,以 IC 形式出现,而 FPGA 仅包含可以再次重新电气连接的逻辑块。此外,在微控制器方面,它比 FPGA 消耗更少的功率。众所周知,FPGA 成本高昂,在构建任何设备时,它需要的成本比微控制器高。FPGA 的设置时间要长得多,而微控制器则很容易为特定应用构建。

FPGA 架构

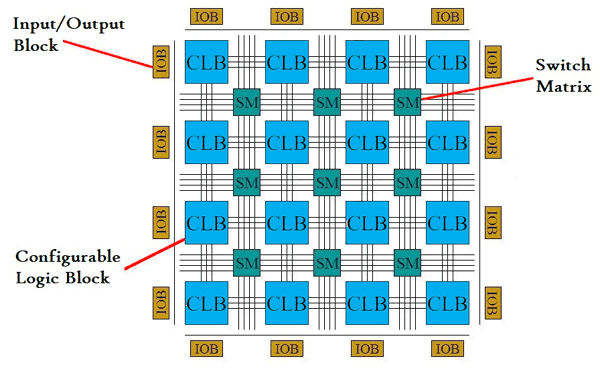

FPGA 具有逻辑单元或模块和互连的规则结构,由开发人员和设计人员完全控制。FPGA 主要由三个主要模块构建,例如可配置逻辑块 (CLB)、I/O 块或焊盘以及开关矩阵/互连线。下面将简要讨论每个块。

- CLB(可配置逻辑块): 这些是 FPGA的基本单元。它由一个 8 位函数发生器、两个 16 位函数发生器、两个寄存器 (触发器或锁存器) 和可重新编程的路由控制 (多路复用器) 组成。CLB 用于实现其他设计的函数和宏。每个 CLB 的每一侧都有 inputs,这使得它们非常适合 logic的映射和分区。

- I/O 板或块: 输入/输出焊盘用于外部外设访问 FPGA 的功能,使用 I/O 焊盘,它还可以与使用不同外设的不同应用的 FPGA 通信。

- 开关矩阵/互连线: Switch Matrix 在 FPGA 中用于将长短互连线灵活组合连接在一起。它还包含用于打开/关闭不同线路之间连接的晶体管。

当需要 FPGA 时

如上所述,微控制器有一些限制,不能用于并行执行任务,因为微控制器和微处理器在程序的顺序执行上运行,这使得它在某些应用中有点慢,在这种情况下,FPGA 具有优势并且可以有效使用。此外,微控制器可以执行有限的任务,因为它们带有指令及其电路。程序员在开发代码时必须遵守这些限制。所以在这种情况下, FPGAs 也有优势。

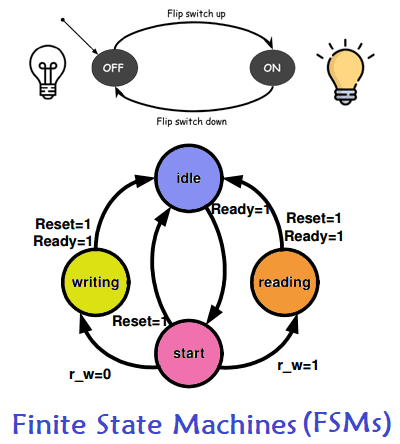

但是,对于微控制器,处理器会从一个代码切换到另一个代码,以实现一定程度的并行性。您会发现在微控制器上编写代码比在 FPGA 上编写代码更容易。FPGA 的并行处理功能使您能够使用有限状态机 (FSM) 有效地控制中断。

对于微控制器,您必须考虑 ISR 解决中断所花费的时间。您只需重新编程即可轻松重新连接 FPGA。当电源打开时,FPGA 中的配置将加载到 configurable logic cells 上。

您无需对硬件进行任何更改即可重新编程 FPGA。FPGA 适用于并行数据的高速处理,并具有高度的可定制性。但是,它们也存在原型操作和配置复杂性的缺点。因此,可以选择具有这些优势的 FPGA,而不是微控制器。让我们开始 FPGA 编程并更多地强调 FPGA 编程。

编程 FPGA(现场可编程门阵列)

FPGA 的编程由 HDL (硬件描述语言) 完成。有几种 HDL 可用,但 VHDL 和 Verilog 是广泛使用的 HDL。尽管 HDL 代码和高级软件编程语言之间存在一些相似之处,但两者在本质上是不同的。软件代码是一系列操作并按顺序执行处理,而 HDL 代码是使用文本引入组件并通过并行处理创建互连的示意图。

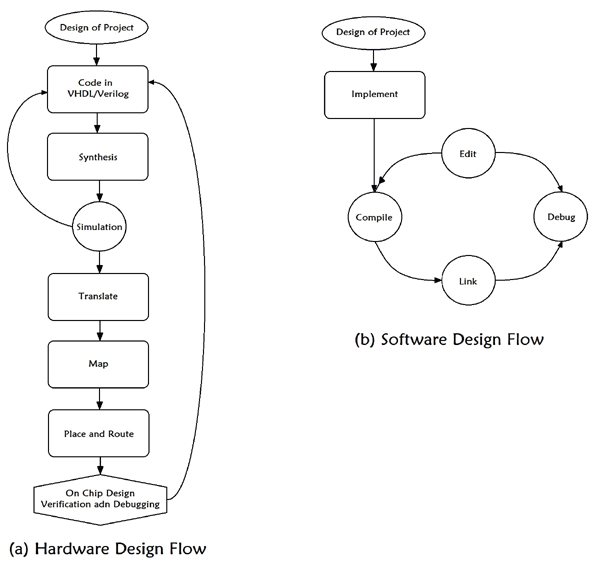

为了更好地理解它,请注意 FPGA 和 Microcontrollers 中分别涉及的 Hardware and Software Design Flow 中涉及的步骤之间的差异。

硬件设计流程和软件设计流程:

典型的硬件和软件流程如上所示。硬件设计流程用于对 FPGA 进行编程,而软件设计流程用于对典型的微控制器和微处理器进行编程。编程 FPGA 涉及的重要步骤如下。

- 合成: 第一步是综合,它采用 HDL 代码并转换为 netlist,这是电路图或原理图的文本描述。

- 仿真:综合后,下一步涉及仿真,用于验证 netlist 中指定的设计是否正常工作。

- 将网表转换为二进制格式: 验证设计后,下一步是将 netlist 转换为二进制格式。元件和连接被映射到 CLB,设计被放置和布线以适应目标 FPGA(即 Place and Route)。

- 执行第二次模拟: 为了查看设计质量,将执行第二次仿真。

- Generate Bit File:最后生成一个位文件以将设计加载到 FPGA 上(.bit 文件是一个配置文件,用于对 FPGA中的所有资源进行编程)。

- 验证和调试: 最后,使用不同的工具对设计在 FPGA上运行时进行验证和调试。

与硬件设计流程不同,软件设计流程中不需要实现前仿真步骤。此外,软件的编译时间比硬件设计的实现时间短得多,因此将重新编译代码并将调试作为迭代过程执行是可行的。

编程语言和工具

如上所述,有几种编程语言和工具可用于编程和调试 FPGA,但使用最广泛的是 VHDL 和 Verilog。VHDL 和 Verilog 都是成熟且广泛支持的 HDL。就程序 FPGA 而言,人们需要忘记软件编码行为,开始考虑逻辑门和电路来实现想要在 FPGA 上运行的功能。

有许多 FPGA 开发工具可用,例如:

VHDL/Verilog 的:这两种语言都提供了结构来描述 FPGA / ASIC 开发固有的并行性质。由于它们最初用于在生成综合工具之前描述电路的行为,因此这些语言还支持测试平台来测试正在实现的设计。

LabVIEW FPGA: LabVIEW 是一种图形语言,它提供了一种完全不同的 FPGA 编程方式。LabVIEW FPGA 是 FPGA 编译 使用 基于云的 选项, 可显著加快编译时间。

MATLAB 的:MATLAB 是可以发挥重要作用的语言,应该进行研究。MATLAB 通常用于生成用于信号处理的滤波器、开发图像处理算法和几乎任何其他算法。但除此之外,还可以使用 HDL 编码器从 MATLAB 模型转到 FPGA。可追溯性使可以使用这种方法开发高完整性应用程序。HDL 编码器支持执行硬件 (FPGA) 循环测试和协同仿真,以查看原始算法和已实现的硬件算法之间的差异,这有助于探索设计空间。

除此之外,还有其他类似的工具,例如 MyHDL、JHDL、BSV、System Verilog、SPINAL HDL、CHISEL、C/C++/System C 等。

结论

FPGA 无疑以自己的方式非常出色。从并行处理开始到加载位文件,FPGA 有几个优点,例如速度、现场可编程,但它也有一些缺点,例如曝光率低、社区支持率低、在 HPC 中不太受欢迎。FPGA 的最初体验不如预期,但经过多次练习后,对 FPGA 进行编程会很方便。此外,现代 FPGA 是高性能设备,在某些需要多功能性的应用中可以发现这些 FPGA 具有潜在优势。

1816

1816

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?