FPGA加速计算生态系统:从Vivado到Vitis AI的全面解析

引言

在当今高性能计算和人工智能快速发展的时代,传统的通用处理器(CPU)已经难以满足不断增长的计算需求。异构计算作为一种新型计算范式,结合了不同类型的处理器来实现高效计算,正成为解决这一挑战的关键方向。在异构计算领域,现场可编程门阵列(FPGA)因其可重构性、高并行度和低功耗特性,成为加速计算的重要选择。

赛灵思(Xilinx,现已被AMD收购)作为FPGA领域的领导者,提供了一套完整的开发生态系统,包括硬件设计工具、软件开发平台、运行时环境和应用框架,支持从硬件设计到应用部署的全流程开发。理解这个生态系统的各个组成部分及其相互关系,对于高效开发FPGA加速应用至关重要。

本文将深入探讨赛灵思生态系统中的关键组件,包括各种文件格式(.hwh、.xclbin、.xo等)、开发工具(Vivado、Vitis、v++等)、硬件加速器(DPU)、运行时环境(XRT、VART)以及应用框架(PYNQ、DPU-PYNQ)。通过详细的解释和实例,帮助读者全面理解这些组件之间的层次关系和工作流程,为高效开发FPGA加速应用奠定基础。

基础文件格式详解

在深入了解赛灵思生态系统的工作流程之前,我们首先需要理解几种关键的文件格式,它们在整个开发流程中扮演着重要的角色。

.hwh文件

.hwh文件(Hardware Handoff File)是Vivado设计工具生成的硬件描述文件,采用XML格式,包含了FPGA硬件设计的详细信息。这个文件对于理解硬件平台的结构和特性至关重要,尤其是在软件开发阶段。

主要内容和功能:

- 硬件架构描述:详细记录了FPGA上的硬件模块、连接关系和接口定义。

- 地址映射信息:定义了各个硬件组件的地址空间,使软件能够通过特定地址访问硬件资源。

- 寄存器定义:描述了各个硬件模块的控制寄存器和状态寄存器。

- 中断配置:记录了中断的连接和配置信息。

- 时钟和复位信息:描述了系统的时钟域和复位机制。

.hwh文件在PYNQ框架中特别重要,它被用来自动生成Python API,使软件开发者能够通过Python代码直接访问和控制FPGA上的硬件资源,而无需深入了解底层硬件细节。

.xsa文件

.xsa文件(Xilinx Shell Archive)是Vivado工具生成的硬件平台描述文件,它是一个综合性的文件包,包含了完整的硬件平台信息。

主要内容和功能:

- 比特流文件:包含了FPGA的配置数据,用于编程FPGA设备。

- 硬件描述文件:包含了硬件平台的详细描述,包括

.hwh文件。 - 软件组件:包含了驱动程序、库文件和其他软件资源。

- 元数据:描述了平台的属性和特性。

.xsa文件是连接硬件设计和软件开发的桥梁,它将复杂的硬件设计封装成一个标准化的平台定义,供Vitis等上层工具使用。Vitis工具可以导入.xsa文件,基于其中的硬件平台信息进行软件应用和硬件加速器的开发。

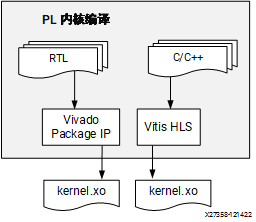

.xo文件

.xo文件(Xilinx Object)是Vitis工具链中的硬件内核对象文件,它是从高级语言(如C/C++/OpenCL)或RTL设计编译生成的中间文件,代表了一个硬件加速器内核。

主要内容和功能:

- RTL描述:包含了硬件内核的寄存器传输级描述,可以是由高层次综合(HLS)工具从C/C++/OpenCL代码生成,也可以是直接编写的RTL代码。

- 接口定义:描述了内核的输入输出接口,包括参数和存储器接口。

- 编译元数据:包含了编译过程中的信息,如资源使用估计、时序约束等。

- 调试信息:支持硬件内核的调试和分析。

.xo文件的生成是Vitis设计流程中的重要一步,它将高级语言描述的算法转换为可以在FPGA上实现的硬件模块。多个.xo文件可以被链接在一起,形成一个完整的硬件加速系统。

生成.xo文件的典型命令如下:

v++ -c -t hw --platform /path/to/platform.xsa -k kernel_name -o kernel.xo source_file.cpp

这个命令将源代码文件source_file.cpp中的kernel_name函数编译为硬件内核对象kernel.xo。

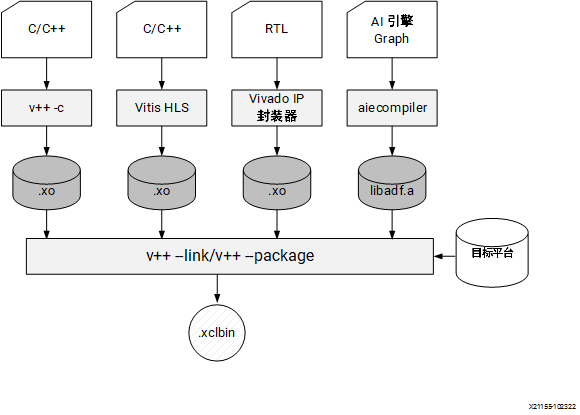

.xclbin文件

.xclbin文件(Xilinx Compute Library Binary)是Vitis工具链生成的最终硬件加速器二进制文件,它包含了完整的硬件加速器实现,可以被XRT运行时加载到FPGA上执行。

主要内容和功能:

- FPGA比特流:包含了FPGA的配置数据,用于编程FPGA设备。

- 内核元数据:描述了内核的接口、特性和资源需求。

- 存储器映射:定义了内核的存储器映射和数据传输路径。

- 运行时配置:包含了运行时需要的配置信息。

.xclbin文件是硬件加速器的可执行形式,它将一个或多个.xo文件与目标平台链接在一起,形成一个完整的硬件加速系统。XRT运行时可以加载.xclbin文件,配置FPGA,并管理硬件加速器的执行。

生成.xclbin文件的典型命令如下:

v++ -l -t hw --platform /path/to/platform.xsa -o final.xclbin kernel1.xo kernel2.xo --config config.ini

这个命令将两个内核对象kernel1.xo和kernel2.xo链接到指定平台,并根据配置文件config.ini生成最终的.xclbin文件。

Vivado设计流程

Vivado是赛灵思提供的主要FPGA设计环境,用于创建和实现硬件设计。它支持从RTL设计到比特流生成的完整流程,是开发FPGA应用的基础工具。

Vivado概述

Vivado设计套件是一个综合性的FPGA设计环境,提供了图形用户界面和命令行界面,支持多种设计输入方式,包括VHDL、Verilog和IP集成。它包含了多种工具和功能,支持FPGA设计的各个阶段,从设计输入到实现和验证。

主要功能:

- 项目管理:创建和管理FPGA设计项目。

- IP集成:集成和配置预定义的IP核。

- RTL设计:编写和编辑VHDL和Verilog代码。

- 综合:将RTL代码转换为门级网表。

- 实现:执行布局布线,生成最终的FPGA实现。

- 时序分析:分析和验证设计的时序性能。

- 功耗分析:估计和优化设计的功耗。

- 比特流生成:生成FPGA的配置文件。

Vivado设计流程步骤

Vivado设计流程是一个结构化的过程,包括多个步骤,从设计输入到最终的比特流生成。下面是典型的Vivado设计流程步骤:

-

创建项目:

- 启动Vivado并创建新项目

- 选择目标FPGA器件

- 设置项目参数和选项

-

设计输入:

- 编写或导入RTL代码(VHDL/Verilog)

- 添加和配置IP核

- 创建约束文件(XDC)

-

行为仿真:

- 创建测试台(Testbench)

- 运行行为级仿真

- 验证设计功能

-

综合:

- 将RTL代码转换为门级网表

- 优化设计逻辑

- 分析综合结果和资源使用情况

-

实现:

- 执行布局(Placement):将逻辑元素映射到FPGA的物理资源

- 执行布线(Routing):连接逻辑元素

- 优化实现以满足时序和资源约束

-

时序分析:

- 验证设计是否满足时序要求

- 识别和解决时序违例

- 优化关键路径

-

比特流生成:

- 生成FPGA的配置文件(.bit)

- 生成编程文件和调试文件

-

硬件验证:

- 将比特流下载到FPGA设备

- 验证硬件功能

- 调试和优化

-

导出硬件平台:

- 生成硬件平台文件(.xsa)

- 包含比特流、硬件描述和软件组件

- 准备用于Vitis开发

生成硬件平台

在Vivado设计流程的最后阶段,我们需要导出硬件平台,生成.xsa文件,供Vitis等上层工具使用。这个过程涉及到以下步骤:

-

准备硬件设计:

- 确保硬件设计已经完成并通过验证

- 确保所有必要的接口和IP核已经正确配置

- 验证设计满足时序和资源约束

-

导出硬件平台:

- 在Vivado中选择"File" > “Export” > “Export Hardware”

- 配置导出选项,包括是否包含比特流

- 选择导出路径和文件名

-

生成.xsa文件:

- Vivado会生成一个

.xsa文件,包含硬件平台的完整信息 - 同时会生成

.hwh文件,包含硬件描述信息

- Vivado会生成一个

-

验证导出结果:

- 检查导出的

.xsa文件是否完整 - 验证硬件平台的接口和功能

- 检查导出的

导出的硬件平台(.xsa文件)包含了硬件设计的所有必要信息,包括比特流、硬件描述、接口定义和软件组件。它是连接硬件设计和软件开发的桥梁,使得软件开发者可以基于硬件平台进行应用开发,而无需深入了解硬件设计的细节。

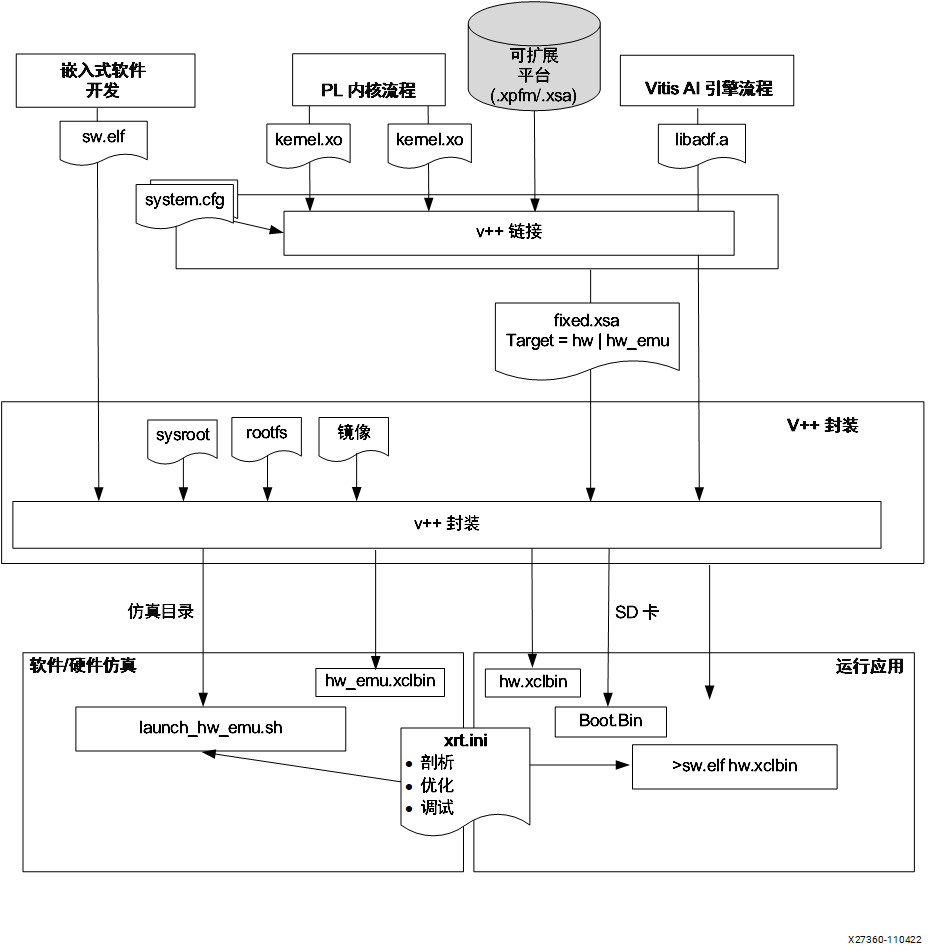

Vitis设计流程

Vitis是赛灵思提供的统一软件平台,旨在简化FPGA应用的开发流程。它支持从高级语言(C/C++/OpenCL)开发硬件加速器,并提供了完整的工具链,支持从开发到部署的全流程。

Vitis概述

Vitis统一软件平台是一个综合性的开发环境,支持FPGA应用的软件和硬件协同设计。它提供了图形用户界面和命令行界面,支持多种开发模式和应用领域,包括数据中心、嵌入式系统和AI加速。

主要功能:

- 应用开发:支持C/C++/Python应用开发。

- 硬件加速:支持从C/C++/OpenCL开发硬件加速器。

- 系统优化:提供性能分析和优化工具。

- 调试和分析:支持软件和硬件的调试和分析。

- 部署和管理:支持应用的部署和运行时管理。

v++工具详解

v++是Vitis工具链中的核心命令行工具,用于编译、链接和打包硬件加速器。它支持从高级语言(C/C++/OpenCL)开发硬件加速器,并生成可以在FPGA上执行的二进制文件。

主要功能:

- 编译:将高级语言代码编译为硬件内核对象(.xo)。

- 链接:将硬件内核对象和硬件平台链接为硬件加速器二进制文件(.xclbin)。

- 打包:将多个硬件加速器打包为一个系统。

- 优化:提供多种优化选项,提高硬件加速器的性能和效率。

v++工作流程:

-

编译阶段:

- 输入:高级语言代码(C/C++/OpenCL)

- 处理:高层次综合(HLS),将高级语言代码转换为RTL描述

- 输出:硬件内核对象(.xo)

-

链接阶段:

- 输入:硬件内核对象(.xo)和硬件平台(.xsa)

- 处理:系统集成,将硬件内核与平台连接

- 输出:硬件加速器二进制文件(.xclbin)

v++命令示例:

编译命令:

v++ -c -t hw --platform /path/to/platform.xsa -k kernel_name -o kernel.xo source_file.cpp

链接命令:

v++ -l -t hw --platform /path/to/platform.xsa -o final.xclbin kernel1.xo kernel2.xo --config config.ini

Vitis设计流程步骤

Vitis设计流程是一个结构化的过程,包括多个步骤,从应用分析到系统部署。下面是典型的Vitis设计流程步骤:

-

创建项目:

- 启动Vitis并创建新项目

- 选择目标平台(.xsa)

- 设置项目参数和选项

-

应用分析:

- 分析应用的计算特性和瓶颈

- 确定需要加速的部分

- 制定硬件/软件分区策略

-

硬件加速器开发:

- 使用C/C++/OpenCL编写硬件加速器

- 使用Vitis HLS优化硬件实现

- 验证硬件功能和性能

-

软件应用开发:

- 使用C/C++/Python编写主机应用

- 集成XRT API,控制硬件加速器

- 实现数据传输和同步机制

-

系统集成:

- 使用v++工具链接硬件加速器和平台

- 生成系统二进制文件

- 验证系统功能和性能

-

部署和运行:

- 将系统部署到目标平台

- 运行应用并验证结果

- 监控和分析系统性能

Vivado与Vitis设计流程的比较

Vivado和Vitis代表了两种不同的FPGA开发方法,它们各有优势和适用场景。

Vivado设计流程:

- 基于硬件描述语言(HDL)如VHDL和Verilog

- 完全控制硬件实现细节

- 适合底层硬件设计和优化

- 设计周期可能较长

- 需要深厚的硬件设计知识

Vitis设计流程:

- 基于高级语言(C/C++/OpenCL)

- 硬件和软件协同设计

- 高级优化和自动化

- 更快的设计周期

- 降低了入门门槛

两种流程的关系:

- Vivado通常用于创建基础硬件平台(.xsa)

- Vitis使用这些平台来开发和部署加速器

- 复杂项目可能同时使用两种流程

- Vitis在内部仍然使用Vivado工具进行硬件综合和实现

XRT(Xilinx Runtime)

XRT(Xilinx Runtime)是赛灵思提供的运行时环境,用于管理和控制FPGA上的硬件加速器。它提供了统一的软件接口,使应用程序能够与FPGA硬件交互,而无需关心底层硬件细节。

XRT架构

XRT的架构分为多个层次,每个层次负责不同的功能,共同实现硬件加速器的管理和控制。

XRT架构层次:

-

应用层API:

- 提供C++和Python接口

- 支持OpenCL标准

- 提供XRT本地API

-

XRT核心库:

- 实现核心功能和算法

- 管理内存和设备资源

- 调度和执行硬件加速器

-

驱动层:

- 与操作系统和硬件交互

- 管理设备访问和中断

- 实现内存映射和DMA传输

-

硬件抽象层:

- 适配不同的FPGA平台

- 实现平台特定的功能

- 提供统一的抽象接口

XRT功能

XRT提供了一系列功能,使应用程序能够高效地使用FPGA硬件加速器。

主要功能:

-

设备管理:

- 发现和初始化FPGA设备

- 加载和配置硬件加速器

- 管理设备状态和资源

-

内核执行:

- 启动和停止硬件内核

- 管理内核执行状态

- 同步和协调多个内核

-

内存管理:

- 分配和释放设备内存

- 管理主机和设备之间的数据传输

- 实现零拷贝和缓冲区共享机制

-

事件管理:

- 创建和管理事件

- 实现异步执行和回调机制

- 支持同步和异步操作模式

-

性能监控:

- 收集和分析性能数据

- 提供性能分析工具

- 支持性能优化和调试

XRT编程模型

XRT支持多种编程模型,使开发者能够根据需求选择合适的接口和抽象级别。

主要编程模型:

-

OpenCL API:

- 符合OpenCL标准的API

- 支持异构计算模型

- 提供标准化的接口和抽象

-

XRT本地API:

- 提供更直接的FPGA访问

- 支持特定于XRT的功能

- 提供更高的性能和控制

-

C++/Python高级API:

- 提供更简洁和直观的接口

- 简化常见操作和模式

- 提高开发效率和可读性

93

93

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?