这几天一直有人问setup和hold在DC中怎么体现出来,感觉自己理解得还是比较可以的,所以决定写下来,因为确实比较搞,同时也防止以后自己忘记。

其实,之所以会有这个问题是因为DC中时间约束(timing constraint)机制,而这个时间约束机制中一部分可以来验证是否违反setup和hold的时间要求。

在讲之前,我们首先要明白,setup和hold是用来做什么的。所谓setup,就是建立时间,也就是在时钟到达之前,信号所必需存在的时间。而hold,就是保持时间,也就是在时钟到达之后,信号必须保持的时间(在保持时间内,信号不允许改变)。

在DC中,一个设计的setup和hold时间是分别通过max 和min 来验证是否满足时间约束的。

使用max来约束setup时间

对于max 我们有input 和output 两种方式

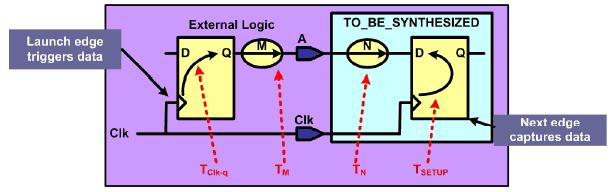

(1) Input

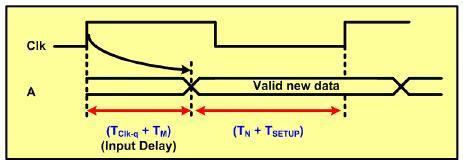

我们可以看到,input的block图,外部逻辑在输入的时候总归是有一个延时的,于是,在每个时钟周期内,留给逻辑块N和D触发器(和N相连的那个)的有效时间就可以计算出来

通过观察输入的时序图,可以得出:T

N + T

SETUP 必须小于等于T

Clk – (T

Clk-q + T

M),即,这就是T

SETUP的约束条件。如果T

N + T

SETUP 大于T

Clk – (T

Clk-q + T

M) 就违反了约束规则。

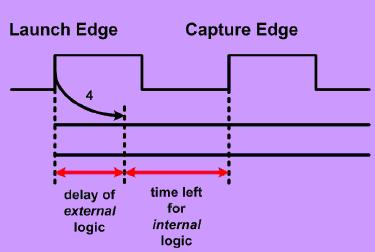

例如:外部的逻辑延时为4,则留给内部逻辑来传输信号和建立(setup)信号的时间可以知道,也就是可以约束了

建立约束的命令如下:

shell>set_input_delay 4.0 -max -clock Clk [get_ports A]

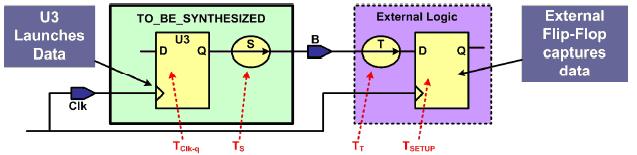

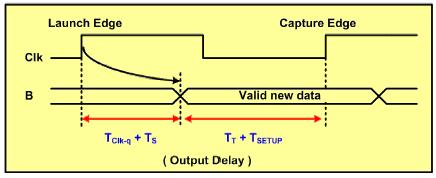

(2) output

从output的block图和时序图中,我们可以看到内部的信号要给外部的电路,同样要满足T

T + T

SETUP 必须小于等于T

Clk – (T

Clk-q + T

S),即,只要知道了T

T + T

SETUP 则T

Clk-q + T

S也就确定了

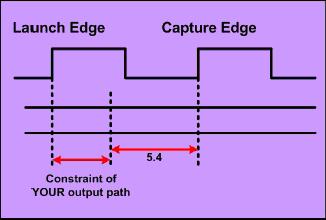

例如:外部的建立时间和传输时间必须为5.4,则留给内部电路的时间就有约束了

命令如下:

set_output_delay 3.0 -max -clock Clk [get_ports B]

使用min来约束hold时间

对于 min 我们也有input 和output两种方式

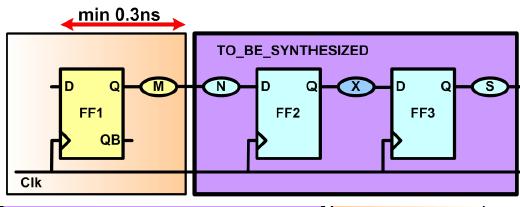

(1) input

从block图中我们看到输入的最小延时为0.3ns,而要使得hold时间满足要求,则必须

0.3 + T

N > T

HOLD即,hold时间可以通过输入的最小延时来约束。

命令如下:

shell>set_output_delay –min 0.3 –clock Clk $ALL_INS_EX_CLK

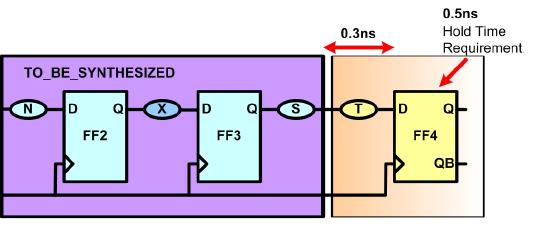

(2) output

从

block

图中可以看到外部电路的

hold

时间为

0.5ns

,而外部电路的逻辑电路的延时为

0.3ns

,要使得外部电路的

hold

时间符合约束,就必须要使内部电路的输出延时的最小值和外部逻辑电路延时之和大于

hold

时间

命令如下:

shell>set_output_delay –min [expr 0.3- 0.5] –clock Clk [all_outputs]

7387

7387

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?