文章目录

本文是对EDA教程《VLSL Physical Design》第六章的理解和笔记,对原文进行了翻译,评论和删减,若有谬误欢迎探讨和指出

前面一章讲了怎么在全局进行布线,把网络分配给各个布线区域,这一章更进一步,把网络直接分配到具体的轨道,金属层和通孔。

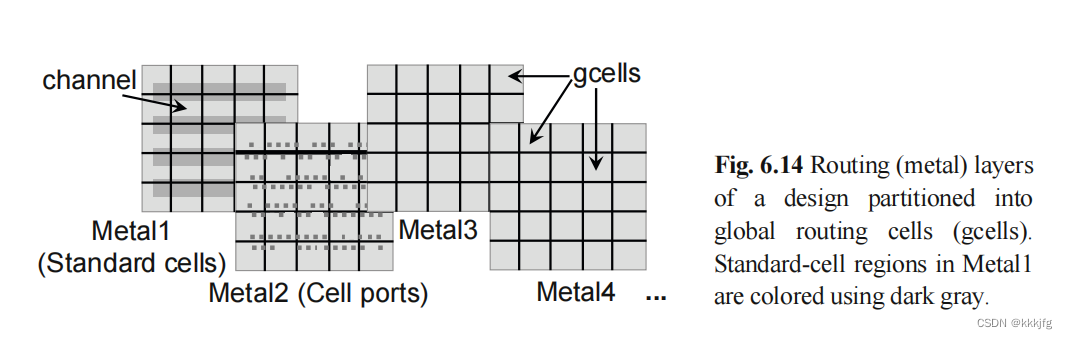

详细布线会在较小(比如10X10轨道大小)的区域内进行,这种区域也叫gcell,是指全局路由单元,其大小与芯片大小无关,可以理解为可以用来做详细布线的一个标准单元。在gcell中,各网络会被分配详细的轨道和通孔,不同的gcell之间互不影响,所以也可以并行处理。

6.1 术语

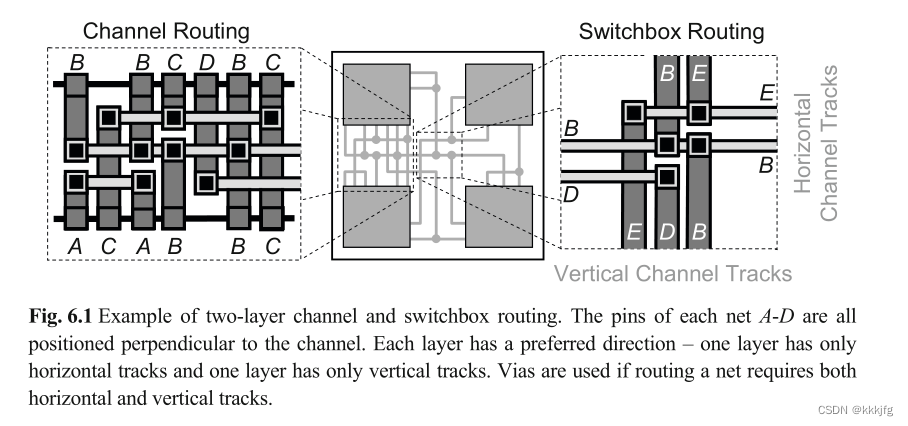

通道布线。通道布线是详细布线的一种特殊情况,只有两侧对端(比如上下)有端口,另外两侧没端口。按照惯例,一般把端口放在上下侧而不是左右侧,而且上下侧之间的通道是均匀摆放的。

交换盒布线。交换盒在四侧都有接口,所以比通道布线更难。

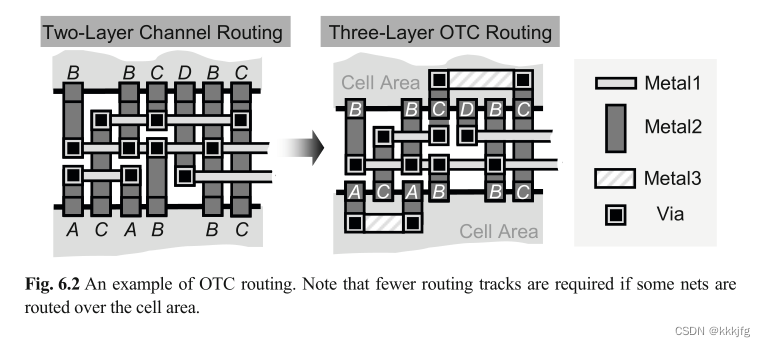

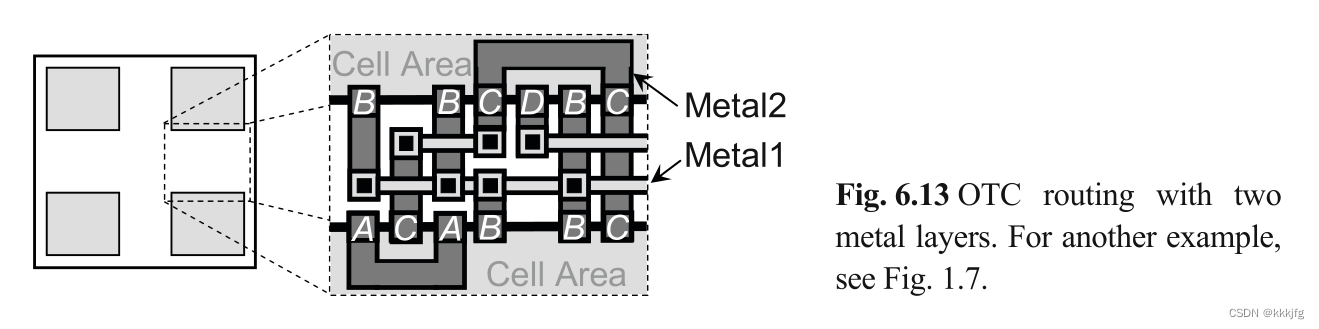

单元上布线(OTC (over-the-cell) routing)。OTC布线可以使用额外的金属层,比如Metal3和Metal4,这样它可以直接穿到功能单元和通道的上方布线,不受一些障碍的阻拦。

下图是两层布线(一层纵线一层横线,不含单元之上的金属层)的通道布线和交换盒布线的示意图。

如下是两层通道布线和三层的单元上布线的对比图。两层的通道通常由多晶硅层(一般叫polysilicon或poly,图中竖着的)和Metal1层(横的)组成,两层直接用通孔(vias)进行连接。而单元上布线多用了一个Metal3层,可以在单元上侧进行布线。

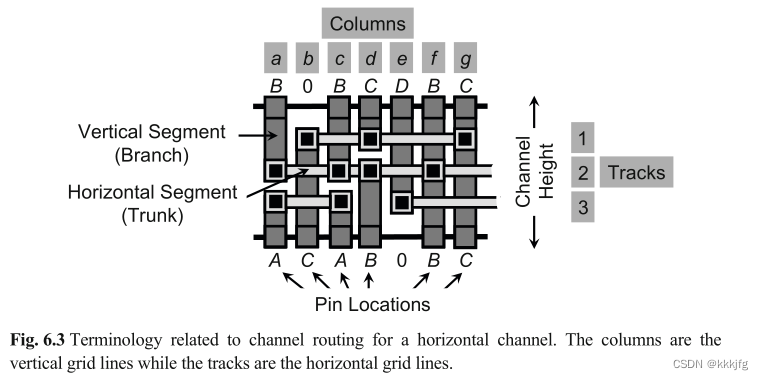

如图是一个通道布线的上下输入的表现形式,通常我们用两个向量来说明通道上下两侧是啥端口。如下,

T

O

P

=

[

B

0

B

C

D

B

C

]

TOP=[B\,0\,B\,C\,D\,B\,C]

TOP=[B0BCDBC],

B

O

T

=

[

A

C

A

B

0

B

C

]

BOT=[A\,C\,A\,B\,0\,B\,C]

BOT=[ACAB0BC]

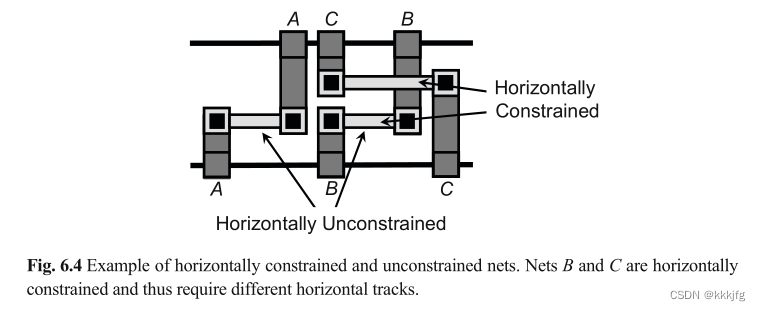

水平约束。指的是两个网络的横向线需要经过相同的列。为什么叫“水平约束”呢?大概是因为是水平线的约束吧,但给我的感觉是“俩水平线上下滑动的时候会打架卡住,而不是可以自由地从最顶到最低滑动”这样的约束,像是纵向的?但或许已经有一个垂直约束了所以只能叫这个。

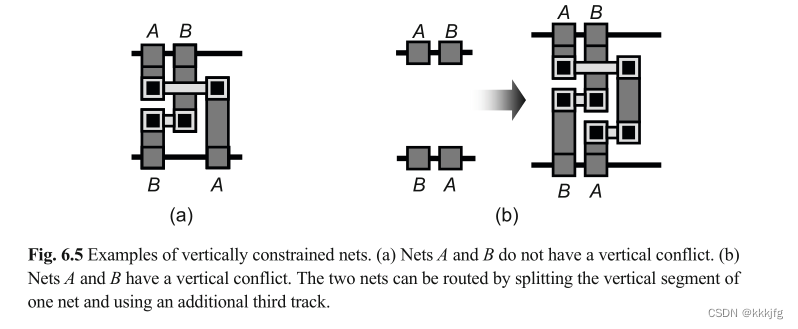

垂直约束。指的是同一列上,上下接了不同网络的端口,这样这个列上,上端口的网络和下端口的网络都不能无限延申到对面了。

而且如果有横向网络接上来的话,上端口的网络的横杠也会压在下端口的网络的横杠上方(比如下图图a,A网络就压在B网络上面了)。若两网络在两列都打架了,则这个垂直约束需要使用额外列解开,比如下图图b。

可以看到垂直约束会引来水平约束,不过水平约束并不总伴随着垂直约束。

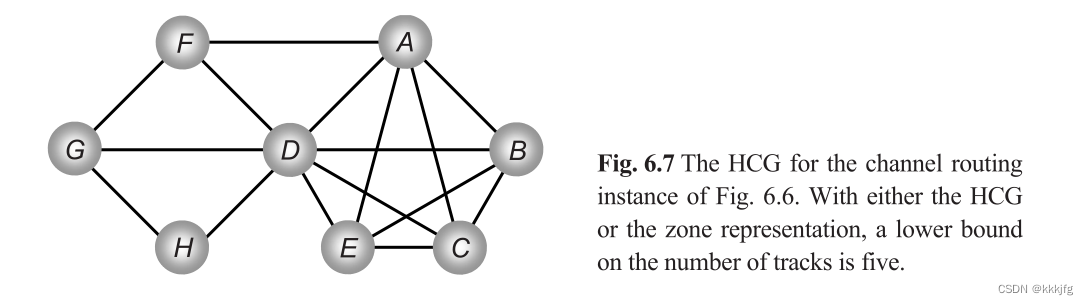

6.2 水平和垂直约束图(Horizontal and Vertical Constraint Graphs )

利用网络之间的水平约束和垂直约束关系,可以通过水平约束图和垂直约束图对网络的相对关系相对进行建模。这些图用于

(1)初步预测所需的最小轨道数量,(2)检测潜在的布线冲突。

6.2.1 水平约束图(Horizontal Constraint Graphs)

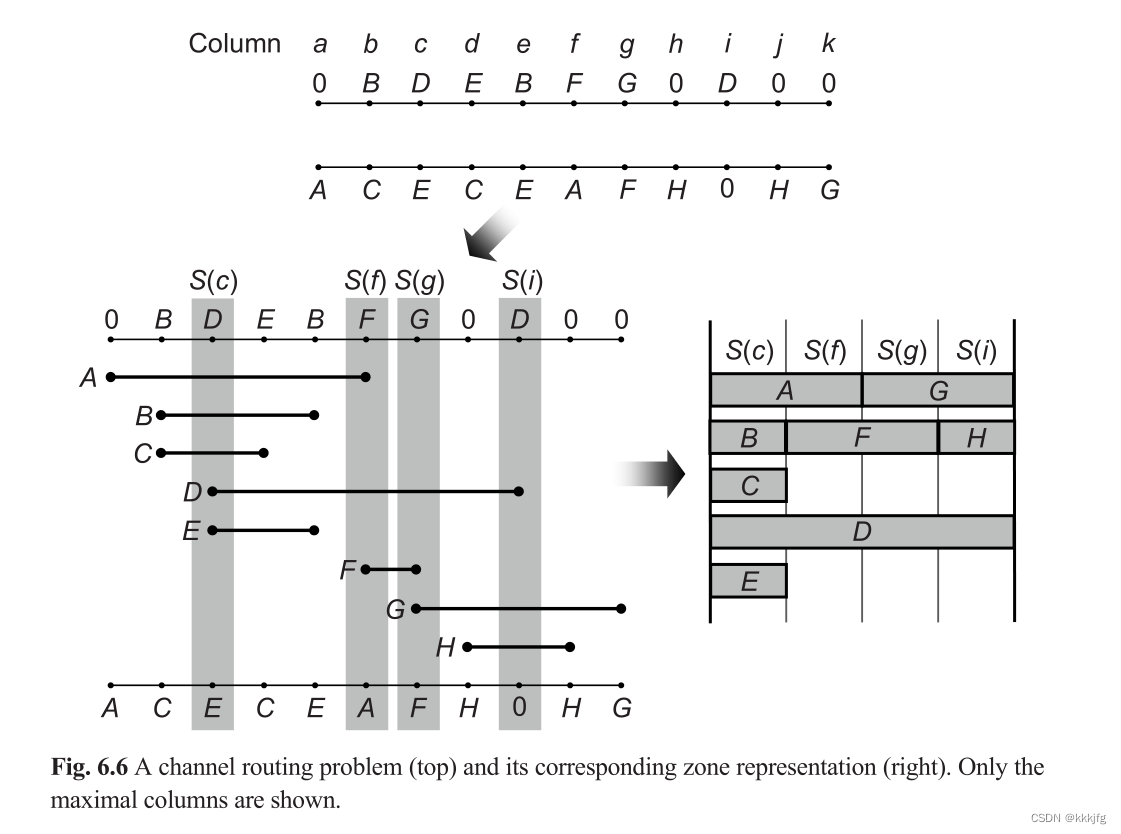

首先,我们定义 S ( c o l ) S(col) S(col)为水平线经过列 c o l col col或者有引脚在 c o l col col上的网络的集合。根据水平约束的定义,如果两个网络之间有水平约束关系,则它们的水平导线应该共同穿过同一列,而且我们应该不难发现,列 c o l col col下 S ( c o l ) S(col) S(col)这个集合中的网络两两都存在水平约束关系。所以从推断水平约束关系的角度看,如果 S ( i ) S(i) S(i)是 S ( j ) S(j) S(j)的子集, S ( i ) S(i) S(i)就可以直接被忽略了因为 S ( j ) S(j) S(j)中能推断出的水平约束关系是包含 S ( i ) S(i) S(i)中能推断出的水平约束关系的。如下,我们选择c,f,g,i四列分析水平约束关系。

不难发现,这个通道所需的最少轨道数是

S

(

c

o

l

)

S(col)

S(col)包含网络数的最大值,即5。

水平约束的图表示。如上我们分析

S

(

c

)

S(c)

S(c),

S

(

f

)

S(f)

S(f),

S

(

g

)

S(g)

S(g),

S

(

i

)

S(i)

S(i)四个集合,以各网络为点,并把同一个集合中的网络两两相连即可。

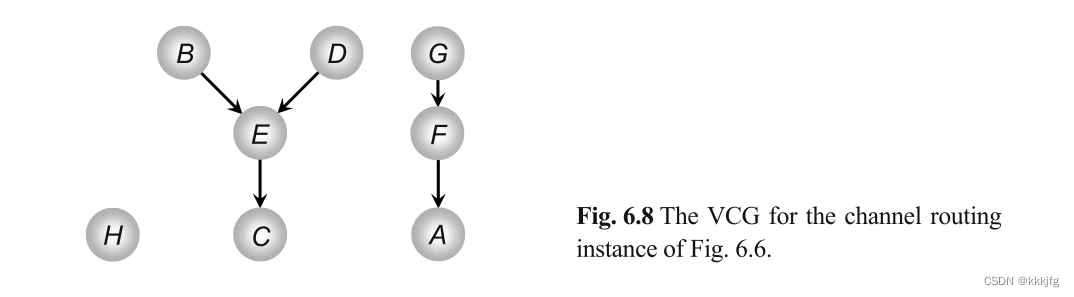

6.2.2 垂直约束图(Vertical Constraint Graphs)

垂直约束图是一个有向图,用来描述哪个网络“偏上”。

其具体定义是,若在某一列的上下两个端口中,i网络的端口在上,j网络的端口在下,则有一条有向边从点i指向点j。

绘制方式也很简单,从第一列一直向右看到最右一列,对于每一列,我们查看这列的上下两端口所属的网络,把上端口网络向下端口的网络指一条线即可。

为了简洁,绘制垂直约束图的时候要注意删去冗余边,若存在三条这样的边(G–>F),(F–>A),(G–>A),我们会把G指向A的那条边删掉。下图是上面的例子的垂直约束图。

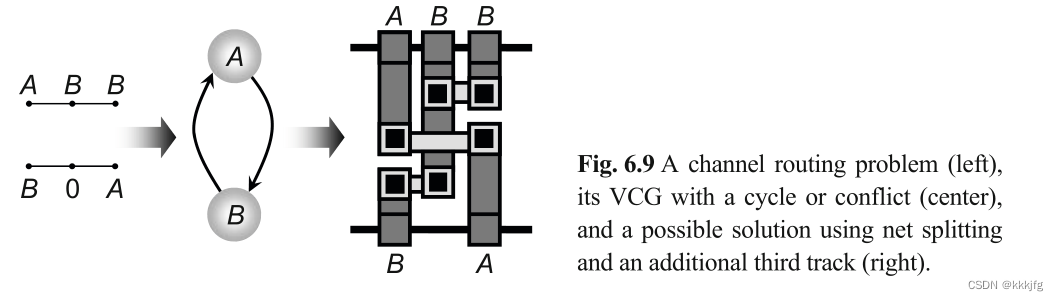

由于可能会出现既有A网络在B网络上侧且B网络在A网络上侧的情况(如下图最左列A在B上侧,最右列B在A上侧),这样的话会出现环。当出现环的时候,通道所需的轨道数就不严格等于最大的

S

(

c

o

l

)

S(col)

S(col)的网络数了,需要拆分网络解循环以便进一步的轨道数估计和考虑约束图的冲突。

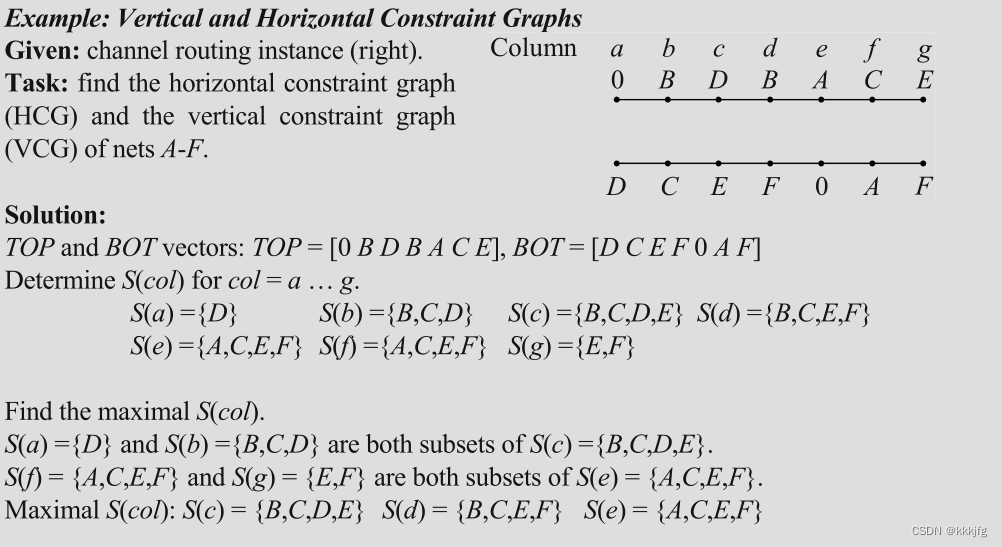

以下是一个构建水平约束图和垂直约束图的例子:

6.3 通道布线算法(Channel Routing Algorithms)

通道布线力求最大限度地减少完成布线所需的轨道数量。在门级别的设计中,通道高度通常是固定的,并且算法被设计为追求100%的路由完成。

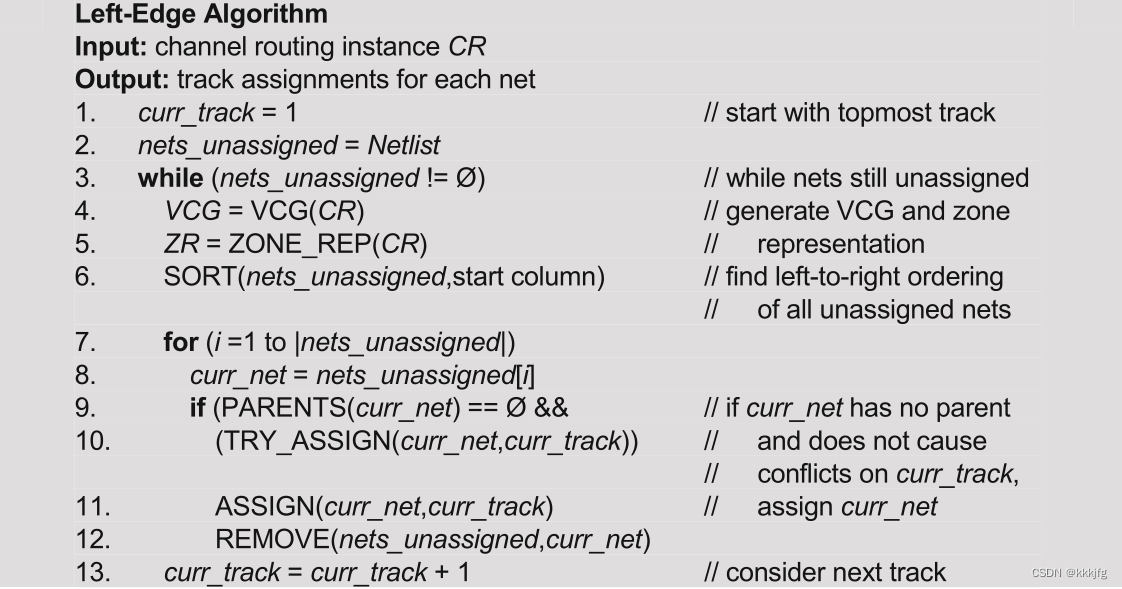

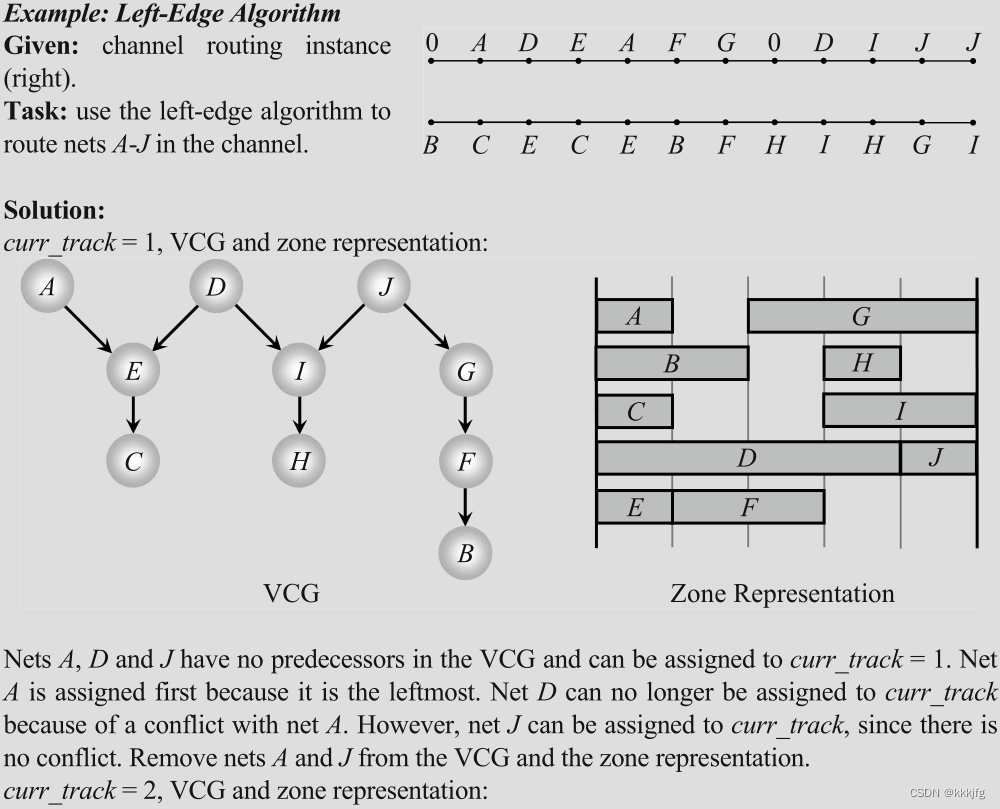

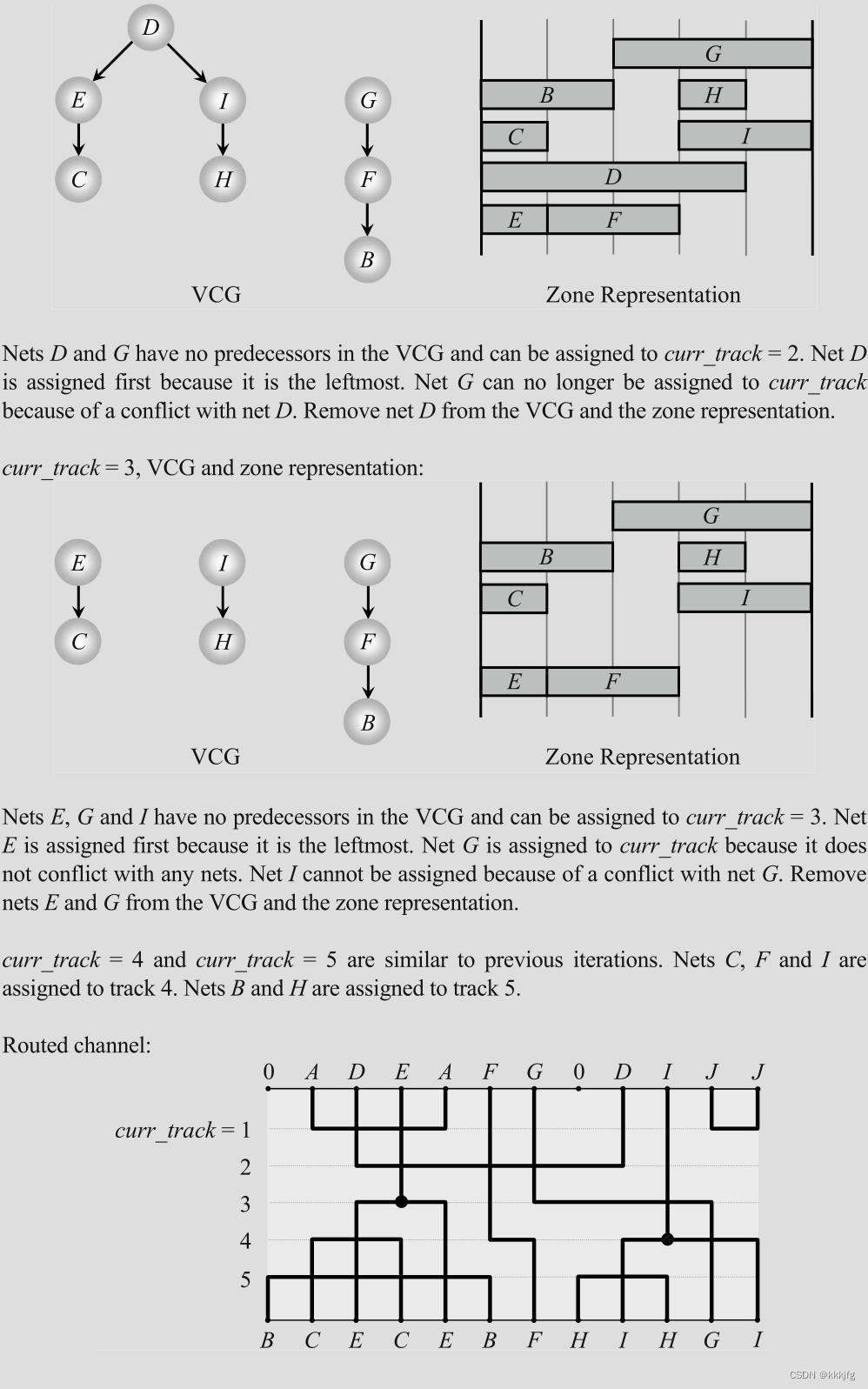

6.3.1 左侧边算法(Left-Edge Algorithm)

这里不知道怎么翻译了,感觉“左”“边”算法是最贴切的,但念起来太怪了。之所以叫“Left-Edge Algorithm”这个“Left”的意思是如果某行布线的时候出现冲突不能把好几个网络都放在同一行,优先给左侧的网络布线,而把右侧的网络延迟处理。

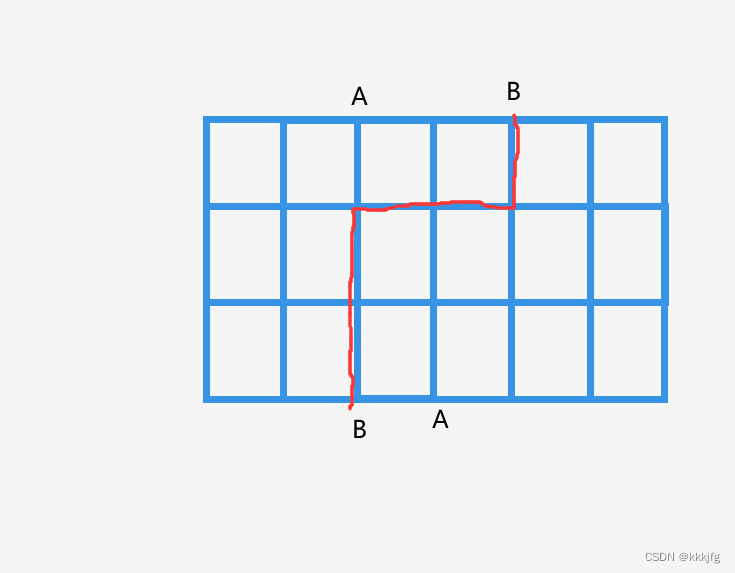

算法根据VCG来确定顺序,利用HCG信息来判断是否会出现同一行的水平方向的冲突,由于算法从最上行开始布线,所以VCG中要选择入度为0的点布设当前行,这样布完之后不会出现还有其他网络要使用小于等于它的行的情况。比如下图的例子中的VCG中a有一条指向b的线,所以a网络应该先布线,但如果不按规则来,先布b线,占用了从上往下第一行,就把a的入口封死了,先布a则不会出现堵死的问题。

这个算法从最上层轨道开始铺设网络,逐渐向下(列1,13)。对于每个轨道,都想尽办法做最大利用,把不冲突的线全部摆上(7-12),若在某一行,某网络与其他网络冲突,则延迟到后面的行再布(9,10),否则能布尽布(10-12行)。由于在尝试对当前行进行布线之前,对所有网络按开始列进行了排序(6行),所以靠左的网络能优先布,后来的更容易冲突。

若VCG图中没有循环,则这个算法可以找到一个所需轨道数为最大S(col)(S(col)是指使用了某列col的所有网络的集合)的解。

其改进包括把网络长度纳入考虑和把某些网络拆分以提高轨道利用率。

以下是一个例子:

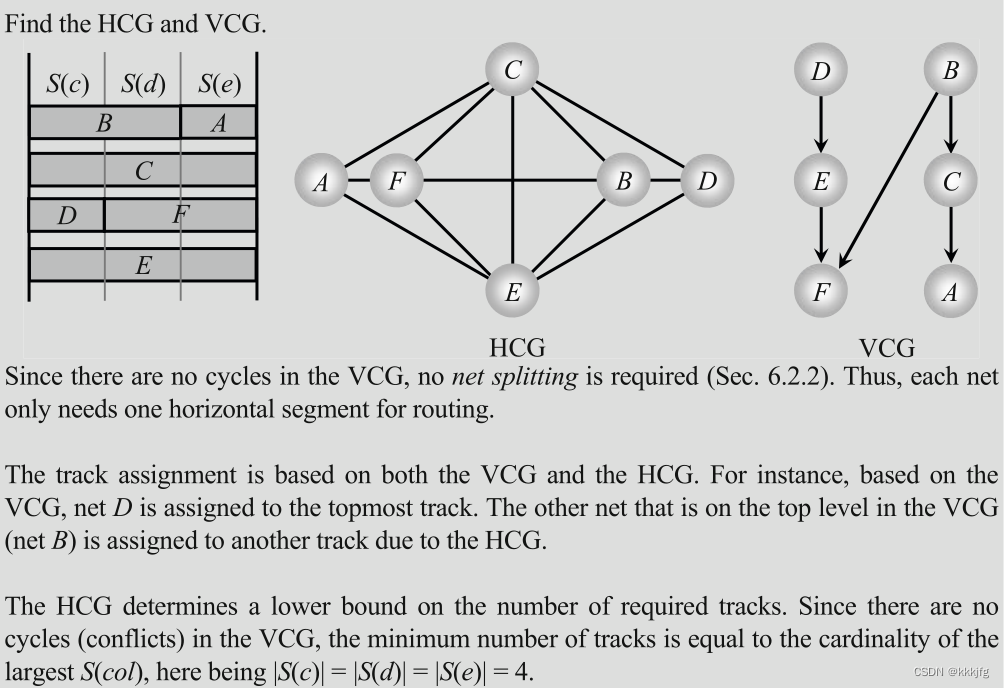

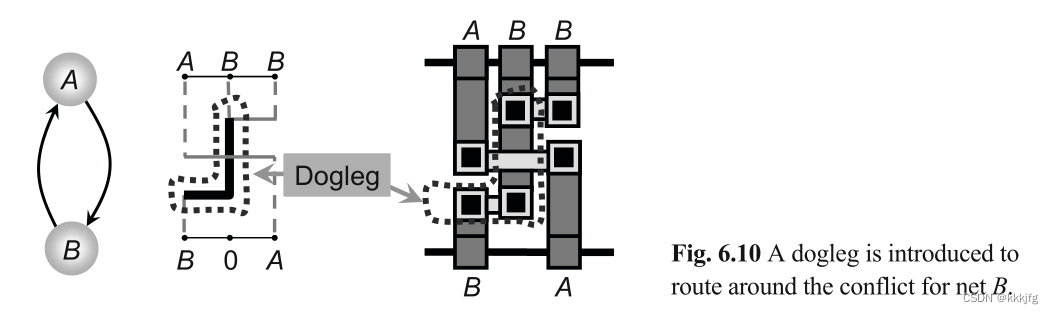

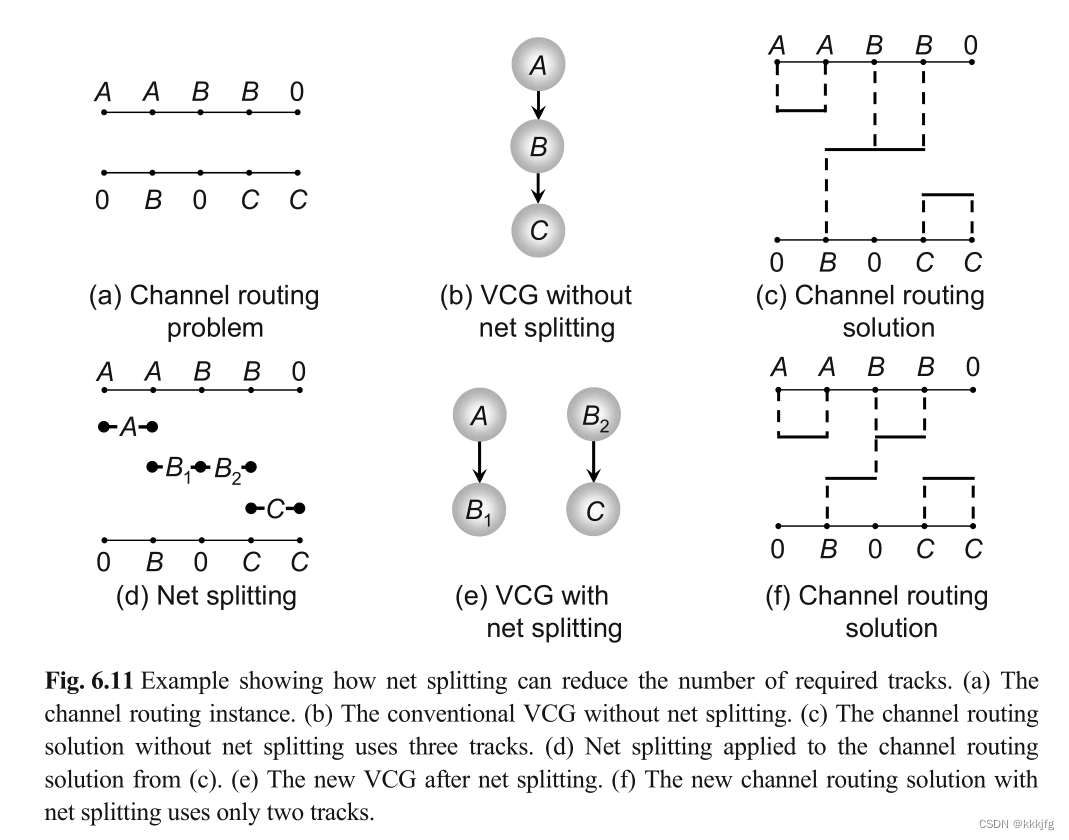

6.3.2 狗腿布线

“狗腿”布线的名字由来如下:B网络的横线被拆开成两份,有个L形区域连接两个部分,不过我还是没搞懂为啥叫“狗腿”,首先“L”不怎么像狗腿,其次连接两个半边的更准确来说是一小条竖线,为什么它把下面那个小横线也算上了?

狗腿算法是Deutsch在20世纪70年代开发的。该算法通过将p引脚网络(p>2)拆分为p-1个双引脚网络,然后再丢给左侧边算法。这样能消除VCG中的循环,并能减少路由轨道的数量。

拆分的方法是在需要拆分的网络的引脚列进行拆分。

以下是一个例子,这个例子中B网络从中间的引脚为界,拆成了B1和B2子网。

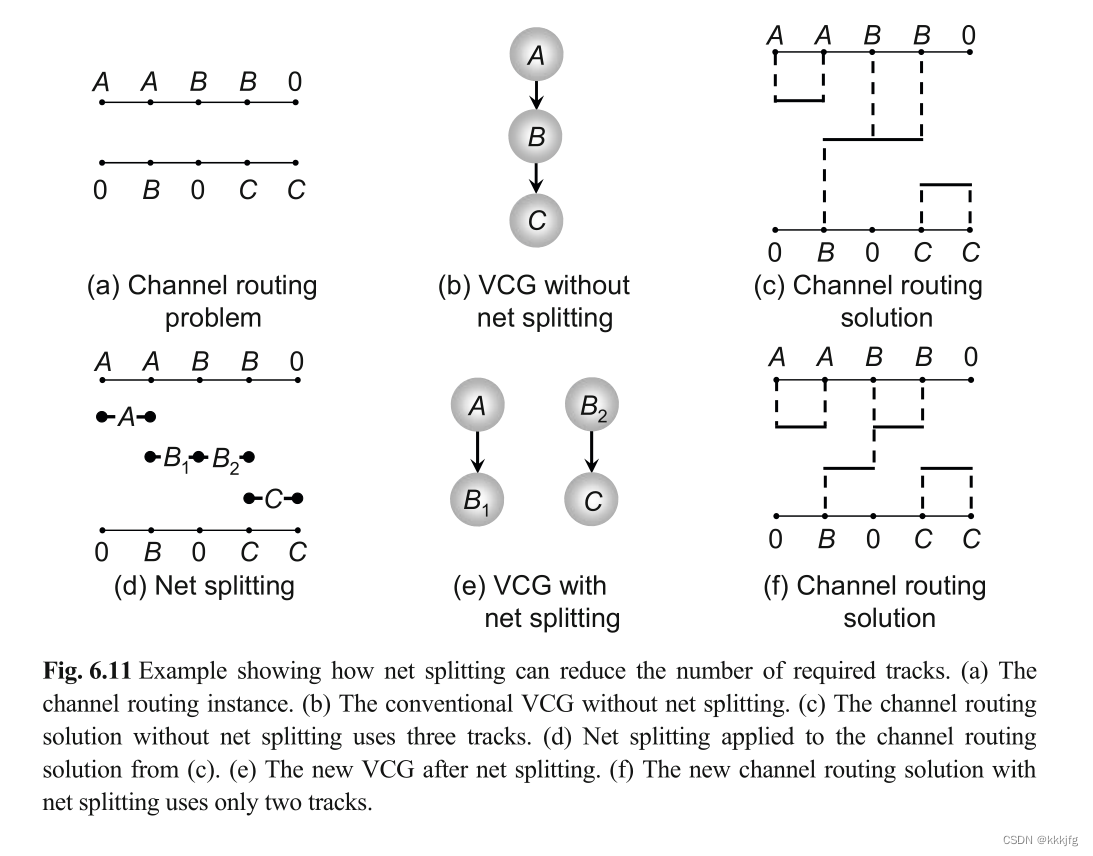

以下是一个混合了狗腿算法的左侧边算法的例子:

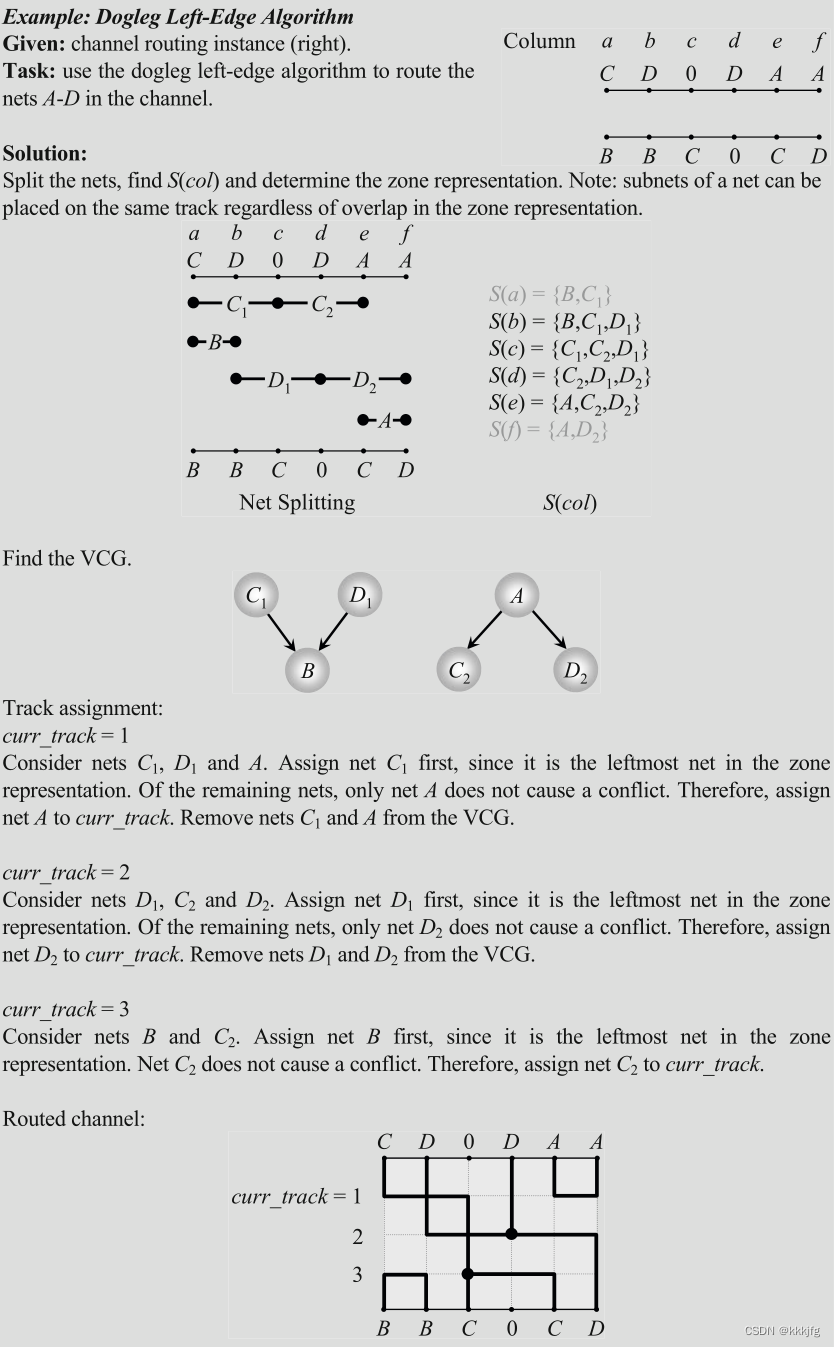

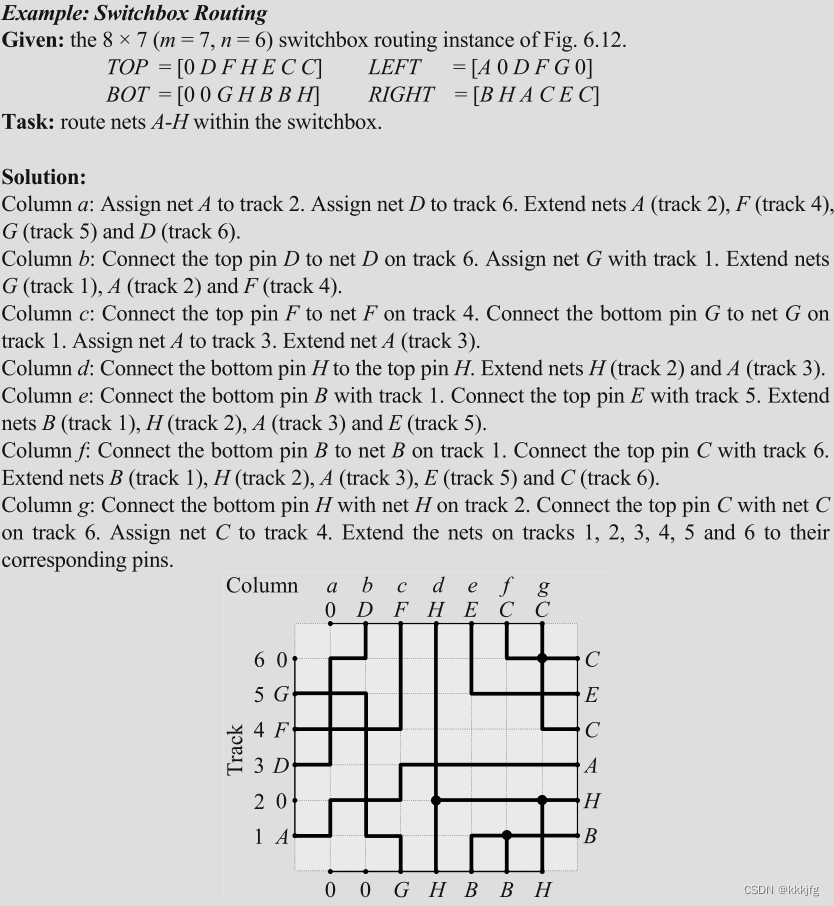

6.4 交换盒布线(Switchbox Routing)

用于交换盒的布线算法可以由信道路由算法修改获得。

一句话概括就是:

1,网络从最左侧的端口开始布线,逐渐向上、下、右扩展。

2,从最左列向最右列扫描,如果空间允许,则让当前的与目标端口不同一行的网络进行竖直铺设“拐一下”。

第二条是我看例子总结的,有点拗口,但反正是猜的,书上我看了半天没有找到很明显的说明合适应该在垂直方向扩展网络的规定或者算法,书上给的例子如下:

6.5 单元上布线(Over-the-Cell Routing Algorithms)

前面提过的方法都是基于两层布线的,但现在的工艺的金属层往往大于两层,这样可以使用较高的金属层,绕到单元上面进行布线。由于功能单元并不会在较高金属层造成障碍,所以在这些金属层进行布线可以跨单元模块进行布线,有更高的自由度。由于能借助高层金属层进行布线,功能单元也可以放得更加紧凑,不必依赖单元间的通道进行布线,这样能进一步减短线长,减小面积和提升可靠度。

OTC设计可以和通道并存,如在FPGA中,为了压缩层数,很多厂家会倾向于把线都布在通道里,但有的部件,比如 乘法器, 数字信号处理模块(digital signal processing ,DSP),存储,会使用高层金属层进行OTC布线。

6.5.1 OTC布线的方法(OTC Routing Methodology)

OTC布线的流程如下:

1,判断需要在通道之外进行布线的网络。

2,在OTC区域内给这些网络布线。

3,在通道内给剩余网络布线。

Cong和Liu在

O

(

n

2

)

O(n^2)

O(n2)时间内最优地解决了步骤1和步骤2,其中n是网络数目。

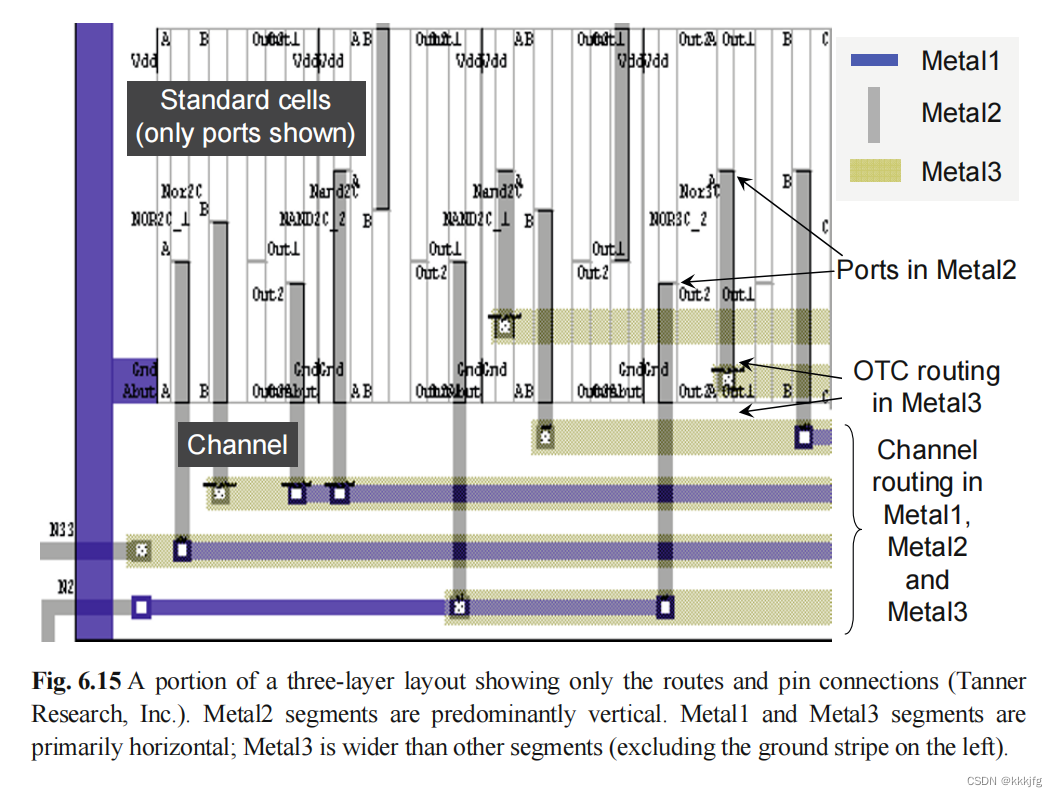

上图展示了一个三层的基于标准单元设计的例子。Metal3层既用于通道内的水平轨道也OTC布线。OTC布线最开始多使用三层金属层,而现代集成电路使用了六层或更多的金属层。

6.5.2 OTC布线算法(OTC Routing Algorithms)

书上的6.5.2并没有实际的算法,是一些算法的简介。这里简要掠过这些算法:

- Chameleon首先提出了一种OTC算法,创新点是考虑了不同层的具体情况,比如线宽。

- Cong, Wong 和 Liu先在两层上布线,再用一些算法映射到三层。这个算法还可以扩展成四层版本。

- Ho 等人开发了一种通过快速迭代简单启发式方法的贪心算法,取得了一定的效果。

- Holmes, Sherwani 和 Sarrafzadeh把空闲引脚导通以增加布线资源。以下是示意图。右图中,第二层某些引线穿过了空闲引脚进行布线。(第二层是纵向的,一三层横向)

6.6 现在详细路由中所面临的挑战(Modern Challenges in Detailed Routing)

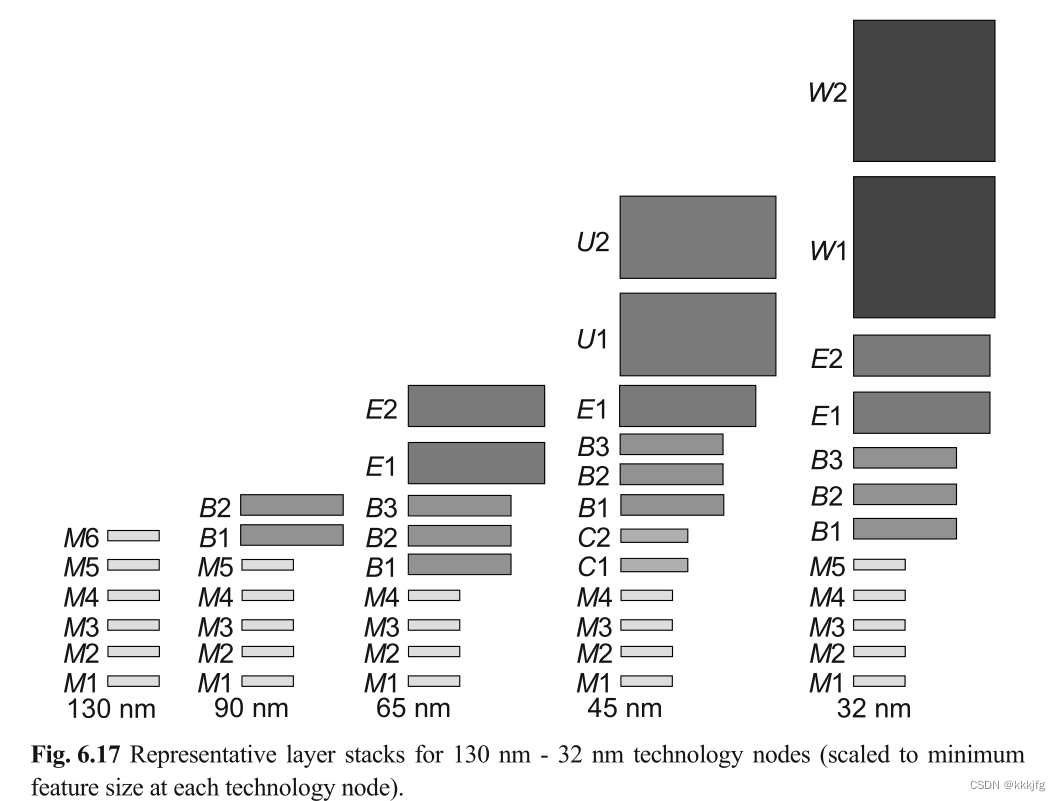

由于导线宽传输速度会更快,在现在的高性能低功耗需求下,出现了不同宽度的金属层,然后有人会用宽金属层传递时钟信号和进行跨全局不同区域的互联。这种混用不同宽度金属层的设计也有助于使得芯片越做越小的同时保证性能。

以下是IBM不同芯片制程下的几种金属层宽度方案。可以看到不同层的宽度厚度很不一样,其中,W,C, B, E, U和W的宽度比是1 : 1.3 : 2 : 4 : 10 : 16。这种配置也带来了挑战,比如,不同宽的金属层之间连接是用的适应宽层的大通孔,大通孔会填充一个金属棒下来与窄层接触,但这个直径对于窄层来说可能过于巨大,比如可能比导线间距还大,这样光是这个通孔金属棒就会占掉一大片位置,挤占路由资源。至于为什么不用多个小通孔连接呢?我问了chatgpt,他说:

“你提出的这个想法在某些情况下是可行的,但通常并不是最优选择。这是因为在制造过程中,钻孔数量和大小可能会影响生产成本和制造效率。另外,如果使用太多的小过孔来连接不同宽度的导线,可能会导致信号干扰和噪声问题。这是因为过多的小过孔可能会形成电感和电容,从而影响信号的传输和稳定性。此外,使用大一些的过孔连接不同宽度的导线,可以使连接更加可靠,同时也可以减少设计中的一些不必要的复杂性。因此,在选择过孔的大小和数量时,需要综合考虑各种因素,并权衡各种利弊。”emm,挺有道理的。

另外,生产过程中,还会遇到许多挑战,比如通孔会失效,导线可能会开路,短路等等,以下列举了一些:

通孔缺陷(Via defects)

通孔在生产中可能会发生偏移,导致永久在此芯片留下电子迁移效应(electromigration effects ), 若电阻增加可能会导致时序冲突,若失败则还可能改变电路功能。一种防范方法是多打几个孔,但多打孔会多消耗资源,在拥挤区域尤其难办,所以也不是所有通孔都能加倍打。

多打孔这一步可以由商业布线器或者使用独立拓展工具做。

互联缺陷(Interconnect defects)

电路连接的时候会发生开路或者短路的缺陷。防短路的办法有,把线隔远点布置,但这样会增加线长,且增加开路风险。防开路的办法有多连线,即不仅仅用树形结构对网络各点进行连接,但这样又会增加短路风险。

多加线这一步往往在后处理步骤中做。

天线缺陷(Antenna-induced defects)

这个缺陷很拗口,感觉直接这么翻译这个“Antenna-induced defects”也很奇怪,或许可以叫做“天线效应导致的缺陷”?

这种缺陷通常发生在集成电路的制造过程中。它是由制造过程中的等离子体刻蚀引起的。在这个过程中,金属线路未连接到PN结节点的其他部分可能会因为某种原因聚集电荷并冲击PN结,当电荷通过栅氧化物(如 S i O 2 SiO_2 SiO2)放电时,会对晶体管栅产生不可逆的损坏。

为了防止这些天线效应,详细的布线器会在设计时就调整金属线路和栅极的比例。具体来说,如果一个栅极没有连接到漏极/源极,我们将严格限制连接它的金属多边形的面积(可以理解为没做好的二极管不能连到太多带电导线上,怕给导通整坏了)。

当违反这些天线规则时,最简单的解决方法是通过新的或换位置的过孔将一部分路径传输到更高的层。”

一些研究人员提出了考虑到了制造可行性的布线器,其中详细布线过程显式地优化产量。然而,在制造之前很难客观地量化这种优化的好处。因此,这些技术尚未在行业中得到广泛应用。

文章深入介绍了电子设计自动化(EDA)中的VLSI物理设计,特别是详细布线阶段。内容涵盖水平和垂直约束图、通道布线算法如左侧边算法和狗腿布线,以及交换盒布线和单元上布线(OTC)。文章还讨论了现代详细路由面临的挑战,如不同宽度金属层的管理、通孔缺陷和天线效应导致的缺陷。

文章深入介绍了电子设计自动化(EDA)中的VLSI物理设计,特别是详细布线阶段。内容涵盖水平和垂直约束图、通道布线算法如左侧边算法和狗腿布线,以及交换盒布线和单元上布线(OTC)。文章还讨论了现代详细路由面临的挑战,如不同宽度金属层的管理、通孔缺陷和天线效应导致的缺陷。

2127

2127

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?