1. 前言

eMMC有多种速率模式,主要根据如下几个方面进行划分:

- single rate or dual rate

- I/O电压

- BUS宽度

- 支持的clock频率范围

- 最大的传输速率

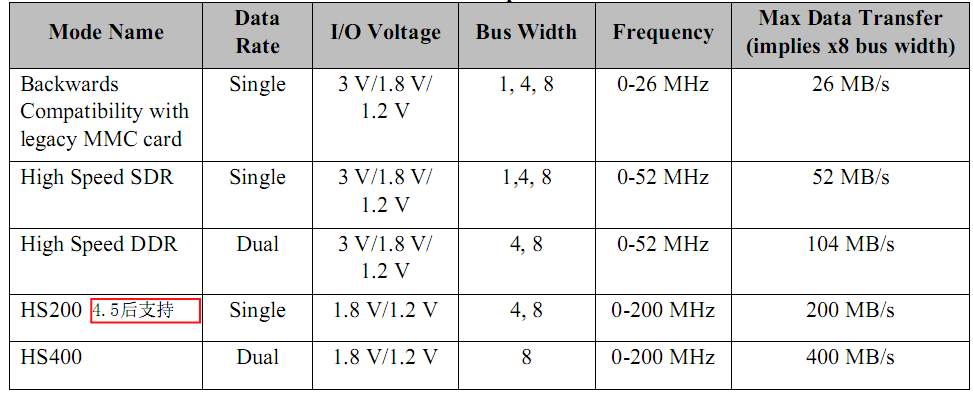

2. 概览

图 BUS speed的多种模式

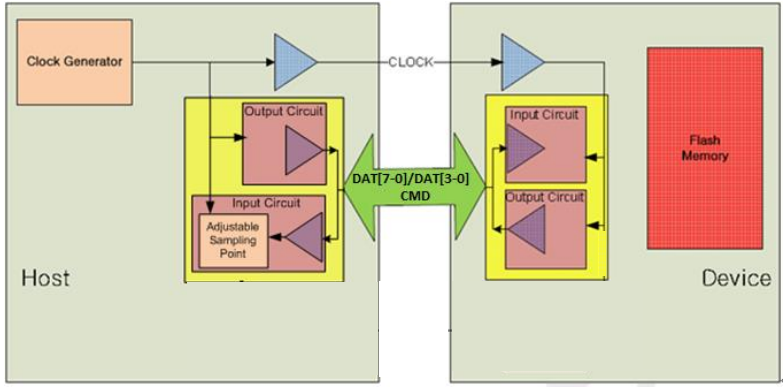

3. HS200总线速率模式

图 HS 200 host and device block

读时host需要校准获取合适的采样点以可靠的接受数据,方法见spec 5.3.5

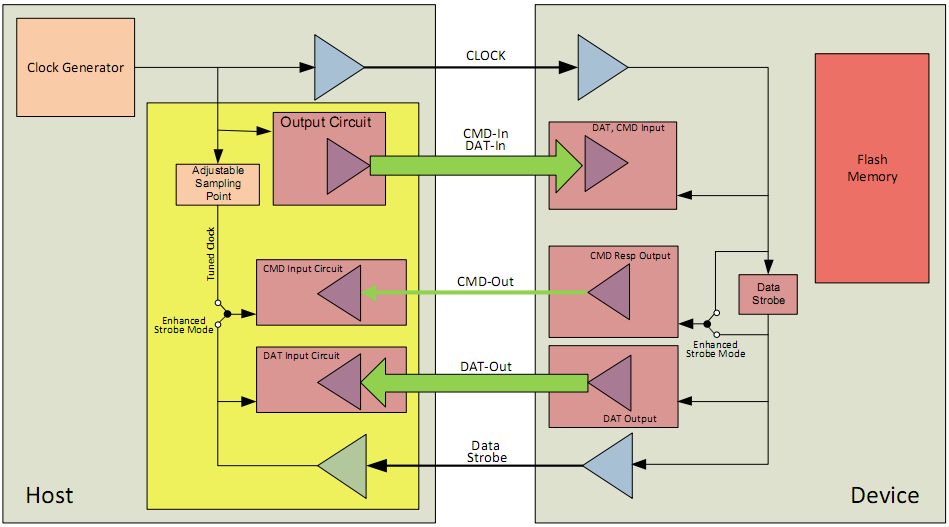

4. HS400总线速率模式

图 HS 400 host and device block

数据读时,device端会发送data strobe信号,主要用于接收端做数据同步信号使用,data,crc,response必须与data strobe边界对齐,这样host端可以参考data strobe信号,调整数据采样点,就可以保证接收数据的准确性。

data strobe一般只会用在ddr速率模式。

5.参考文档

[1] http://www.jedec.org/sites/default/files/docs/JESD84-B51.pdf

607

607

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?