ADRV9009-定义:一个收发器芯片。

1.驱动方式

分Linux驱动和裸机,此处附上差别。

参考:https://blog.csdn.net/qq_21438461/article/details/130868609

2.linux驱动下给出的例程

linux驱动下:

–https://github.com/analogdevicesinc/adrv9009-zu11eg-fan-control-daemon

这是一个用于控制 ADRV9009-ZU11EG 系统模块上的风扇速度的程序。

High-level API:API是指应用程序编程接口?

IIOD Server:linux系统下为ADC/DAC提供支持的系统

3.ADI官方的hdl程序和no-os驱动

在github能下载到,hdl程序要求的对应的vivado版本在readme文件的require里,需要确认。

4.cpack-wiki介绍

该内核从ADC接口“收集”样本并将其传递给DMA(或任何其他接收模块),数据流由ADC控制。通过一些例子可以最好地解释这一点。我们考虑一个通道数据宽度为32位的4通道ADC。当有效通道被置位时,ADC内核在其输出端为所有通道提供两个16位样本。在本例中,DMA 接口是交错的 8 个样本(128 位)流。这是因为无论ADC通道数据宽度如何,软件始终将数据视为“样本交错”。通道宽度为128位或16位的DMA内核可以接收相同的数据集。

官方其他答疑中写道: The pack/upack cores just help optimize the bandwidth to the DDR based on the enabled channels.

目前的进展是没看懂cpack ip下的pack_shell。

4.1pack_shell程序读取

这个程序的主要作用是???暂时没看懂

| 英文名 | 解释 |

|---|---|

| prefix_count_s | prefix_count的暂存版,被用于累加可用端口 |

| ce | 输入信号 |

| ready | ce与reset_data取反 |

| reset_data | 每次被选信道改变时外部状态都会重置一次,控制路径是流水线的且会提前一个时钟周期计算。如果渠道数大于2,则需要两个startup_cycles。只有一个渠道时不需要startup cycle,2个渠道时需要一个startup cycle |

| reset_ctrl | 如名 |

| enable_int | 内部使能信号 用于检测信道选择时的变化并在此时重置内部状态 |

| enable_count | 可用信道数-1 |

| rotate | 用作输入数据向量的偏移量的参数。当没有所有样本都被启用时,可能需要多个周期才能消耗完输入向量。rotate指向输入向量中应该下一个被消耗的第一个样本。例如,当有4个通道,但只有2个被启用时,rotate会在0和2之间摆动。如果有4个通道,其中3个被启用,它将在序列0、3、2、1之间循环。 |

| ce_ctrl | 时钟使能 |

| samples_enable | 考虑了每信道采样点数的enable信号,位宽为采样点数 |

| prefix_count | 在该通道前的禁用赛道数 |

| num_of_samples | 信道数乘每个信道的采样点数,即总的采样点数 |

| sync | 指示第一个启用通道是否在第一个输出样本中。如果启用的通道数量是 2 的幂,那么这个描述总是成立。 |

always @(prefix_count_s[i]) begin 即一旦prefix_count_s[i]变化,则会触发begin开始

4.2 ad_perfect_shuffle

洗牌程序。在这个程序中完成数据交织。

在完美洗牌中,输入向量被分成 NUM_GROUPS 个组,每个组包含 WORDS_PER_GROUP 个元素。

输出向量由 WORDS_PER_GROUP 个组组成,每个组有 NUM_GROUPS 个元素。数据被重新映射,以便输出向量中第 j 个组的第 i 个元素是输入向量中第 i 个组的第 j 个元素。

- Examples:

- NUM_GROUPS = 2, WORDS_PER_GROUP = 4

-

[A B C D a b c d] => [A a B b C c D d] - NUM_GROUPS = 4, WORDS_PER_GROUP = 2

-

[A a B b C c D d] => [A B C D a b c d] - NUM_GROUPS = 3, WORDS_PER_GROUP = 2

-

[A B a b 1 2] => [A a 1 B b 2]

4.3.pack_network

data信号是直接接到这个pack_network的。内含pack_ctrl和pack_interconnect

4.4.pack_ctrl

这个模块的作用是根据特定的全局旋转和输出的前缀计数来确定如何配置多路复用器的控制位。

| 名称 | 意义 |

|---|---|

| port_address_width | 端口地址宽度,指代输入端口数量。如果是2的话就有4个输入端口 |

| mux_order | 多路选择器级联阶数,比如说想要8:1就级联两个4:1,阶数就是2 |

| min_stage | 多路选择器的最小阶数,以免有多层级 |

| num_stages | 多路选择器的级别数 |

输入信号为rotate和prefix_count,输出ctrl信号连到pack_interconnect

4.5 pack_interconnect

受到pack_ctrl控制。连接(interconnect)不同模块或单元的结构或技术。

送进来的ctrl信号跟乘法器相乘后变为一个七位信号,与接地信号合为一个32位信号,同时与输入数据一起进行位选择BSEL,输出一个16位信号。所以ctrl是为了分信道?

四个位选择后合成一个64位信号,再送进一个洗牌程序,最后输出

互连模块由 NUM_STAGES 个阶段组成。每个阶段由多个多路选择器(MUXs,每个端口一个)和一个完美洗牌器组成。

每个多路选择器的输入数量为 。

端口的数量为 。

乘法器中,S端代表选择,决定了哪个输入被输出。

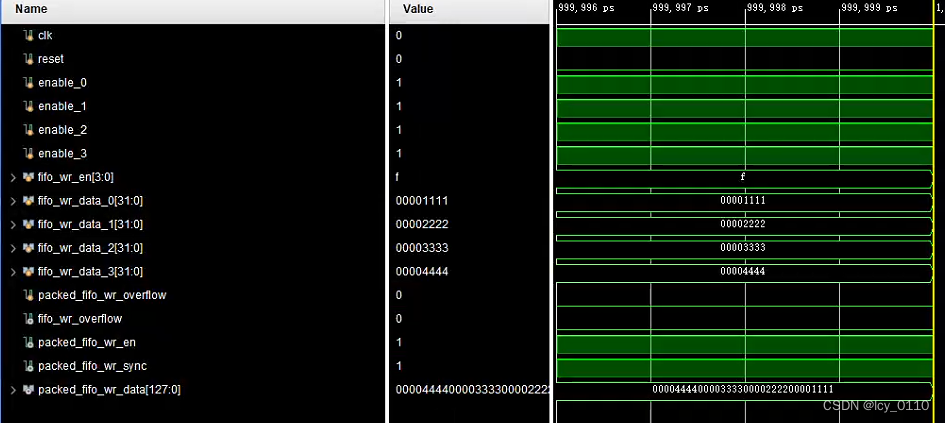

👉仿真可见在输入为16bits数据时 输出为4444333322221111

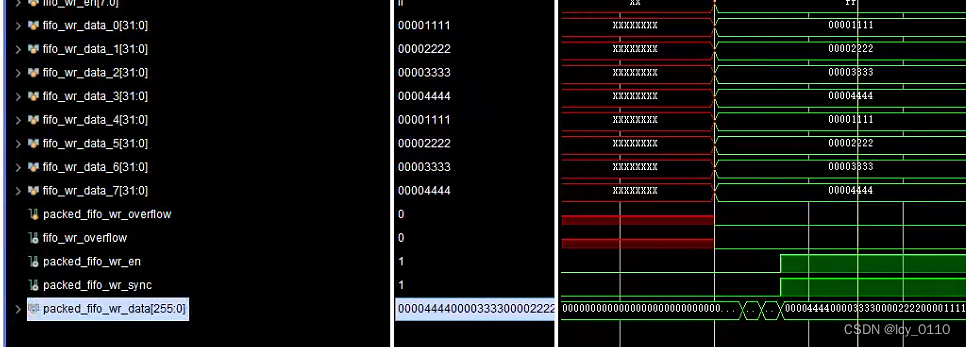

输入8通道32位数据时,也是倒序排列的,没有交织。

以下是单独新建了一个只含cpack的工程然后仿真的

4通道32位数据时,使能四个信道

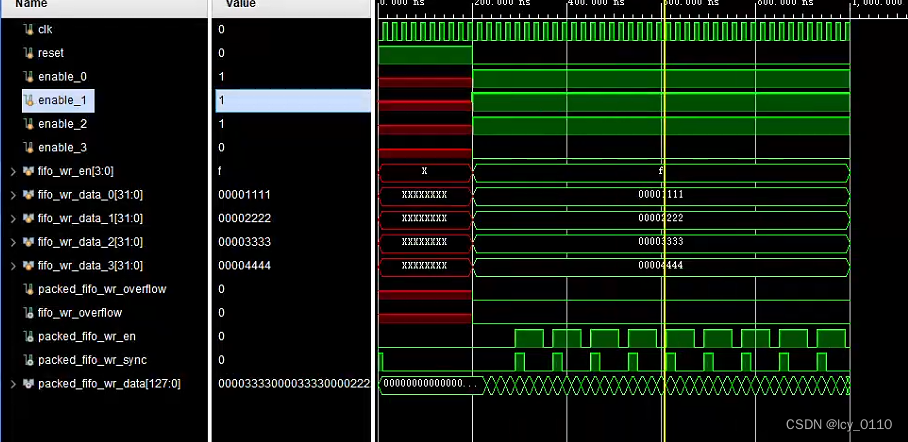

使能3个信道 4‘b1110

输出数据轮流:01030201 02010302 03020103 此处每位数字代表4位相同数字

理论输出应该是21000321 03210003 00032100

暂时不确定为什么会这样

914

914

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?