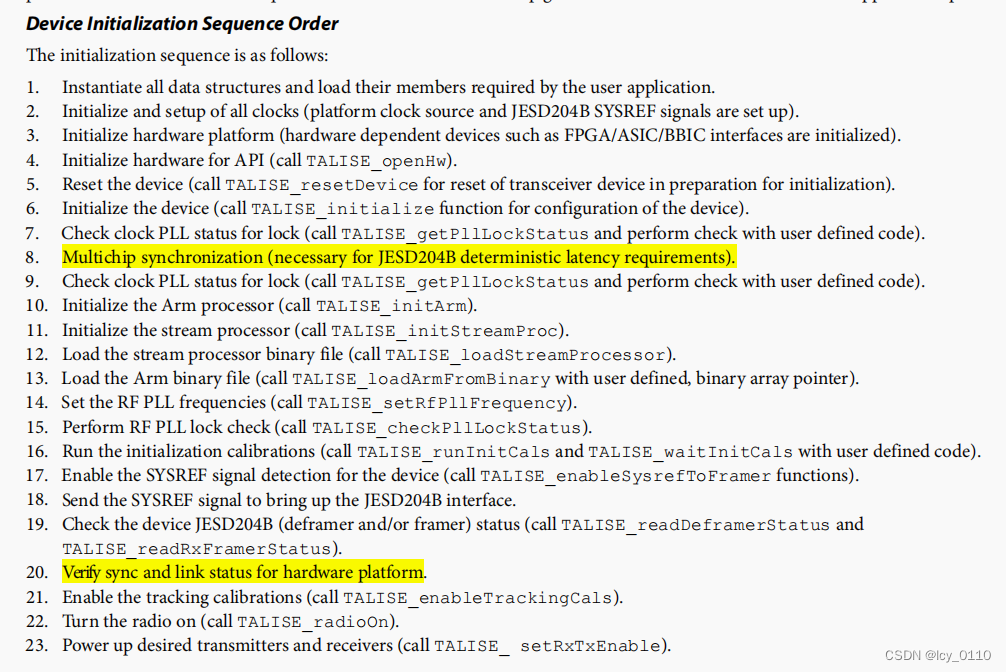

该.C文件主要完成了talise_setup,跟9009官方提供的顺序逻辑完全一致。

本篇主要探讨JESD204B Framer有关程序。即第17步开始。

首先是Enable Talise JESD204B Framer,仅以RX为例。在talise_config.c中给出结构:

/* JESD204B settings */

.jesd204Settings =

{

/* Framer A settings */

.framerA =

{

.bankId = 1, /* JESD204B Configuration Bank ID -extension to Device ID (Valid 0..15) */

.deviceId = 0, /* JESD204B Configuration Device ID - link identification number. (Valid 0..255) */

.lane0Id = 0, /* JESD204B Configuration starting Lane ID. If more than one lane used, each lane will increment from the Lane0 ID. (Valid 0..31) */

.M = 4, /* number of ADCs (0, 2, or 4) - 2 ADCs per receive chain */

.K = 32, /* number of frames in a multiframe (default=32), F*K must be a multiple of 4. (F=2*M/numberOfLanes) */

.F = 4, /* F (number of bytes per frame) */

.Np = 16, /* Np (converter sample resolution) */

.scramble = 1, /* scrambling off if framerScramble= 0, if framerScramble>0 scramble is enabled. */

.externalSysref = 1, /* 0=use internal SYSREF, 1= use external SYSREF */

.serializerLanesEnabled = 0x03, /* serializerLanesEnabled - bit per lane, [0] = Lane0 enabled, [1] = Lane1 enabled */

.serializerLaneCrossbar = 0xE4, /* serializerLaneCrossbar */

.lmfcOffset = 31, /* lmfcOffset - LMFC offset value for deterministic latency setting */

.newSysrefOnRelink = 0, /* newSysrefOnRelink */

.syncbInSelect = 0, /* syncbInSelect; */

.overSample = 0, /* 1=overSample, 0=bitRepeat */

.syncbInLvdsMode = 1,

.syncbInLvdsPnInvert = 0,

.enableManualLaneXbar = 0 /* 0=auto, 1=manual */

},

/* Framer B settings */

.framerB =

{

.bankId = 0, /* JESD204B Configuration Bank ID -extension to Device ID (Valid 0..15) */

.deviceId = 0, /* JESD204B Configuration Device ID - link identification number. (Valid 0..255) */

.lane0Id = 0, /* JESD204B Configuration starting Lane ID. If more than one lane used, each lane will increment from the Lane0 ID. (Valid 0..31) */

.M = 2, /* number of ADCs (0, 2, or 4) - 2 ADCs per receive chain */

.K = 32, /* number of frames in a multiframe (default=32), F*K must be a multiple of 4. (F=2*M/numberOfLanes) */

.F = 2, /* F (number of bytes per frame) */

.Np = 16, /* Np (converter sample resolution) */

.scramble = 1, /* scrambling off if framerScramble= 0, if framerScramble>0 scramble is enabled. */

.externalSysref = 1, /* 0=use internal SYSREF, 1= use external SYSREF */

.serializerLanesEnabled = 0x0C, /* serializerLanesEnabled - bit per lane, [0] = Lane0 enabled, [1] = Lane1 enabled */

.serializerLaneCrossbar = 0xE4, /* serializerLaneCrossbar */

.lmfcOffset = 31, /* lmfcOffset - LMFC offset value for deterministic latency setting */

.newSysrefOnRelink = 0, /* newSysrefOnRelink */

.syncbInSelect = 1, /* syncbInSelect; */

.overSample = 0, /* 1=overSample, 0=bitRepeat */

.syncbInLvdsMode = 1,

.syncbInLvdsPnInvert = 0,

.enableManualLaneXbar = 0 /* 0=auto, 1=manual */

},

/* Deframer A settings */

.deframerA =

{

.bankId = 0, /* bankId extension to Device ID (Valid 0..15) */

.deviceId = 0, /* deviceId link identification number. (Valid 0..255) */

.lane0Id = 0, /* lane0Id Lane0 ID. (Valid 0..31) */

.M = 4, /* M number of DACss (0, 2, or 4) - 2 DACs per transmit chain */

.K = 32, /* K #frames in a multiframe (default=32), F*K=multiple of 4. (F=2*M/numberOfLanes) */

.scramble = 1, /* scramble scrambling off if scramble= 0 */

.externalSysref = 1, /* externalSysref 0= use internal SYSREF, 1= external SYSREF */

.deserializerLanesEnabled = 0x0F, /* deserializerLanesEnabled bit per lane, [0] = Lane0 enabled */

.deserializerLaneCrossbar = 0xE4, /* deserializerLaneCrossbar */

.lmfcOffset = 17, /* lmfcOffset LMFC offset value to adjust deterministic latency */

.newSysrefOnRelink = 0, /* newSysrefOnRelink */

.syncbOutSelect = 0, /* SYNCBOUT0/1 select */

.Np = 16, /* Np (converter sample resolution) */

.syncbOutLvdsMode = 1,

.syncbOutLvdsPnInvert = 0,

.syncbOutCmosSlewRate = 0,

.syncbOutCmosDriveLevel = 0,

.enableManualLaneXbar = 0 /* 0=auto, 1=manual */

},

/* Deframer B settings */

.deframerB =

{

.bankId = 0, /* bankId extension to Device ID (Valid 0..15) */

.deviceId = 0, /* deviceId link identification number. (Valid 0..255) */

.lane0Id = 0, /* lane0Id Lane0 ID. (Valid 0..31) */

.M = 0, /* M number of DACss (0, 2, or 4) - 2 DACs per transmit chain */

.K = 32, /* K #frames in a multiframe (default=32), F*K=multiple of 4. (F=2*M/numberOfLanes) */

.scramble = 1, /* scramble scrambling off if scramble= 0 */

.externalSysref = 1, /* externalSysref 0= use internal SYSREF, 1= external SYSREF */

.deserializerLanesEnabled = 0x00, /* deserializerLanesEnabled bit per lane, [0] = Lane0 enabled */

.deserializerLaneCrossbar = 0xE4, /* deserializerLaneCrossbar */

.lmfcOffset = 0, /* lmfcOffset LMFC offset value to adjust deterministic latency */

.newSysrefOnRelink = 0, /* newSysrefOnRelink */

.syncbOutSelect = 1, /* SYNCBOUT0/1 select */

.Np = 16, /* Np (converter sample resolution) */

.syncbOutLvdsMode = 1,

.syncbOutLvdsPnInvert = 0,

.syncbOutCmosSlewRate = 0,

.syncbOutCmosDriveLevel = 0,

.enableManualLaneXbar = 0 /* 0=auto, 1=manual */

},

.serAmplitude = 15, /* Serializer amplitude setting. Default = 15. Range is 0..15 */

.serPreEmphasis = 1, /* Serializer pre-emphasis setting. Default = 1 Range is 0..4 */

.serInvertLanePolarity = 0, /* Serializer Lane PN inversion select. Default = 0. Where, bit[0] = 1 will invert lane [0], bit[1] = 1 will invert lane 1, etc. */

.desInvertLanePolarity = 0, /* Deserializer Lane PN inversion select. bit[0] = 1 Invert PN of Lane 0, bit[1] = Invert PN of Lane 1, etc */

.desEqSetting = 1, /* Deserializer Equalizer setting. Applied to all deserializer lanes. Range is 0..4 */

.sysrefLvdsMode = 1, /* Use LVDS inputs on Talise for SYSREF */

.sysrefLvdsPnInvert = 0 /*0= Do not PN invert SYSREF */

}

对应

talAction = TALISE_enableFramerLink(pd, TAL_FRAMER_A, 0);

if (talAction != TALACT_NO_ACTION) {

printf("error: TALISE_enableFramerLink() failed\n");

goto error_11;

talAction = TALISE_enableSysrefToFramer(pd, TAL_FRAMER_A, 1);

if (talAction != TALACT_NO_ACTION) {

printf("error: TALISE_enableSysrefToFramer() failed\n");

goto error_11;

}

}

此处结构为

uint32_t TALISE_enableFramerLink(taliseDevice_t *device,

taliseFramerSel_t framerSel, uint8_t enable)

先unable再enable?该函数指定帧生成器A/B的控制 定义了帧生成器A,则函数通过写入SPI操作来设置帧生成器A的链接状态。

TALISE_enableSysrefToFramer:启用或禁用TALISE设备中指定帧生成器的Sysref信号,会根据FRAME_A/B选择不同的地址。

重复完成FRAMERA/B的以上两个设置,再重复完成DeframerA/B的设置,再进入第十八步,发送SYSREF

ADIHAL_sysrefReq:此处设置sysref的发送模式。

随后使能jesd_lane_clk,并复位CDR,最后关闭SYSREF。此处代码注释提示:插入用户的JESD204B同步验证代码(?

Check Talise Deframer Status

确认解帧、成帧状态。

warning: TAL_FRAMER_B status 0x2F

我的报错是在这里出现的。且单步调试仍然会出现这个错误。

错误原因是:SYSREF phase error ,a new SYSREF had different timing than the first that set the LMFC timing.

目前困惑的是这个SYSREF状态?为什么会出现phase error,且感觉这个phase error不影响我后面的程序,已在频谱仪上看到tx。

该怎么调呢

而且在这里send sysref以后主程序再次sysref_cont_on?

6317

6317

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?