在高速或高频电路板中,PCB中的寄生效应非常明显,这些寄生电容和寄生电感会引起串扰、EMI、信号完整性等问题。在处理高频、高速和混合信号PCB时,需要做一些特殊处理,以减小寄生效应对信号的影响。

为了减小寄生电容和电感的影响,我们需要知道它们是怎么产生的,才能对症下药。本节我们先来了解如何计算PCB的寄生电容和寄生电感,然后讨论如何减小它们的影响。

PCB上的导体一般有走线和过孔(焊盘、覆铜等都可以等效为走线),二者的结构完全不同,所以我们在讨论寄生效应时,需要把这两种结构分别分析。

1)寄生电容

信号线/焊盘的寄生电容:

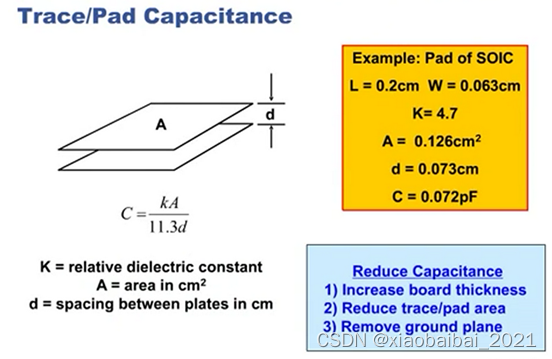

我们知道,平板电容器的电容计算公式为:C=ε0*S/d;其中ε0是介电常数,S是相对的两个平板的面积,d是两个平板的距离。可以知道,在介电常数一定的情况下,正对的面积S越大、距离d越小,则电容越大。

由于在PCB的同一层上,信号线与信号线之间等效的正对面积很小,距离相对于相邻层之间的间距也很大,所以,同一层内的走线之间的寄生电容认为很小可以忽略;把走线覆盖的面积当作平板电容器的面积,相邻层的间距作为平板电容器的间距,忽略掉其他因素引起的小电容,寄生电容的产生就可以简化为平板电容器的电容。

可以如下图计算:(A为面积、d为与相邻参考层的间距,例子中K=4.7是把PCB板材的介电常数考虑进去了)

从这个计算公式可以看出,如果想要减小信号线、焊盘的寄生电容,在设计PCB时,一是要减小铜皮覆盖的总面积;二是要增加层间距(在实际操作时,可以选用层间距大的PCB层叠结构,或者挖空相邻层的参考面)

过孔的寄生电容:

过孔的寄生电容,不能等效成平板电容器,一般用以下公式计算:

(其中D1为过孔的外径、D2为过孔周围铜皮挖空部分的圆直径、T为PCB厚度、εr为板材的相对磁导率)

从以上计算公式可以看出,要想减小过孔的寄生电容,需要使用小孔径的过孔、加大过孔和铜皮的间距、选用更薄的PCB板材。

2)寄生电感

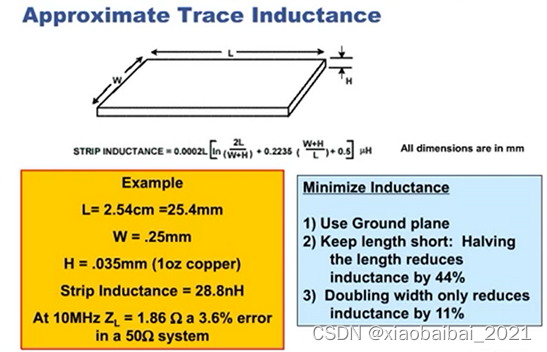

信号线/焊盘的寄生电感

计算方法如下:(W是线宽、L是线长,H是铜厚)

这个公式看起来比较复杂,实际上,对寄生电感影响最大的是线长L,将L的长度缩短是减小信号线寄生电感的最有效方法。

过孔的寄生电感:

计算方法如下:(h是板厚、D是过孔直径)

从公式上可以看出,要减小过孔的寄生电感,需要减小板厚、增大过孔直径。

好了,本节的内容就分享到这了。

如果觉得有用,欢迎大家关注我的微信公众号,有更多学习资源分享:

1104

1104

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?