什么是PCB寄生电容?

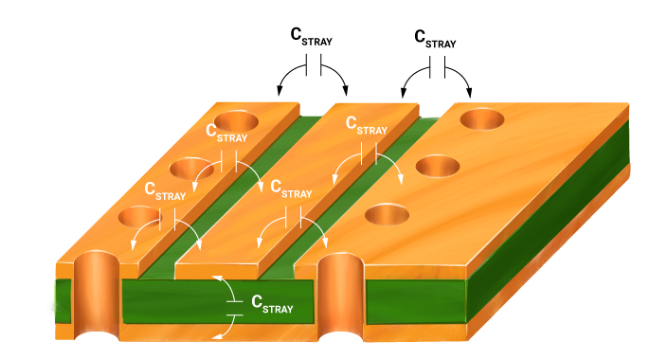

寄生电容是存在于由绝缘体隔开的两个导电结构之间的虚拟电容,是PCB布局中的一种效应,其传播的信号表现为电容,但并不是真正意义上的电容。

寄生电容有什么影响?

在高速或高频电路板中,PCB的寄生效应非常明显,容易引起串扰、EMI、信号完整性等问题。因此在处理高频、高速和混合信号PCB时,需要做一些特殊处理,以减少寄生电容对信号的影响。

- 当传输线有频带限制时,在非常高的频率下回产生低通滤波器行为。

- 不同电位地之间的噪声耦合,容易导致共模噪声

- 噪声或信号耦合到组件中,尤其是绕线电感

- 高频电容串扰(表现为FEXT和NEXT)

- 由于电源层和接地层之间的间距而导致的PDN阻抗修改

- EMI耦合到散热器中,产生共模电流

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?