电容的理解

众所周知,采用电容去耦是解决电源噪声问题的主要方法。这种方法对提高瞬态电流的响应速度,降低电源分配系统的阻抗都非常有效。因此,理解电容的工作原理对设计好电源系统具有重要的作用。

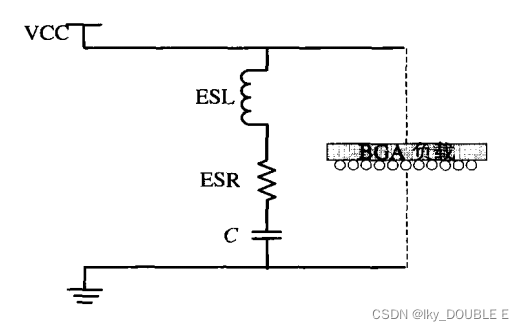

如下图所示,是电容在实际电路中使用的等效模型。当负载电流不变时,其电流由稳压电源部分提供,即图中细线所示的电流流动方向。此时电容两端电压与负载两端电压一致,电容两端存储一定数量的电荷,其电荷数量和电容本身的容量有关。当负载电流发生瞬态变化时,供电系统必须在极短的时间内为负载芯片提供足够的电流,但是稳压电源模块是无法快速响应负载电流的变化的。因此,负载芯片电压会降低,而也正是由于负载的电压发生瞬间变化,使得位于负载芯片周围电容上的电压也发生了变化,对于电容来说电压变化必然产生电流此时电容对负载放电,其电流大小由电容公式决定:

从公式中可以看出,只要电容量C足够大,即使很小的电压变化,电容也可以提供足够大的电流,满足负载瞬态电流的要求。这样就保证了负载芯片电压在容许的范围内变化。电容在这里所表现的功能是大家所熟悉的,即电容作为储能元件,在负载需要的时候释放能量,储能电容的存在使负载快速动作所消耗的能量得到及时补充,因此保证了负载两端电压不至于有太大变化,此时电容担负的是局部供电电源的角色。

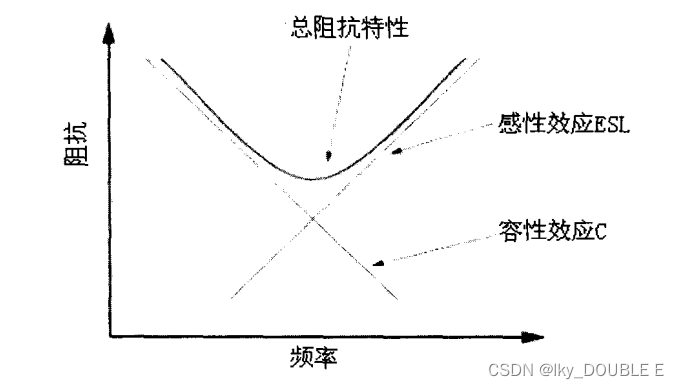

从储能的角度来理解电源去耦,非常直观易懂,但是对于设计高速稳定的电源分配系统,需要更加全面地了解电容特性。理想电容在实际中是不存在的,由于制造和封装的现实条件,电容中必定会存在等效电感ESL和等效电阻ESR,如下图所示,这些等效参数,在频率较低的情况下,表现不是十分明显,通常可以忽略。但是对于高速电源分配系统而言,这些参数在高频下的作用比较显著,因此,为正确使用电容进行电源系统设计,需要进一步了解包含了所有物理参数在内的实际电容的频率特性。存在于电路中实际的电容器件所表现的应该是下图所示的模型。

对于上图所示的电容模型,其实际的阻抗为:

- 当频率比较低时,可以忽略

,此时电容表现出容性阻抗;

- 当频率比较高时,可以忽略

,电容表现出感性阻抗。因此,在高频电路中,电容器件实际上是“电感”器件;

- 而当

时,电容表现出纯阻性,而且此时的阻抗最小,该频率点就是电容的自谐振频率。

电容阻抗特性随频率变化的曲线如下图所示。从图中可以看出,自谐振频率点是区分电容是容性还是感性的分界点,高于谐振频率时,电容器件不再是容性器件,去耦作用将下降,而在谐振点附近电容的去耦作用最明显。因此,实际电容器件都有一定的工作频率范围,只有在其工作频率范围内,电容才具有很好的去耦作用,使用电容进行电源去耦时要特别关注这一点。寄生电感(等效串联电感)是电容器件在高于自谐振频率点之后去耦功能被削弱的根本原因。在实际的应用中,尤其要控制电容的寄生电感。

电容的自谐振频率值取决于它的电容值及等效串联电感值,使用时可查看相关器件手册,了解相关参数,确定电容的有效去耦频率范围。下表列出了AVX公司生产的不同封装形式的陶瓷电容的参数值。

| 封装 | ESL(nH) | ESR( |

| 0402 | 0.4 | 0.06 |

| 0603 | 0.5 | 0.098 |

| 0805 | 0.6 | 0.079 |

| 1206 | 1 | 0.12 |

| 1210 | 0.9 | 0.12 |

| 1812 | 1.4 | 0.203 |

| 2220 | 1.6 | 0.285 |

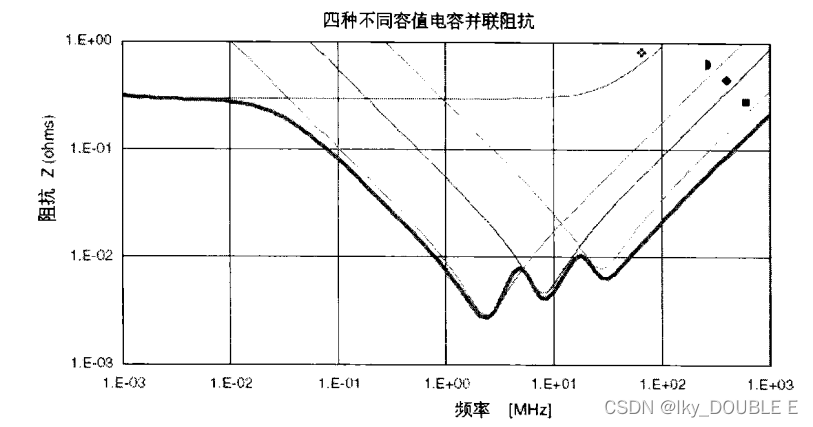

正是由于各种电容的容值和寄生参数不同,使得电容的谐振点不同。而在高速电路的电源系统设计中,正是利用了这一点特性,采用适当的不同容值的电容和数量配比,使得去耦网络总的阻抗降低。如下图的设计实例中,是采用470uF,2.2uF及0.022uF电容对电源系统去耦的阻抗特性,其综合效果如图中粗线所示。通过这种不同容值的电容配比,合理利用每类去耦电容的谐振点,可以使得总的去耦网络阻抗在一个很宽的频率范围内保持较低的阻抗值。目前数字电路中典型的去耦电容为0.1uF的去耦电容有5nH的分布电感,他的谐振频率大约在7MHz,也就是说对于10MHz以下的噪声有较好的去耦作用,对40MHz以上的噪声几乎不起作用。这也是很多工程师常犯的错误,为了简单省事,常常并列一堆0.1uF的电容,而忽略了不同种类电容的谐振配合效应。

SSN分析和应用

同步开关噪声SSN是Simultaneous Switching Noise的缩写,它实质上是由于功能部件的很多驱动端口进行同步状态切换而产生的一种感性噪声。

它的定义为:

式中,——同步切换噪声幅度,单位V;

N——同步切换驱动器数目;

L——单个驱动器对地连线等效电感;

I——每个驱动器瞬时电流变化。

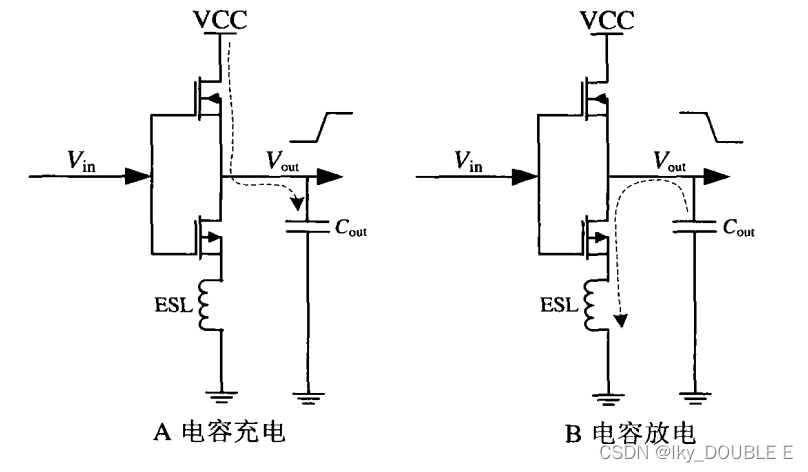

由于SSN和器件内部的一些物理特性相关,因此在系统级设计中,很难精确对其测量和控制。这里我们按照下图做一个定性的分析说明。

在A图中,驱动器输出高电平时,电源向电容充电;B图中,当驱动器输出为低电平时,

通过内部电路放电。假设,驱动器和地连线等效电感ESL=1.0nH。这是一个合理的经验值,大部分IC器件的引脚对地等效电感基本都在这个量级。同时,假设驱动器状态转化速度为50ps。在这段时间内,平均通过ESL的电流为10mA。这样,我们可以估算出在ESL上造成的压降为:

这样,当有10个这样的驱动器,共用一个接地引线,并且按照同样的切换速度进行状态切换,那么就会有:

这相当于把地电位额外增加了2V,如果这些驱动器的负载在这个时间内对进行采样,必定会造成信号的误判。这个SSN,通常也叫做地弹(Ground Bounce)噪声,SSN对地造成地弹噪声。同样,对于器件和电源之间的连接,也一样有引线电感存在,当多个I/O取代电路,同时要对外输出时,对于电源来将就会造成压降,电压对负载的瞬间供电需求会消耗在ESL上,而不能达到有效负载。因此,SSN对电源和地的影响分别称为Power Bounce和Ground Bounce,只是他们发生的时机和等效电路的不同,但其原理是一致的。

通过对SSN成因的分析,我们知道,在实际设计中,SSN是不可能彻底消除的,因为有电源引线存在就一定有SSN。虽然不能彻底消除,但是我们希望通过各种办法尽量减小SSN对信号质量的影响。

1.通过以上分析可知,SSN是共享电源/地的多个驱动器同时进行状态转换而引起的,并且这些状态的转换是以共模方式进行的,才会在电源引线上引起SSN,而如果这些驱动器的状态变化是差模方式,即有些驱动器从低到高,而另外一些驱动器从高到低变化,SSN的影响就不会很明显。因此,在系统设计中,对于关键信号,比如时钟Clock和采样Strobe信号,使用差分信号形式。差分信号的一对驱动器总是以相反的状态变化,即差模变化;而差分信号接收器靠差分信号的电平差触发,并且差分信号中的差模成分在接收端会形成虚地,不会有大量电流流入真正的地回路。因此,差分信号无论是对电源还是对地,都会大大减轻了负载要求。所以,差分信号不仅对本身的信号完整性质量有很大改善,同时也有助于维护良好的电源完整性。

2.既然SSN发生在共享一个电源回路的多个驱动器间,那么可以通过增加电源和地引脚的方式,来减小共享一个电源回路的驱动器个数,也就缓解多个驱动器同时动作时对电源的需求压力,从而有效减小SSN。

3.由于SSN发生在共享电源回路的驱动器之间,而这些共享电源回路的驱动器设计在芯片内部完成。因此,增大芯片的片内电容也是很有效地减小SSN的一种方法。增加片内电容,也就意味着增大了电源在芯片内的局部储能,可以有效地改善芯片内部的电源完整性,而不必把芯片内的电源供电需求再通过外部电源回路反映到外部连线上也就减小了ESL对供电的影响。

4.为了减小由于I/O驱动器产生的SSN对芯片内部逻辑的影响,在芯片的电源设计上,可以采用独立的I/O和核电源供电方式。这样不仅可以提高电源供电效率,减少芯片功耗,也可以有效防止核电源和I/O电源之间的相互干扰。事实上,这也正是目前很多大型芯片所采用的供电模式。

5.从系统设计角度出发,在芯片的外部,通过增加适当的去耦电容,并尽可能地靠近芯片供电管脚来改善芯片周围的电源局部完整性,是一种高效可行的方法。

6.从SSN产生的原因看,I/O驱动器瞬时对电源的需求变化,是引起SSN的一个重要因素。因此,如果能增大dt,也即减缓驱动器的上升沿和下降沿时间,同样也可以有效缓解电源压力,减小SSN。所以,在系统设计中,在满足系统整体性能需求的前提下,尽可能地使用较平缓的驱动信号,不仅可以减小信号本身的反射,提高信号质量,也可以有效抑制SSN。

以上,从芯片内部、外部,以及驱动信号本身的时间特性各角度,对减小SSN的各种可能的有效方法进行了分析总结,然而,不幸的是,对于系统设计者而言,上面减小SSN的方法中,除了方法5和方法6之外,其他方法都是在芯片内部设计时所采用的方法,在系统级是没有办法实施的。因此当确定芯片选型后,系统设计者根本不可能有机会在对芯片内部进行任何工作。所以,只有方法5和方法6,在芯片的外部,通过增加适当的去耦电容,尽可能地靠近芯片供电管脚来改善芯片周围的电源局部完整性,并尽可能地改变信号的时间特性,才是在系统设计这个级别上的可行方法。

7580

7580

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?