一、背景

FIFO是FPGA项目中使用最多的IP核,一个项目使用几个,甚至是几十个FIFO都是很正常的。通常情况下,每个FIFO的参数,特别是位宽和深度,是不同的。

明德扬(MDY)在2021年承担了多个基于XILINX芯片的研发项目,包括VPX网络透明传输项目(芯片为XC7K325T-2FBG900)、某高端测试仪项目(芯片为XCKU060-FFVA1156)、某网闸设备项目(芯片为XC7Z030-FBG676)等,另外,明德扬自研了基于XC7K325T-2FBG900和基于XC7K410T-2FBG900芯片的核心板,在XILINX研发领域拥有丰富的经验。

这些项目都必须用到FIFO。如果按照通常做法,每种位宽和深度的IP,都要打开FIFO IP核界面、命名(命名不好不好分辨需要的FIFO)、设置参数、生成并编译IP核,工作量可以想象出来是非常多的。更重要的是随之而来的管理问题,如何管理这几十个不同FIFO,如何检查FIFO的设置是否正确,都是一个不小的挑战。

对于我们专门承接项目的团队,绝不可忍受如此重复、枯燥、容易出错的工作。经过精心研究,终于找到了一条实用的方法:使用XILINX的原语--xpm_fifo_async和xpm_fifo_sync。

XILINX原语xpm_fifo_async和xpm_fifo_sync在FPGA中,可以直接例化使用,并且可以参数化FIFO的位宽和深度的。即在设计时,不用生成FIFO IP,直接例化就可以使用了。

二、获得参考代码

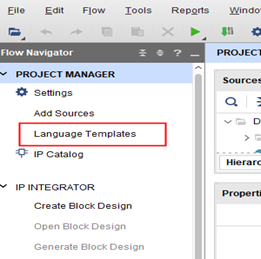

打开

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

329

329

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?