关于D触发器,d触发器在Verilog时序电路设计中是一个基本元件,多存在于单元库调用之中。dff可以形成4位移位寄存器,接下来进行一个简单的1bitd触发器的设计和仿真。

- 代码段

module dff(clk,data,q);//端口名定义

input clk;

input data;

output q;

reg q;

always @(posedge clk)

q<=data;//unblocking

endmoduleD触发器功能是在时钟上升沿到来之后将data传出。

`timescale 1ns/1ns

module dff_tb;

reg clk;

reg d;

//integer delay1;

wire q1;

dff4 U1(clk,d,q1);//模块调用

initial

begin

clk=1'b0;

repeat(20)

begin

// delay1=10*({$random}%5);

#10 clk=~clk;

end

end

initial

begin

clk=1'b0;

#20 d=1'b1;

#20 d=1'b0;

#20 d=1'b1;

#20 d=1'b0;

#20 d=1'b1;

#20 d=1'b1;

#20 d=1'b0;

#20 d=1'b1;

#20 d=1'b0;

#20 d=1'b1;

end

endmodule

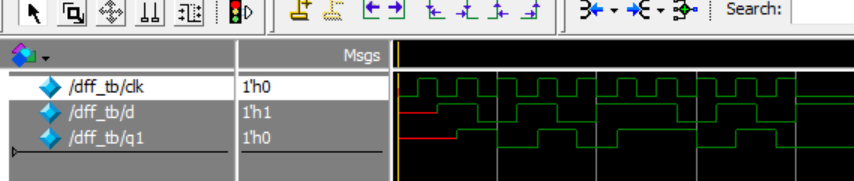

仿真时间200ns,由仿真结果可得dff是在上升沿到来之后把

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1197

1197

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?