此篇是我在学习中做的归纳与总结,其中如果存在版权或知识错误请直接联系我,欢迎留言。

PS:本着知识共享的原则,此篇博客可以转载,但请标明出处!

目录

[Labtools 27-3303] ---- FPGA vivado中报错,无法烧录bit

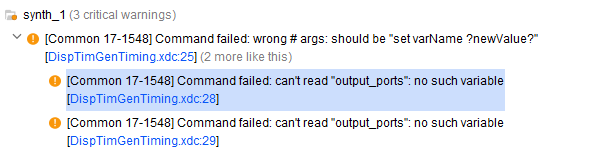

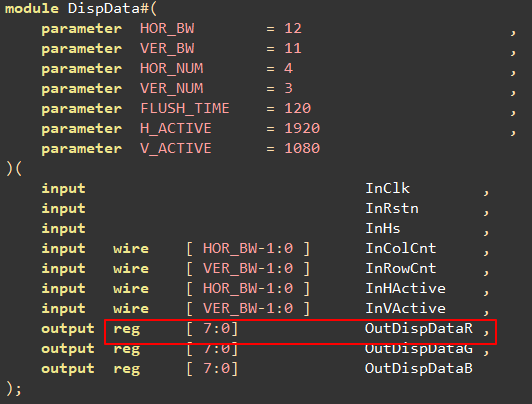

[Synth 8-685] variable 'OutDispDataR' should not be used in output port connection

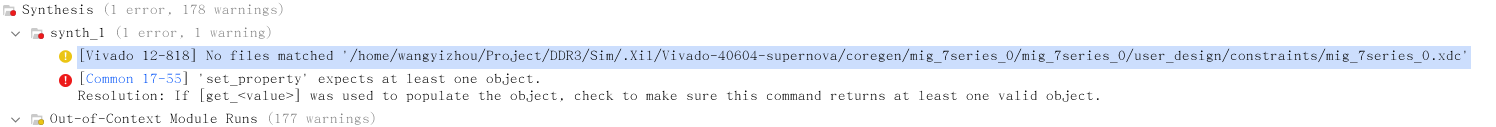

[Common 17-55] 'set_property' expects at least one object.

[Labtools 27-3303] ---- FPGA vivado中报错,无法烧录bit

Incorrect bitstream assigned to device. Bitfile is incompatible for this device.

原因:板卡型号不对,在Setting中选择新的板卡型号,是否改变sys,可以选择否,重新生成Bit即可。

[Synth 8-685] variable 'OutDispDataR' should not be used in output port connection

["E:/Vivado_Project/DispTimGen/DispTimGen.srcs/sources_1/new/DispTimTop.v":99]

原因在于:顶层设计中如果信号是从子模块输出,不能使用reg类型,应使用wire型

[Place 30-602] IO port 'InClk' is driving multiple buffers. This will lead to unplaceable/unroutable situation.

The buffers connected are:

u_DispTop/u_DispTimClk/inst/clkin1_ibufg {IBUF}

u_clk/inst/clkin1_ibufg {IBUF}

u_DataSource/u_DataSourceClk/inst/clkin1_ibufg {IBUF}

时钟从 IO 引脚 InClk 路由到三个Clk_IP核。 还告诉每个IP的时钟向导,“Source”是“Single ended clock capable pin”。 这导致问题的出现。

然后,在每个Clk_IP核的时钟向导中,指定 Clk_IP核“Source”为“No Buffer”。

[Common 17-55] 'set_property' expects at least one object.

Resolution: If [get_<value>] was used to populate the object, check to make sure this command returns at least one valid object.

IP核出错误 删除IP后重新添加IP .xci 文件

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?