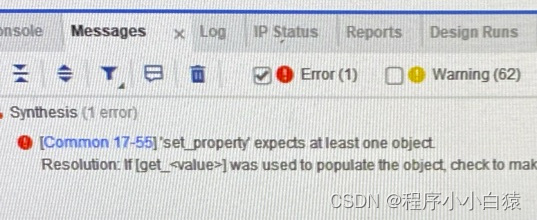

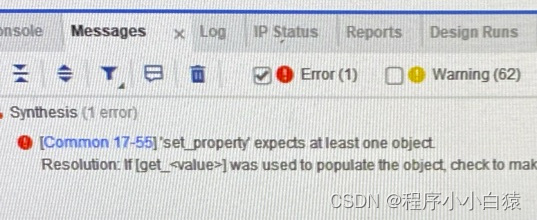

,不知道怎么解决,但是,把这个已经修改的核删掉,把工程路径下对应位置的这个核的信息都删掉,重新把这个核加进来,就不会有这个错误了

,不知道怎么解决,但是,把这个已经修改的核删掉,把工程路径下对应位置的这个核的信息都删掉,重新把这个核加进来,就不会有这个错误了

vivado的blockdesign设计的时候,如果有ip核更新了,点击updata后,编译的时候,会报错,

最新推荐文章于 2023-08-05 20:15:35 发布

,不知道怎么解决,但是,把这个已经修改的核删掉,把工程路径下对应位置的这个核的信息都删掉,重新把这个核加进来,就不会有这个错误了

,不知道怎么解决,但是,把这个已经修改的核删掉,把工程路径下对应位置的这个核的信息都删掉,重新把这个核加进来,就不会有这个错误了

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?