一、开发环境

1、vivado 2019.2版本 MIG 7Series (V4.2)

2、仿真时间:2020/07/24

二、过程记录

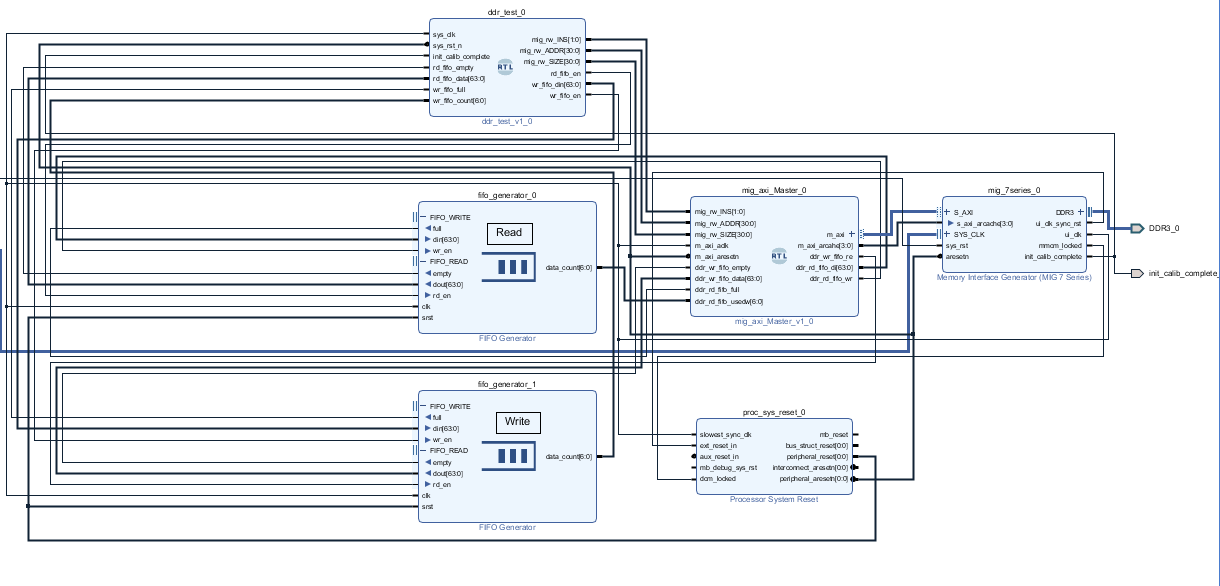

1、 首先是没有想过要仿真,上来就是创建block design原理图,然后就是设计整个工程电路,如下图:

图1 原理图

2、原理图包含MIG 控制器、AXI总线控制器、FIFO读写缓存、主逻辑控制器等模块。

3、原理图完成后,进行综合,看电路连线有无错误,无错误后进入下一步。

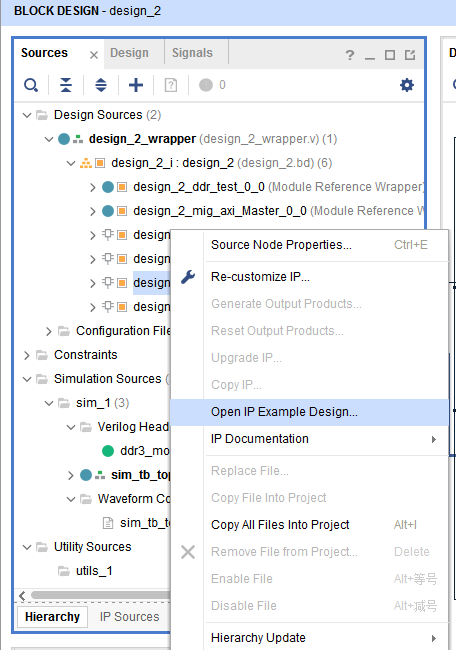

4、在vivado工具的Sources中找到mig 7series例化后的实体,然后右击,选择【Open IP Example Design...】如下图:

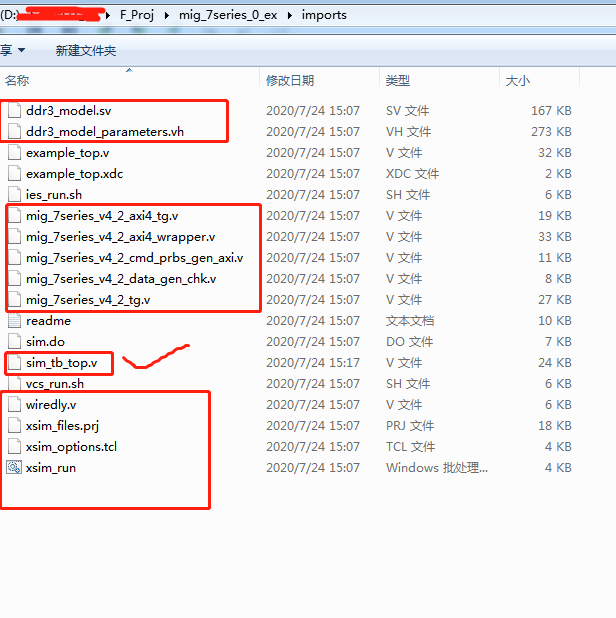

5、vivado工具会根据该mig实例新建一个参考案例,里面包含顶层的设计和测试平台和DDR的仿真库,如下图:

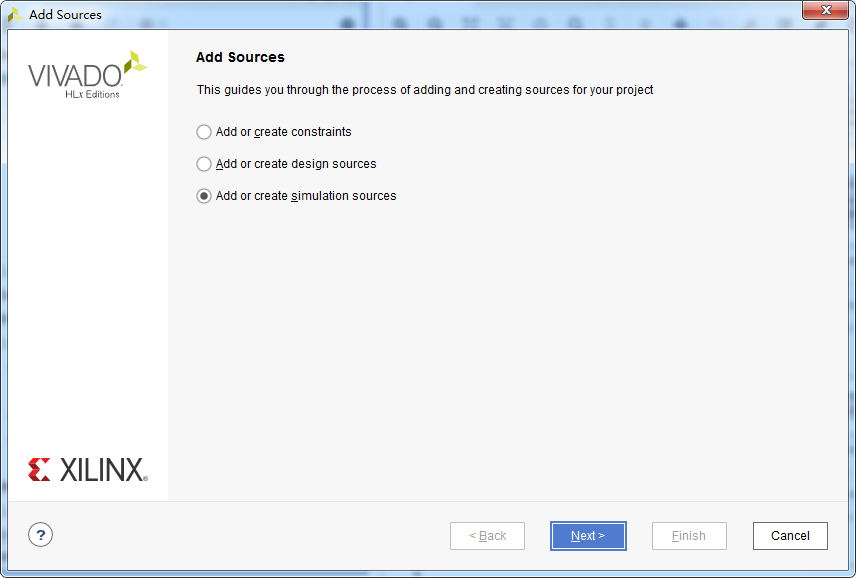

6、在你自己的工程根目录下,新建一个import文件夹,把上述文件全部拷贝到import文件夹下,然后工程导入sim_tb_top.v、wiredly.v、ddr3_model_parameters.vh三个文件。如下图:

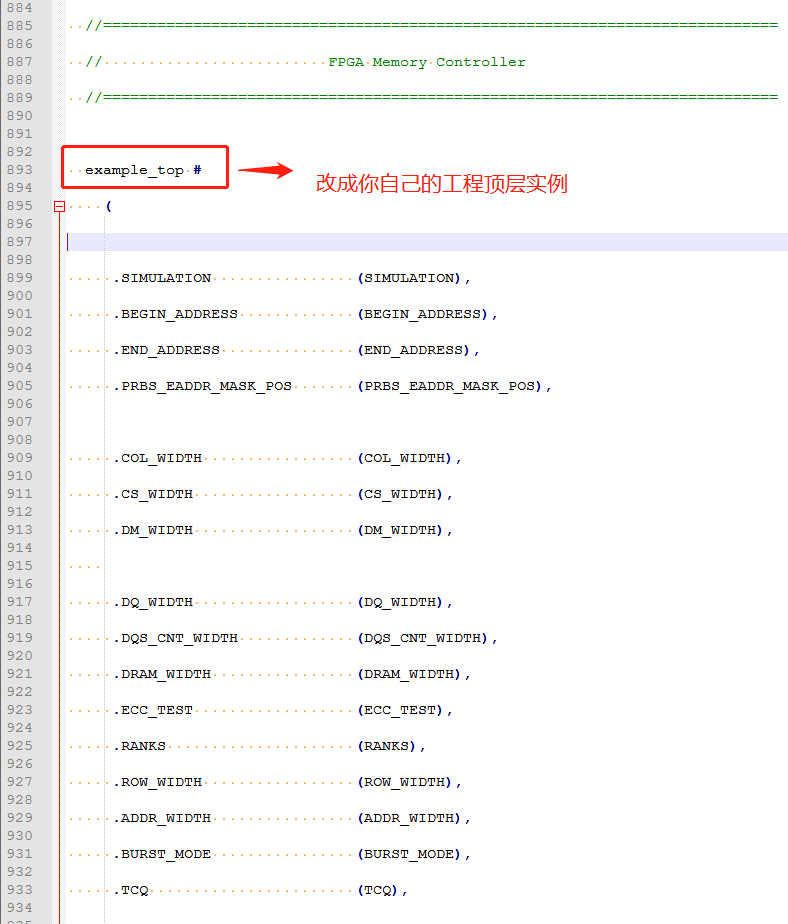

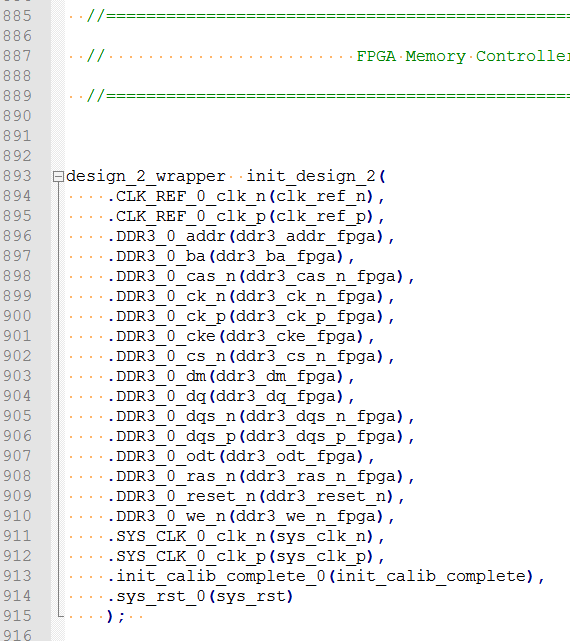

7、修改sim_tb_top.v文件,把其中example_top这个例化的实例改成你自己工程的顶层模块实例:

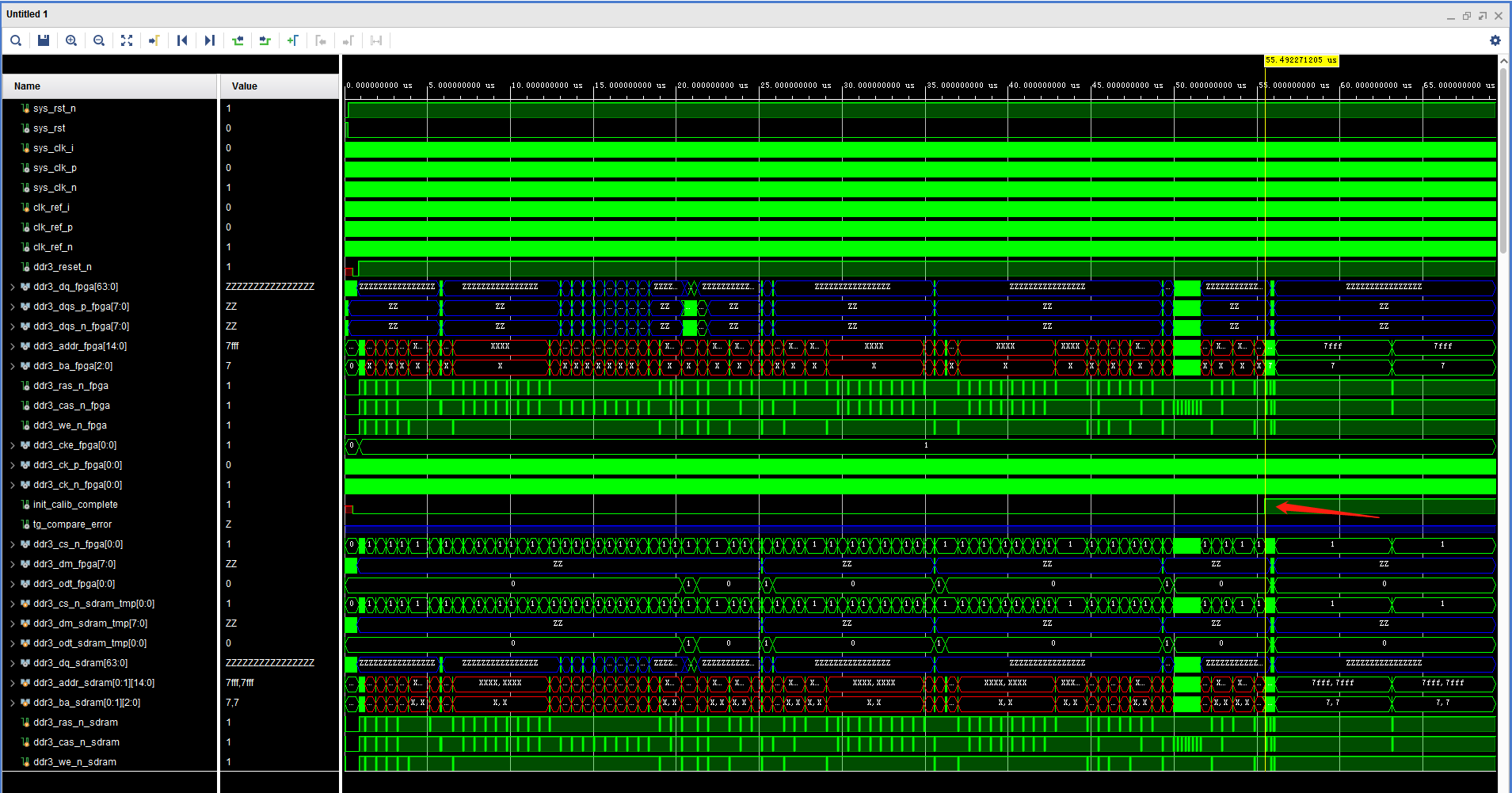

8、改完后,直接运行仿真,init_calib_complete信号拉高,表示初始化完成,如下图:

3138

3138

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?