这里只讨论数字电路里的双反相器式buffer,模拟运放型的Buffer不懂。

以前学的只记得buffer链用来插在长wire中以减小delay,还有放在大扇出逻辑中形成buffer tree来减小扇出,保证摆幅,减小延迟,也就是保证驱动能力了。

自己有个理解,但是讲起来还是绕,下面是各家的解释:

目录

1.数字电路的输入输出端加buffer的作用是什么?

一般认为有两个主要作用:

- 一是增大信号驱动能力;

- 二是做信号时序修整。

增大驱动能力简单理解就是可以让一个数字门后面可以挂更多的负载(扇出)而不至于失真,个人觉得信号恢复也可以算在这里面,就是当前一级信号由于种种原因而无法在电源和地之间满摆幅变化时,通过增大驱动能力来恢复满摆幅工作的能力。

信号时序修整包含了所谓的防止噪声干扰,和增加延时。

2.他和反相器的区别在哪啊?

从结构上说,数字的buffer一般就是偶数个反相器链的级联。从功能上说,buffer的输入和输出是同相的,而反相器自然是反相的。

3.增强驱动能力/减少连线负载/降低delay都是如何体现的?

当数据连线很长时,连线负载电容很大,导致存在很大的延时。此时插入buffer将连线分割成几个连线,每个buffer驱动的负载较小,因此能够有效减少延时,虽然buffer本身也具有延时,但是插buffer减少的连线延时明显大于buffer自身延时就可以采用插buffer的方式。

通过插buffer的方式减少了电路的负载电容,负载电容减少后,同样电压的情况下,对电容充电速度快(上升沿陡峭),同样电容小时存储的电容小,放电所需的时间短(下降沿陡峭)。一句话来说就是: 插buffer的方式减少了电路的负载电容,从而增大了电路驱动能力。

4. 确保信号时序正确

当一条wire很长时,延迟很大(delay正比于长度的平方,设长度为1,delay为1),这时在中间插入buffer,wire delay变为1/4+1/4=1/2,只要buffer delay小于1/2,则buffer的插入可以缩短wire delay。

当一条wire的延迟不大时,如果有hold violation(表现为数据到达过快,需要滞后到达),则插入buffer,利用buffer delay可以修正这个hold violation。

5. 增强驱动能力

什么是带负载能力

带负载能力是指,外接负载器件后,输出的电压或者电流不受影响的能力。比如,如果一个单片机的引脚输出5V的电压信号,如果接上一个负载后,它的5V保持不变,那么,它可以带动这个负载,如果变小,那就说明无法带动这个负载。同样,对于输出电流如果能够满足负载的需要,那就说明带负载能力满足要求。

这就告诉我们,在实际电路分析,首先你要看它的输出端是想稳定输出电流还是想稳定输出电压。

如果是想稳定输出电压,说它带负载能力强,表示其输出电阻比较小,如果是稳定输出电流,说它带负载能力强,表示其输出电阻比较大如果是想稳定输出电压,说它带负载能力强,表示其输出电阻比较小,如果是稳定输出电流,说它带负载能力强,表示其输出电阻比较大。

这得看所谓“buffer”的physical结构。path上插buffer实际上是output“放大”了input的驱动能力,其输入阻抗小,而输出阻抗大,因此概念上等价于:受被驱动单元输入阻抗影响相对小。可以减小电压转换时的transition time,眼图更完备。Buffer 的一个比较著名的模型是 logic effort

提高驱动能力

buffer是一种宽高比很大的mos管,宽高比大意味着电流大,驱动能力高。

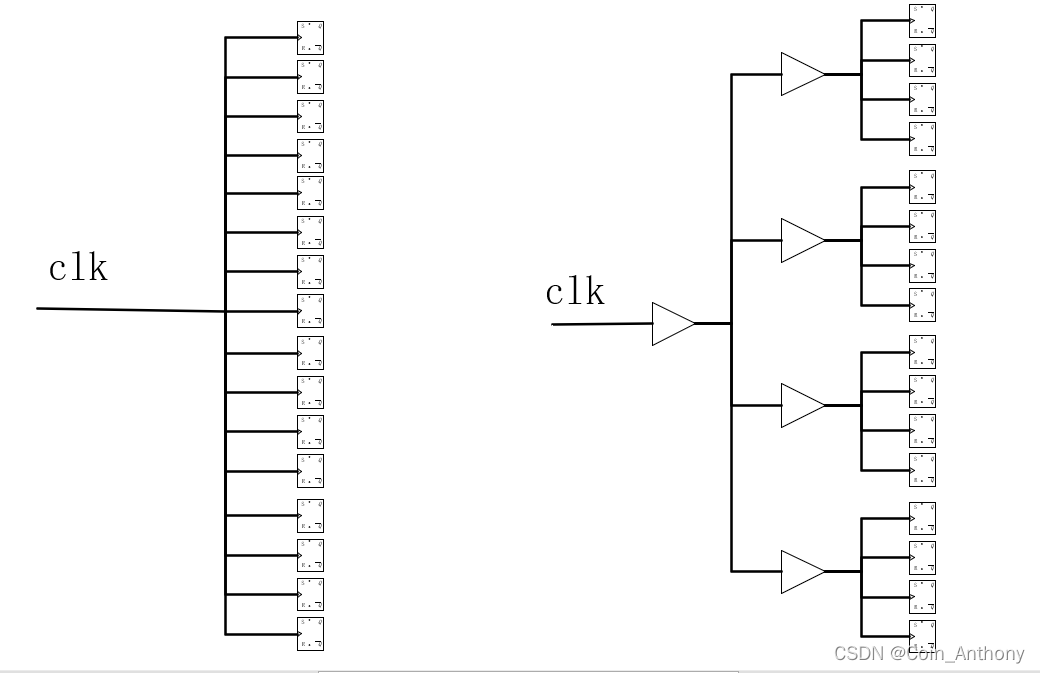

在扇出很大的wire中插入buffer可以提高带负载能力,常见于时钟树中。

时钟驱动16个reg时,负载很大,时钟上升很慢,并且时钟摆幅小,此时插入4个buffer。加buffer之前你的时钟直接驱动寄存器或者很多个寄存器。加buffer以后你的时钟只驱动buffer,而你的buffer会去驱动寄存器。时钟buffer本身是输入负载较小,输出驱动能力较强的。而且通常会做成一个时钟buffer网络来驱动设计里面全部的寄存器,并保证整个时钟网络上的信号有很好的transition,以及平衡从时钟源到所有寄存器的insertion delay.寄存器的CK端接在时钟上面, 在时钟上加入buffer是在做时钟树的时候让时钟到每一个寄存器的CK端的SKEW尽可能的小,还有增加驱动的功能。

驱动能力

所谓驱动能力,是指前级电路的输出信号可以使得后级电路有效响应,这个有效的包含两层意思:

- 第一是前级输出信号能被后级电路识别;

- 第二是在规定的时间内被后级电路识别。

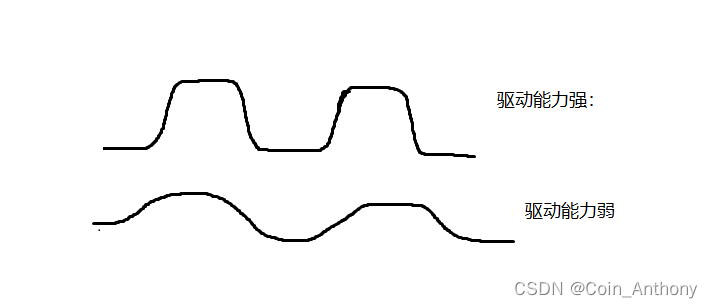

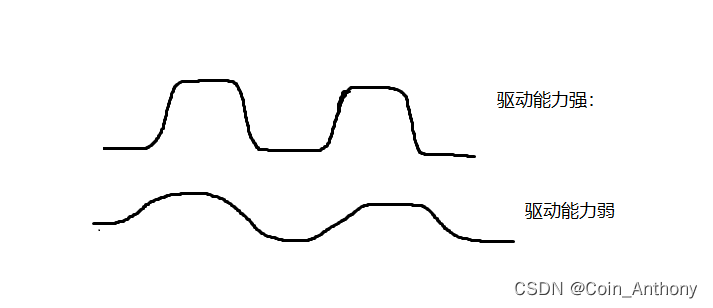

不插buffer会发生什么情况?不插buffer会导致驱动能力不够,通常是两种情况

第一种是输出电流不够,导致信号状态异常,这常常发生在后级电路对输入电流有要求的时候,另一种则是输出电流不够,导致信号上升下降沿太差,这常常发生在后级电路的输入电容较大的情况。

驱动能力强:摆幅大,上升快

驱动能力弱:摆幅下,上升慢

本文探讨了数字电路中Buffer的主要作用,包括增强信号驱动能力、时序调整和减少延迟。Buffer通过级联反相器实现,用于分割长线路负载,降低延迟并保证信号完整。此外,Buffer还能解决时钟树中的扇出问题,确保信号时序正确,提高带负载能力。

本文探讨了数字电路中Buffer的主要作用,包括增强信号驱动能力、时序调整和减少延迟。Buffer通过级联反相器实现,用于分割长线路负载,降低延迟并保证信号完整。此外,Buffer还能解决时钟树中的扇出问题,确保信号时序正确,提高带负载能力。

500

500

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?