目录

本文主要参考自2007届 西电 杨清宝 的**《嵌入式 SRAM 的高速、低功耗设计及优化》**硕士论文,知网下载。

版图设计步骤

整个版图的设计工作可以分为划分(partition)、布图规划 (floorplanning),布局(placement)、布线 (routing)和压缩 (compaction) 等几个步骤。

版图设计方法分类

版图设计的方法有很多种不同的分类,按照对布局布线位置的限制和对布局模块的限制分,可以把设计方法分成全定制( full-custom )和半定制 (semicustom)两大类。

全定制设计模式对模块和布局的位置没有限制,除了模块所占区域外其它区域都是布线区。对于有三层和三层以上的布线工艺来讲,模块上面也可用来走线,只是走线的层数有所限制,这样,就大大减小了芯片所需的面积。因此我们说全定制设计模式除了要遵循最基本的几何设计规则 ( 最小线宽、间距、覆盖、露头等 )外,没有任何其它附加的物理限制。

半定制设计模式则对于单元的高度、电源线位置和单元引线端的引出方向都有一定的限制,且单元只能放置在规定的区域内或必须按行放置。

半定制设计模式又可分成标准单元设计模式、门阵列设计模式、门海设计模式以及现场可编程门阵列。

版图设计完成后的验证工作

版图验证工作包括设计规则检查( Design Rule Check,DRC )、版图 & 原理图一致性检查( LVS )、版图的电路网表提取( Netlist Extraction,NET)、电学规则检查( Electrical Rule Checking,ERC )和寄生参数提取 ( Layout Parameter Extraction, LPE ) , 通过验证后的版图方可送去制作掩膜并用于芯片的

制造。

1.设计规则检查 (DRC)

设计规则检查是检查版图中各掩膜层图形的各种尺寸是否合乎设计规则的要求。

版图的设计规则是根据具体工艺线所能生产的最小图形尺寸、最细线条宽度及线条间的间距来确定的,是集成电路版图设计工程师和工艺师之间的桥梁。

在进行版图的设计规则检查时主要是针对两个方面进行检查的 :

- 同一层的几何图形的宽度及间距。

- 不同层图形之间的间距及套刻间距。

对于同一层的设计规则检查时,情况比较简单,只需进行最小尺寸及最小宽度的检查 ; 而对于不同层的套刻间距检查时,情况就比较复杂了。

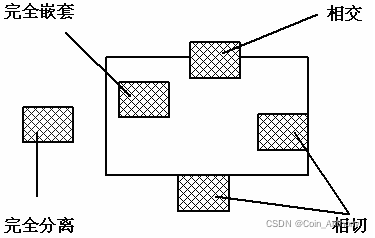

两个不同版图层的图形之间无非有四种关系 : 即完全嵌套、相交、相切及完全相分离。

图 4.3 不同层的几何图形之间的关系

我们需要根据不同层图形间的相互关系定义出 DRC 所需的虚拟层,因此有必要对各层的图形进行一定的逻辑操作 (AND, NOT, OR, SIZE) 。

然后按照设计规则对其进行相应的检查。

我们采用diva对所设计的版图进行检查。其具体操作就不在此详述。

2.版图与电路图一致性检查 (LVS)

LVS版图与电路图一致性检查 (LVS) 是把从版图中根据对器件与节点识别提取出的电路网表同原设计的电路网表进行对比检查,要求二者的节点与器件皆能一一配对。

如果二者不一致,其错误类型大体有两类 :

- 不一致点与失配器件。

- 不一致点分节点不一致和器件不一致。

节点不一致指版图与电路中各有一节点,这两个节点所连器件情况很相似,但又不完全相同。

器件不一致是指版图与电路中各有一器件,这两个器件相同,所接节点情况很相似,但又不完全相同。

失配器件是指有的器件在版图中有,但在原理图中没有,或在原理图中有而版图中没有。

在完成 LVS 后要根据检查结果所报告的各种错误,修改版图,直到二者在结构上达到完全的一致。

我们采用 dracula 对 SRAM 的版图进行了 LVS 检查,版图设计与原理图完全匹配。

3.电学规则检查(ERC)

什么叫电学规则呢?其实它的种类也不多,主要包括:

- MOS的gate不能直接连supply。

- cell input永远不能floating。

- 一个cell的driver最多一个,或者说output不能发生short。

- N/P区(衬底或阱)不能floating。可能还有别的,不过我目前只知道这四种了,可以先了解一下。

摘录自 电气规则检查-ERC

4.版图寄生参数提取 (LPE)

随着集成度的提高与器件尺寸的不断缩小,由版图寄生效应导致的芯片性能变差已经成为设计中所面临的一个主要问题。

为了准确把握寄生效应对芯片性能的影响,我们对 SRAM 的总体版图进行了寄生参数提取。

我们以上海中芯国际半导体有限公司提供的工艺参数为参照编写了相应的 LPE 文档,其中精确地定义了器件及连线的寄生电容。

版图寄生参数的提取不但为后仿真提供了更为真实有效的网表文件,也为我们电路修改工作提供了必要的参考信息。还有一点要注意的是版图寄生参数提取的宽和长有的可能是错的,因为一般情况下都是按照直栅来提取寄生参数的,那么在提取环栅寄生参数的时候就会出错。我们可以根据有关文献 [33]来计算出宽和长。

功能仿真(后仿)

版图画好后,由 LVS 在检查的同时也就提出了后仿真的网表,后仿网表与前仿网表不同之处是后仿网表有寄生电容和寄生电阻,而前仿网表只有管子的宽和长,没有寄生电容和寄生电阻,因此后仿数据要比前仿准确。

有了后仿真网表再结合 testbench( 测试向量 ) 就可以后仿了。

在进行后仿的时候可以用多种不同的方法来进行仿真,下面就介绍一下常用的几种方法。

1. 连写连读

先是连着写若干个信号,再一下子连着读出这些信号。检查这些被读出的信号和已经写入的信号是否一样,如果不一样就说明在数据写入时或在数据往外读时出现了错误。图 4.4 是按照地址顺着写的,也可以不顺着地址写,还有也不一定要把地址都写完了再读(如图 4.5 所示)。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Ig3Dj7sc-1648046484197)(en-resource://database/1616:1)]](https://i-blog.csdnimg.cn/blog_migrate/559081baf63ce58cca707dfb9fcc0e57.png)

2. 连续读写

在同一地址中完成先写后读的操作(如图 4.6 ),检查是否由错误存在。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-eBTn3CZ4-1648046484198)(en-resource://database/1618:1)]](https://i-blog.csdnimg.cn/blog_migrate/183666e4b00a776003e97b9cf41b8b29.png)

图 4.6 连续读写

3. 交叉读写

读操作和写操作交错进行(如图 4.7 )。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-WV4PcH2l-1648046484198)(en-resource://database/1620:1)]](https://i-blog.csdnimg.cn/blog_migrate/8a5e39c5f27e8a9e5efafb6c87cd92de.png)

图 4.7 交叉读写

4. march C+ 算法

march C+ 算法是使用非常普遍的一种方法

[1] 地址从最低到最高,写入全 0 ;

[2] 地址从最低到最高,读出全 0 ,写入全 1 ,并读出全 1 ;

[3] 地址从最低到最高,读出全 1 ,写入全 0 ,并读出全 0 ;

[4] 地址从最高到最低,读出全 0 ,写入全 1 ,并读出全 1 ;

[5] 地址从最高到最低,读出全 1 ,写人全 0 ,并读出全 0 ;

[6] 地址从最高到最低,读出全 0 。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-BLRMMXkc-1648046484198)(en-resource://database/1622:1)]](https://i-blog.csdnimg.cn/blog_migrate/f8d9fe0bf09e77a554730546d6cf9316.png)

在此我们用软件 Ultasim 进行后仿可得三种典型值。具体仿真图形

-

最快 FF –55 ℃ 1.89V

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-xmqFl5nB-1648046484198)(en-resource://database/1624:1)]](https://i-blog.csdnimg.cn/blog_migrate/e949f292caab0ba93b0f420d7a0480ed.png)

-

常温下 TT 25 ℃ 1.80V

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-4aTYb7pS-1648046484199)(en-resource://database/1626:1)]](https://i-blog.csdnimg.cn/blog_migrate/c2ba75a08482f2a3022c71bfa28c2615.png)

-

最慢 SS 125 ℃ 1.71V

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-qzIw91TG-1648046484199)(en-resource://database/1628:1)]](https://i-blog.csdnimg.cn/blog_migrate/ae747cdba8173bc16e15e81fb96ac63e.png)

经过三种典型环境下测定的数据可以得到三种典型值的后仿真数据(如表 4.4 所示),可以得知当存储器处于**最恶劣条件(即 SS 125 ℃ 1.71V )**下功能完好,写时间为 2.27 纳秒,读时间为 2.96 纳秒。说明能够满足时钟频率为133MHz 的要求。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-BuzIfxA2-1648046484199)(en-resource://database/1630:1)]](https://i-blog.csdnimg.cn/blog_migrate/a30f729663e7c8ca2b44e238047f6a22.png)

1785

1785

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?