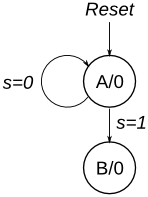

对题目要求的时序图和程序中用到的变量进行时序分析如下:

NUM变量为时钟计数器计数次数

ADDW为w为高的周期个数

Z为应有的输出

根据时序图编写程序如下

module top_module (

input clk,

input reset, // Synchronous reset

input s,

input w,

output z

);

parameter A = 0,B = 1;

reg state;

reg next_state;

reg [3:0] addw; //w为1的个数

reg [3:0] num; //计数器

always@(posedge clk)begin

if(reset)

state<=A;

else

state<=next_state;

end

always@(*)begin

case(state)

A:next_state = s?B:A;

B:next_state = B;

endcase

end

always@(posedge clk)begin

if(reset)begin

num <= 0;

end

else if((next_state == B)&&(num!=3))begin

num <= num + 1;

end

else if((next_state == B)&&(num==3))begin

num <= 1;

end

else begin

num <= 0;

end

end

always@(posedge clk)begin

if(reset)begin

addw <= 0;

end

else if((state == B)&&(num!=1))begin

addw <= addw+w;

end

else if((state == B)&&(num==1))begin

addw <= 0+w;

end

end

assign z = (num == 1)&&(addw == 2);

endmodule

63

63

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?