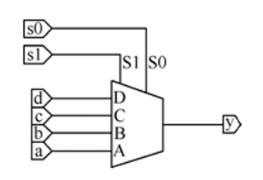

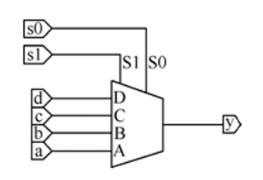

一、4选1多路数据选择器

原理图:

代码实现:

module MUX41(a,b,c,d,s1,s0,y)

input a,b,c,d;

intput s1,s0;

output y;

reg y;

always@(a,b,c,d,s1,s0)

begin

case({

s1,s0})

一、4选1多路数据选择器原理图:代码实现:module MUX41(a,b,c,d,s1,s0,y) input a,b,c,d; intput s1,s0; output y; reg y; always@(a,b,c,d,s1,s0) begin case({s1,s0}) 2'b00:y<=a; 2'b01:y<=b; 2'b10:y&l...

一、4选1多路数据选择器原理图:代码实现:module MUX41(a,b,c,d,s1,s0,y) input a,b,c,d; intput s1,s0; output y; reg y; always@(a,b,c,d,s1,s0) begin case({s1,s0}) 2'b00:y<=a; 2'b01:y<=b; 2'b10:y&l...

一、4选1多路数据选择器

原理图:

代码实现:

module MUX41(a,b,c,d,s1,s0,y)

input a,b,c,d;

intput s1,s0;

output y;

reg y;

always@(a,b,c,d,s1,s0)

begin

case({

s1,s0})

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?