VHDL的并行语句

①模块例化(component)

先声明在例化

②赋值语句

③进程语句(process)

④条件选择语句

when/else对应if/else

with/select/when 对应case语句

⑤generate语句

⑥procedure过程语句

⑦块语句(block)

⑧程序包(package)

VHDL的顺序语句

顺序语句只能出现在进程、过程和函数中。

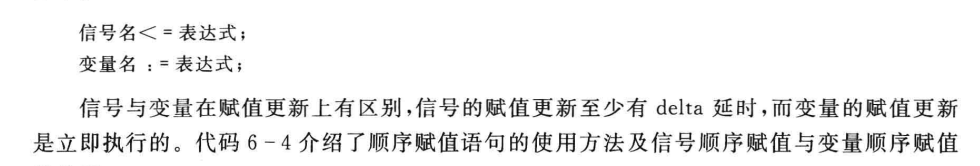

①顺序赋值语句

②wait语句有3种形式

wait for一般用于测试文件,综合工具一般不支持;另外2种不建议使用。

③after语句

④if语句

⑤case语句

如果没有优先级要求建议使用case语句生成数据选择器。

⑥loop循环语句

⑦exit语句和next语句

⑧return语句

基本概念

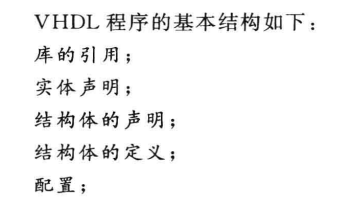

VHDL程序的基本结构

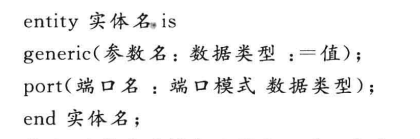

实体声明的一般格式

端口声明可隐含信号的意义。

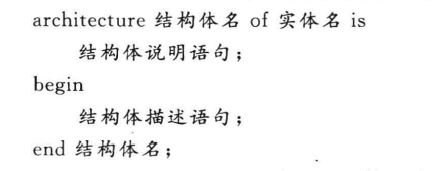

结构体的描述

标识符不区分大小写。

数据对象有4种。(常量、变量、信号、文件)

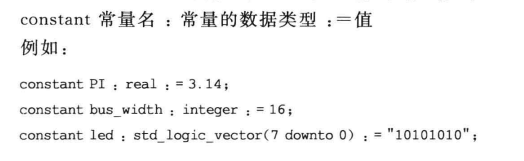

①常量(constant)

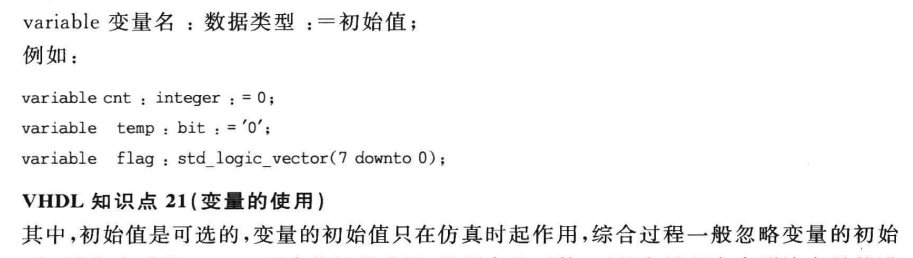

② 变量(variable)

变量的赋值是不需要延时的。

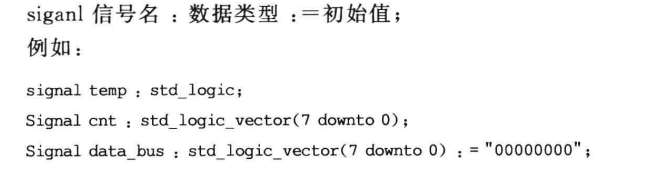

③信号(signal)

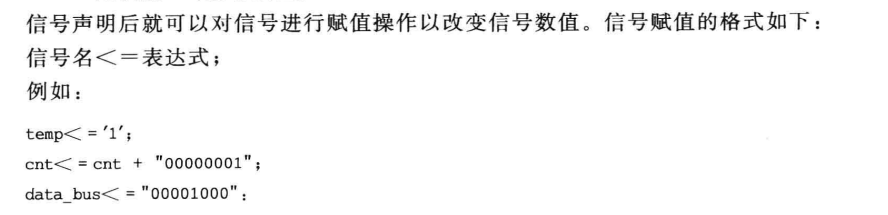

信号的赋值

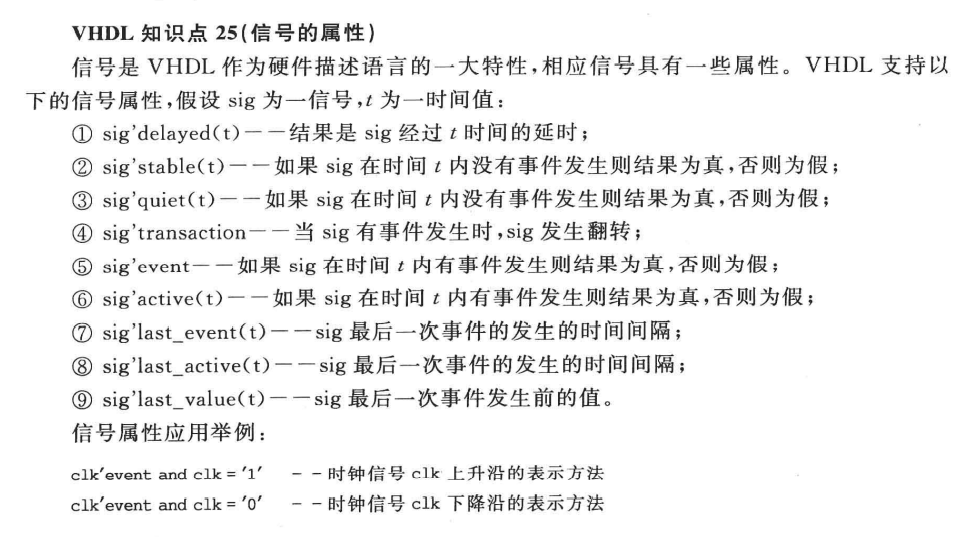

信号的属性

强数据类型语言。

标量的数据类型(整型、实型、枚举型)

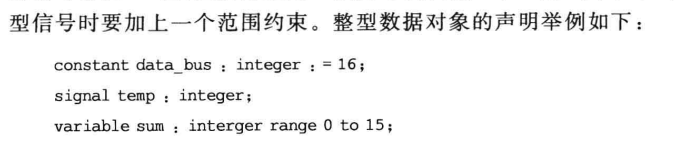

整型(integer)的声明

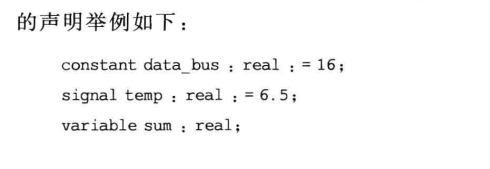

实型(real)

标量类型的属性

VHDL的操作符

5697

5697

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?