前言

学习单片机的时候,通过控制IO口的电平就能控制LED的亮灭,通过检测IO口的电平就能知道按键有没有被按下,同样是IO口操作,有没有什么不同?答案是肯定的,肯定有不同,控制LED的亮灭时,MCU是主动的,LED的亮灭是MCU说的算的。检测按键有没有按下的决定因素是外面的电路,按键按下与没按下,给IO口的电平逻辑是不一样的,MCU是被动的。也可以这么理解MCU主动控制IO口的电平逻辑,IO口就是输出模式,MCU被动检测IO口的电平逻辑,IO口就是输入模式。

STC89C52系列单片机的IO口结构

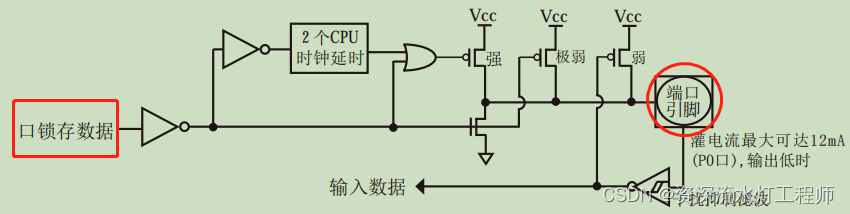

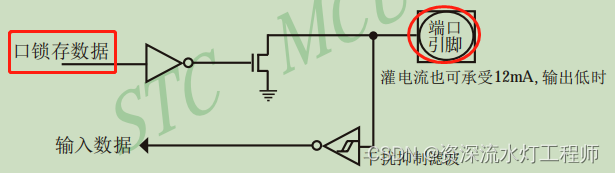

STC89C52单片机的IO口内部逻辑就是这个样子

看起来蛮复杂,是因为它是IO口,既可以用作输出模式,有可以用作输入模式,兼容的东西越多,结构就越复杂,那就需要一层一层的剥了。

首先要知道IO口相关的几个基础知识

传统的C51单片机的IO端口只有4组,分别是P0、P1、P2、P3;

STC89C52系列的单片机做了一些扩展,增加了一个P4端口;

STC89C52单片机的P1、P2、P3端口上电复位的时候就是准双向口状态,也可以叫弱上拉状态,既可以用作输入,也可以用作输出,你也不用特意的区配置它为输出模式还是输入模式了。

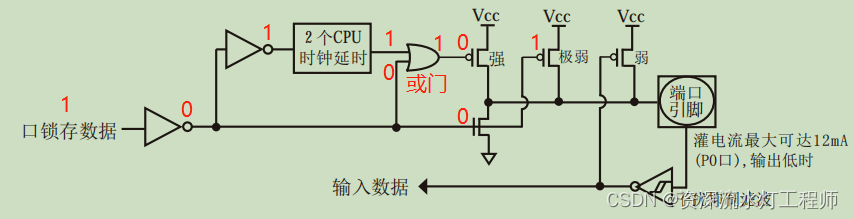

当口锁存器为1的时候,内部各模块的电平逻辑如下,

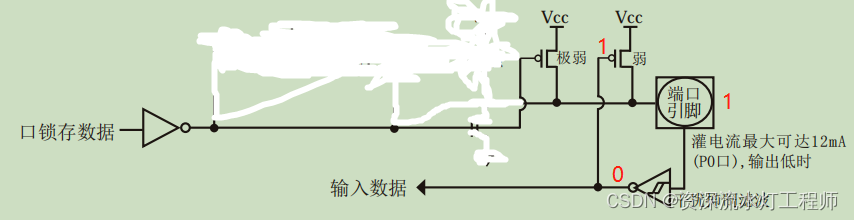

当口锁存器为1的时候,强上拉的晶体管的门极电平位0,不参与作用,只有极弱上拉和弱上拉在起作用,所以电路可以简化为

而弱上拉是否起作用还要看端口引脚此时的电平,如果此时外部的电路使端口引脚为高电平1的时候,弱上拉和极弱上拉才同时起作用,把端口引脚电平维持在高电平。

如果外部的电路使端口引脚为低电平,那弱上拉晶体管也就不能工作了,退出战场,只有一个极弱的上拉晶体管在支撑着,既然是极弱上拉,那就是没什么实力了,只要外面的电路强势一点(电流大一点)端口引脚的电平就是外部电路说的算了,它设置为低,端口引脚就是低电平,它设置为高,端口引脚就是高电平。

所以可以理解为,当口锁存数据位1的时候,就是MCU想把引脚设置为高电平,奈何实力太弱(驱动电流太小),能不能把端口引脚设为高电平还要看外面电路的脸色,此时的MCU就像一个没事实权的皇帝。

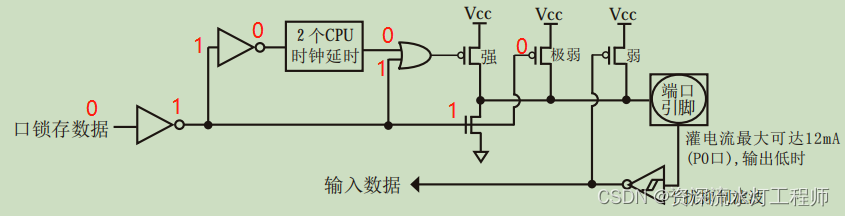

当口锁存数据设置为0的时候情况就不一样了,怎么个不一样,看看口锁存数据位0 时,各模块电平的状态

把没参与战场的清除掉,就靠内部的下拉晶体管将端口引脚拉低位低电平,那个极弱上拉没参与作用,这个下拉晶体管的能力就决定了MCU的实权了,如果有人说,即使MCU设置口锁存数据位0,我也用外面电路把端口引脚强行拉高(注入强电流),那后果是怎样?,那个下拉晶体管直接烧掉了,IO口就干废了,那还玩什么,有什么意思。

感觉那个强上拉晶体管就没做什么事一样,其实这个强上拉的作用只有当口锁存数据从0跳变到1的时候,可以是端口的引脚的电平快速变化,就这点作用。

所以可以得出一个结论了MCU将引脚设置为高电平的时候,驱动能力比较小,MCU将引脚设置为低电平的时候,驱动能力比较大。引脚设置为高电平,电平从引脚流出,就是拉电流,引脚设置为低电平,电平从引脚流入,就是灌电流,STC89C52单片机引脚的灌电流能力比拉电流的能力强。

所以LED电路,一般是将MCU的引脚与LED的阴极连接,用低电平去点亮LED,而不是引脚直接给给高电平点亮LED(虽然也能点亮)。

89C52单片机的P0端口端口可以用来内存扩展、上电复位后处于开漏状态,P00端口的内部结构如下图所示,没有那么多的上拉晶体管,所说的晶体管一般是MOSFET。P0端口默认设计是用来作为地址/数据复用的,内部就没有那么多的上拉,结构上简单很多,

什么是开漏状态,就是那个晶体管,也就是那个MOSFET,漏极什么也没有,就叫开漏;

如果把P0用作IO口,端口引脚的外面要加上拉电阻;

当口锁存数据为0的时候,晶体管导通,直接将端口引脚的电平拉低;

当口锁存数据为1的时候,晶体管不作用,端口引脚外面的电平由电路决定;

所以P0口用作逻辑输出的时候,端口引脚外要加一个上拉电路。

文章详细阐述了STC89C52单片机的IO口在控制LED和检测按键时的不同操作模式,强调了IO口在输出和输入状态下的电平逻辑差异。当口锁存器为1时,MCU试图保持高电平但受外部电路影响;为0时,MCU能有效拉低电平。P0端口默认为开漏状态,使用时需外接上拉电阻。

文章详细阐述了STC89C52单片机的IO口在控制LED和检测按键时的不同操作模式,强调了IO口在输出和输入状态下的电平逻辑差异。当口锁存器为1时,MCU试图保持高电平但受外部电路影响;为0时,MCU能有效拉低电平。P0端口默认为开漏状态,使用时需外接上拉电阻。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?