微信公众号上线,搜索公众号小灰灰的FPGA,关注可获取相关源码,定期更新有关FPGA的项目以及开源项目源码,包括但不限于各类检测芯片驱动、低速接口驱动、高速接口驱动、数据信号处理、图像处理以及AXI总线等

本节目录

一、扰码

1、扰码定义

2、扰码的作用

二、自同步扰码

1、自同步扰码器

2、自同步解扰器

三、同步扰码

本节内容

一、扰码

1、扰码定义

信源编码是根据实际的业务变换得到,没有传输方面的考虑,编码后的信号出现长串连“0”或连“1”序列是很常见的一种现象。因为这种信号无法提供充分的定时信息,会给接收端的解调造成很大困难。通常将信源编码器出来的数据进行随机化处理,改变原有数据序列的统计特性,使之具有伪随机特性,这就是扰码。

2、扰码的作用

采用扰码后,可以降低连“0”和连“1”序列的长度和概率,保证在任何情况下进入传输系统的码流中0、1的概率都能基本相等接近50%,改善位定时恢复的质量。

从信号功率谱的角度来看,扰乱过程相当于将数字信号的功率谱进行扩展,使其分散开来,因此扰乱过程又被称为“能量分散”,通过对信源编码器送来的数据进行随机化处理,改变原有数据序列的统计特性,使之具有伪随机特性。

3、扰码分类

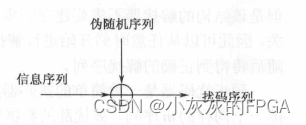

在通信加扰中,从扰码序列是否独立于用于加扰的伪随机序列来看,扰码可分为自同步扰码和同步扰码两种。一般伪随机序列由一个或多个线性反馈移位寄存器(LFSR)来产生。扰码关系图如下:

二、自同步扰码

自同步扰码器与解码器均是以LFSR为基础。

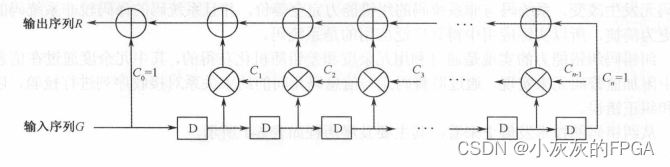

1、自同步扰码器

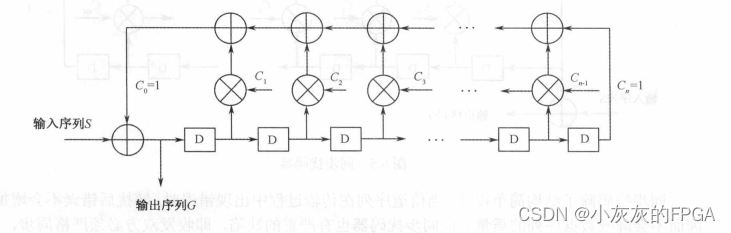

自同步扰码,在反馈逻辑输出与第一级寄存器之间引入异或逻辑,将得到的结果作为寄存器的输入,形成自同步扰码器。

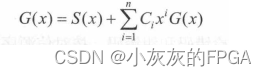

原始序列为S(x),经过扰码后的序列为G(x),扰码器的变化公式为:

自同步扰码器结构图如下:

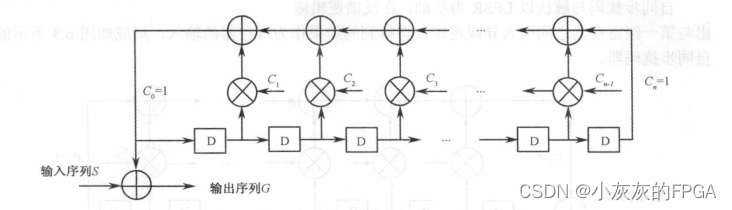

2、自同步解扰器

自同步解扰器需要采用不同的结构以完成相反的过程,如图6.4所示。这种结构可以从输入的加扰序列G中得到原始序列S。

自同步解扰器结构图如下:

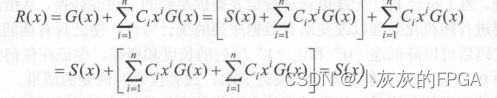

在自同步解扰过程中,伪随机序列的产生与输入序列有关,如果输入序列存在1位错误,将会在结果序列中造成最多n位(n为级数)出错,具体错误位数不大于解扰器的抽头个数。

自同步解扰器不需要建立同步,从解扰过程来看,由于解扰序列只与输入的扰码序列有关,因此可以从任意时刻开始进行解扰,除了输出序列中前n个比特受寄存器初始状态影响外,随后将得到正确的解扰序列。

三、同步扰码

同步扰码器是一种简单的扰码器,它把m序列加到数据序列上产生信道序列。

同步解扰器是信道序列减掉一个同样的m序列,被扰乱的数据序列就得到恢复。

同步扰码的加扰器和解扰器具有相同的结构,其结构图如下:

同步扰码除了结构简单以外,当信道序列在传输过程中出现错误时,解扰后错误不会增加,因而不会降低数据序列的质量。

同步扰码器也有严重的缺陷,即收发双方必须严格同步,且在同步以后,当信道序列中插入或漏掉若干数据时又会失去同步,造成数据序列无法恢复,必须重新建立同步。

4307

4307

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?