⼀ 实验⽬的

1. 掌握组合逻辑电路的设计⽅法

2. 掌握Quartus II软件⽂本输⼊设计的流程

⼆ 实验内容

2.1 设计输⼊

1. 模块名称:adder

2. 输⼊输出:A,B,Ci,Sum,Co

2.2 引脚约束

1. ⾃⾏确定

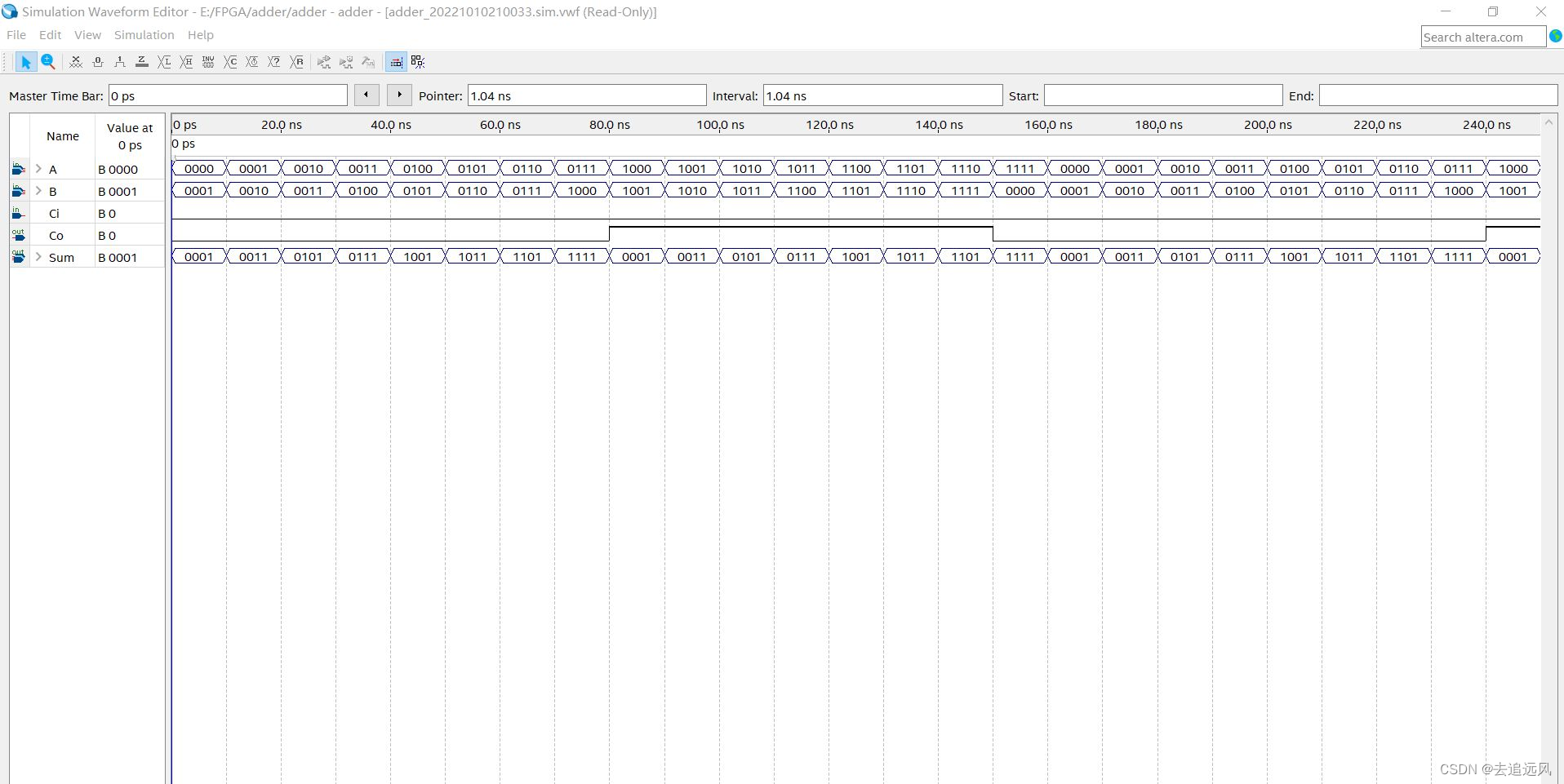

2.3 电路仿真1. 激励⽂件的输⼊A,B分别为0000~1111

2. 功能仿真

三 实验报告

1. 设计代码

2. 仿真结果

3. 报告中附代码和仿真结果截图

注意事项: 模块名称、实体名称、⽂件名称必须⼀致

实验步骤:

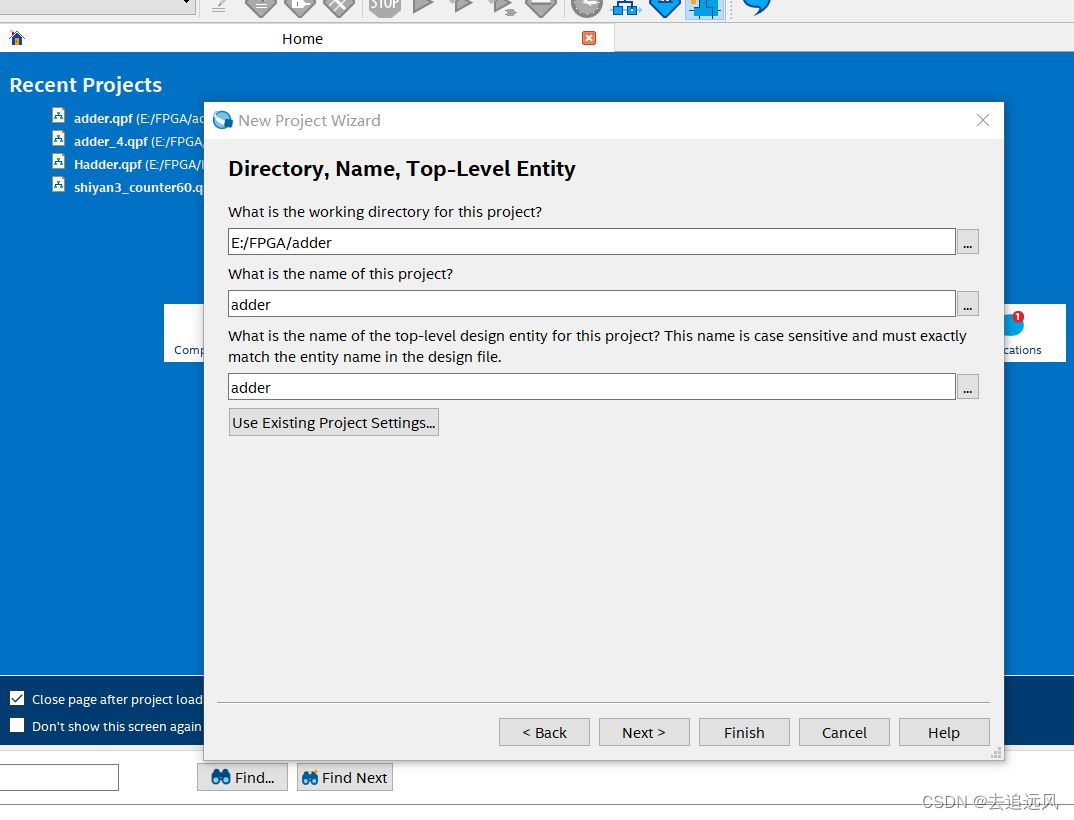

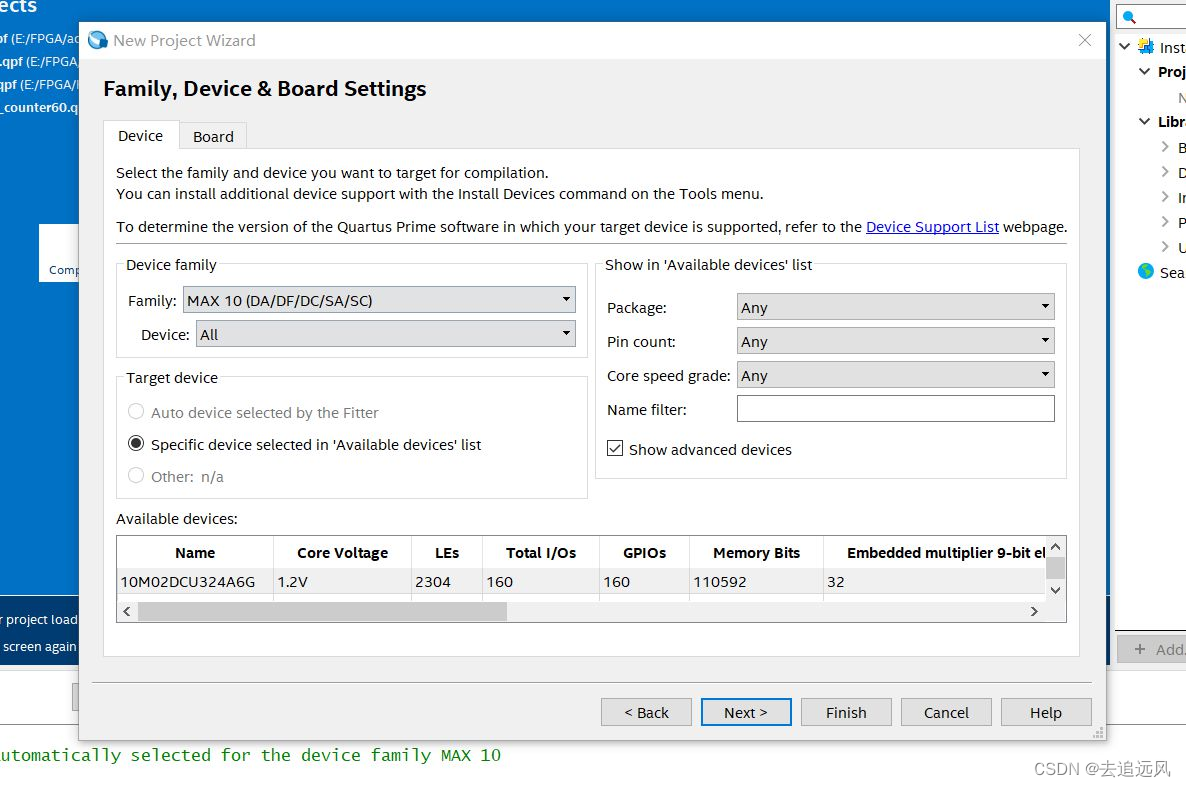

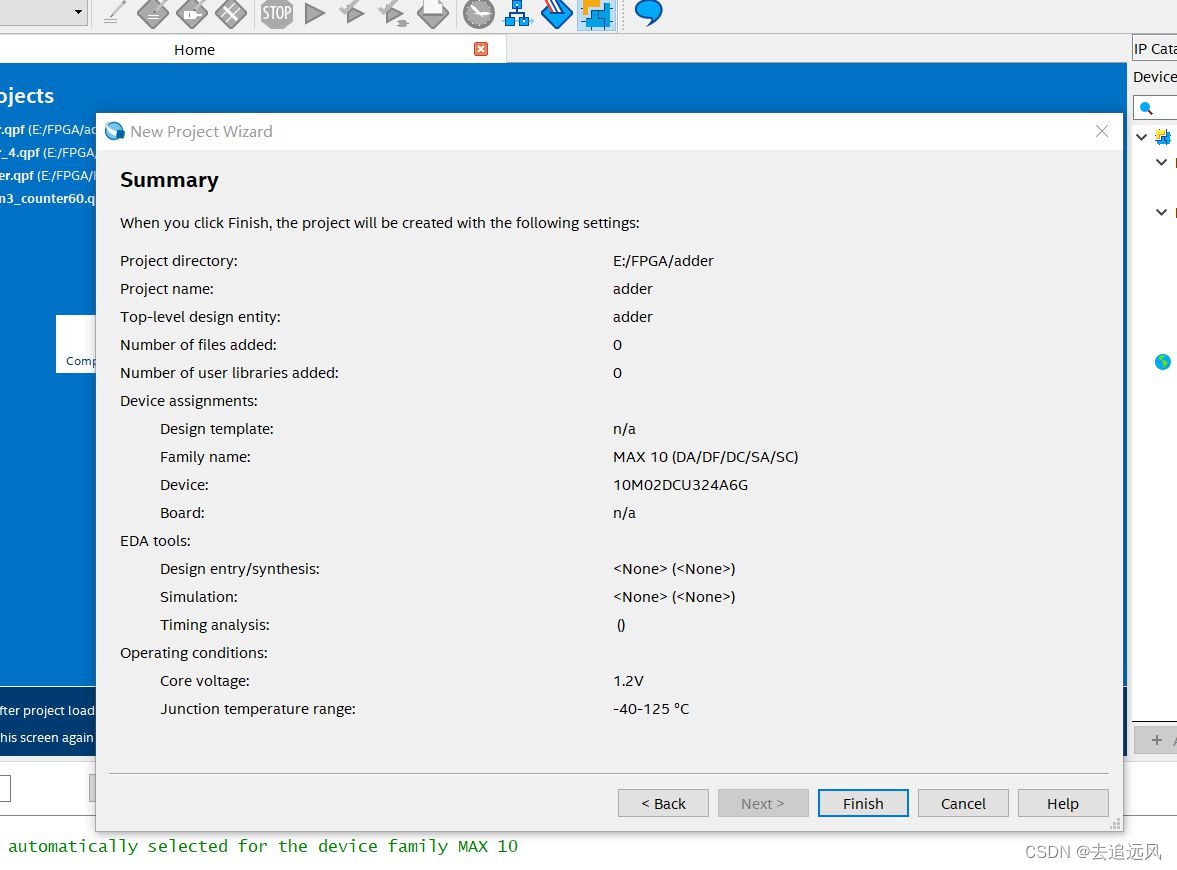

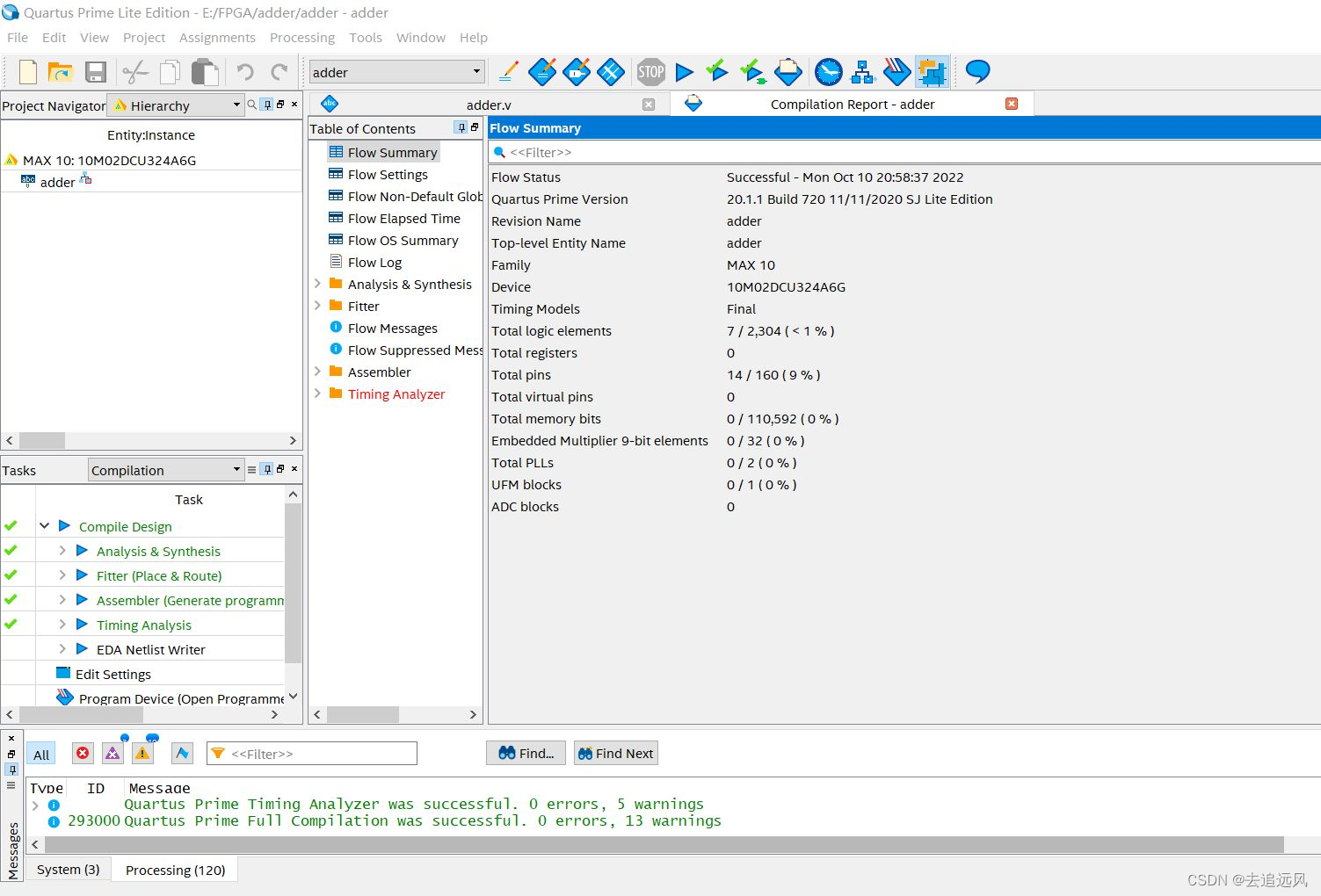

1.路径设置&器件选择

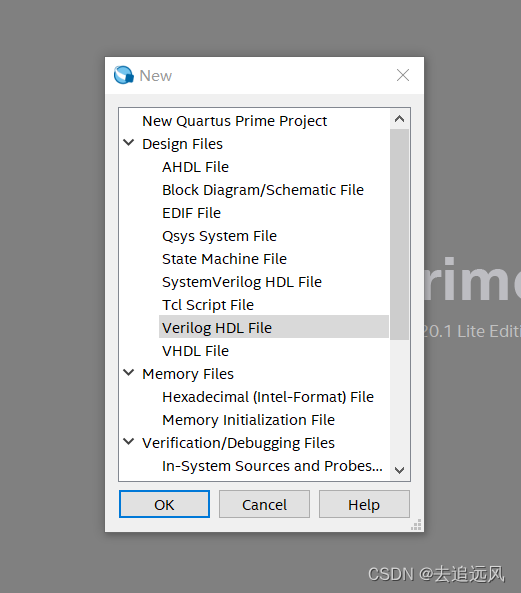

2.创建Verilog代码&编译

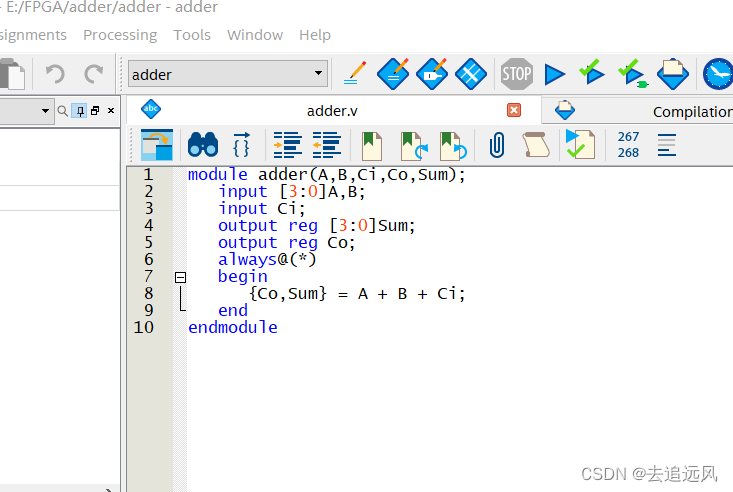

代码:

module adder(A,B,Ci,Co,Sum);

input [3:0]A,B;

input Ci;

output reg [3:0]Sum;

output reg Co;

always@(*)

begin

{Co,Sum} = A + B + Ci;

end

endmodule

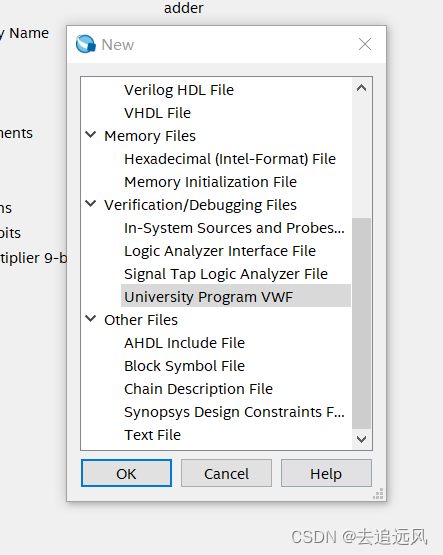

3.创建vwf文件&功能仿真

{Co,Sum} = A + B + Ci,(注意事项:Co和Sum的位置不可互换

其中A和B ,Sum是4bit的数据,进位Ci和Co是1bit数据

功能仿真时,可以设置A和B 分别从0000和0001开始,间隔相同时间自增+1

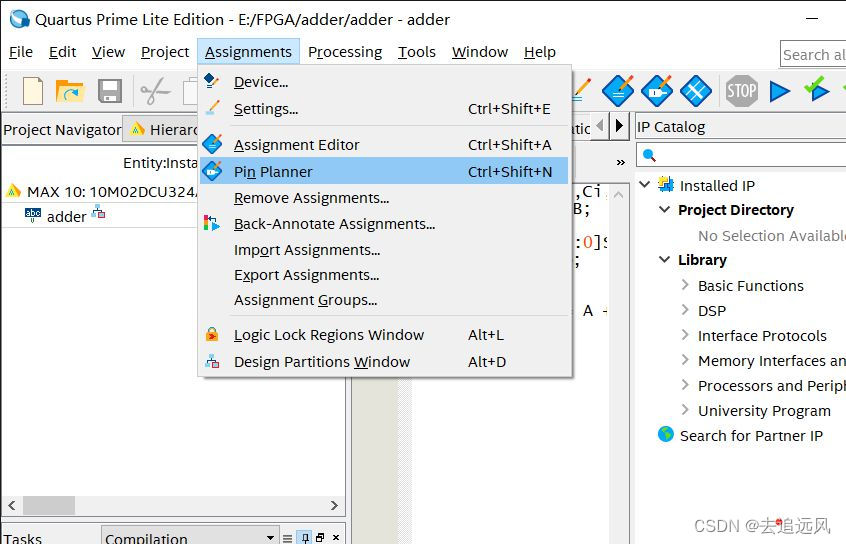

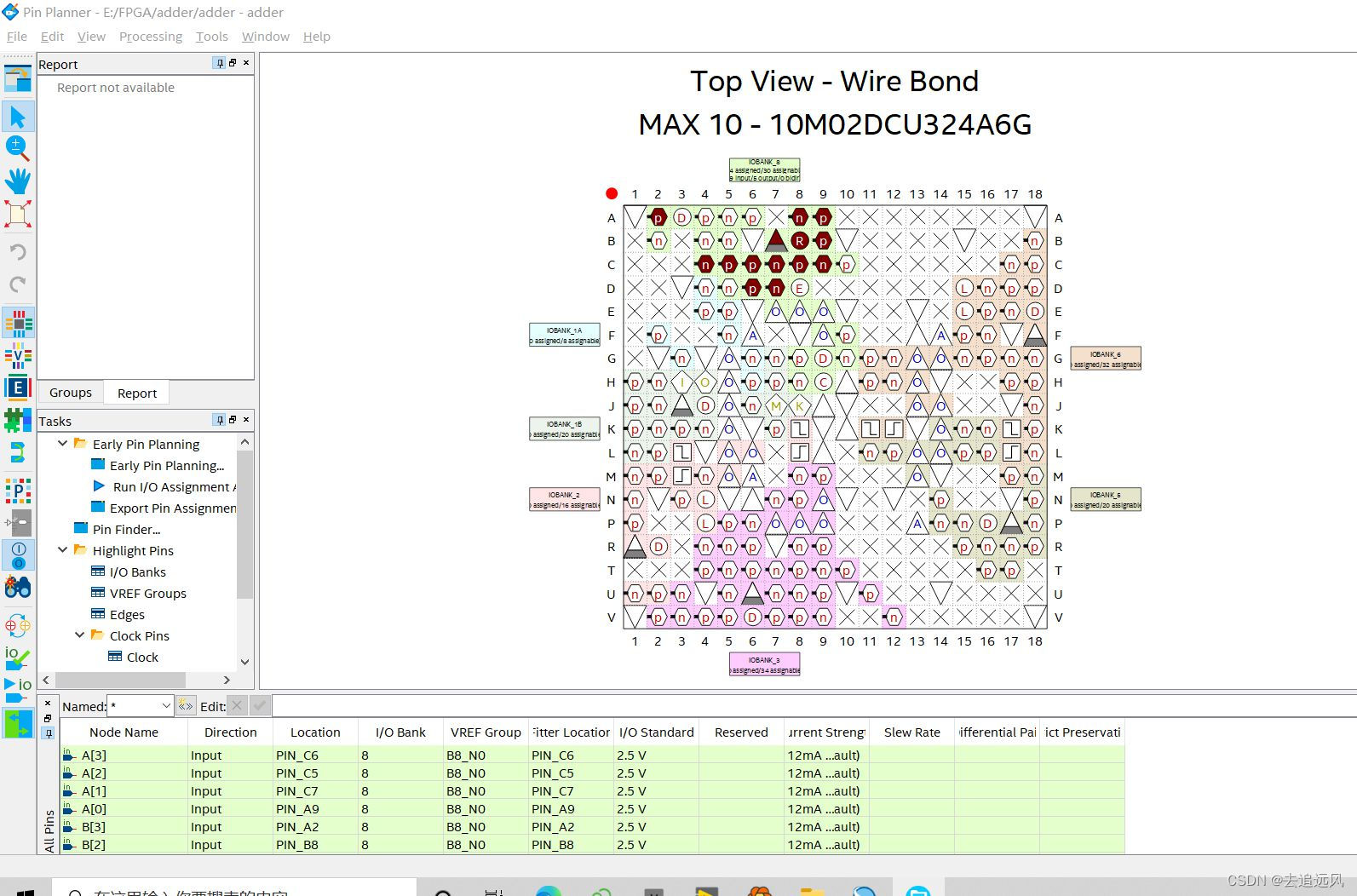

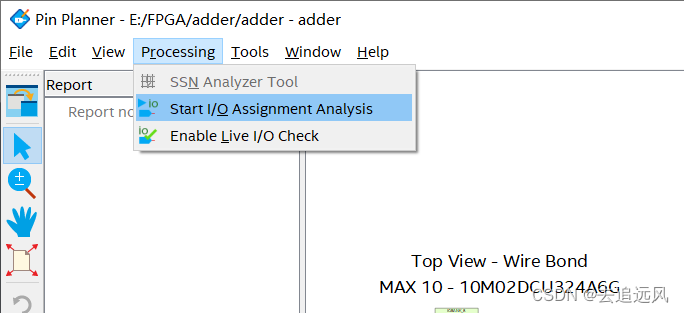

4.分配管脚&检查管脚

3139

3139

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?