专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

分析

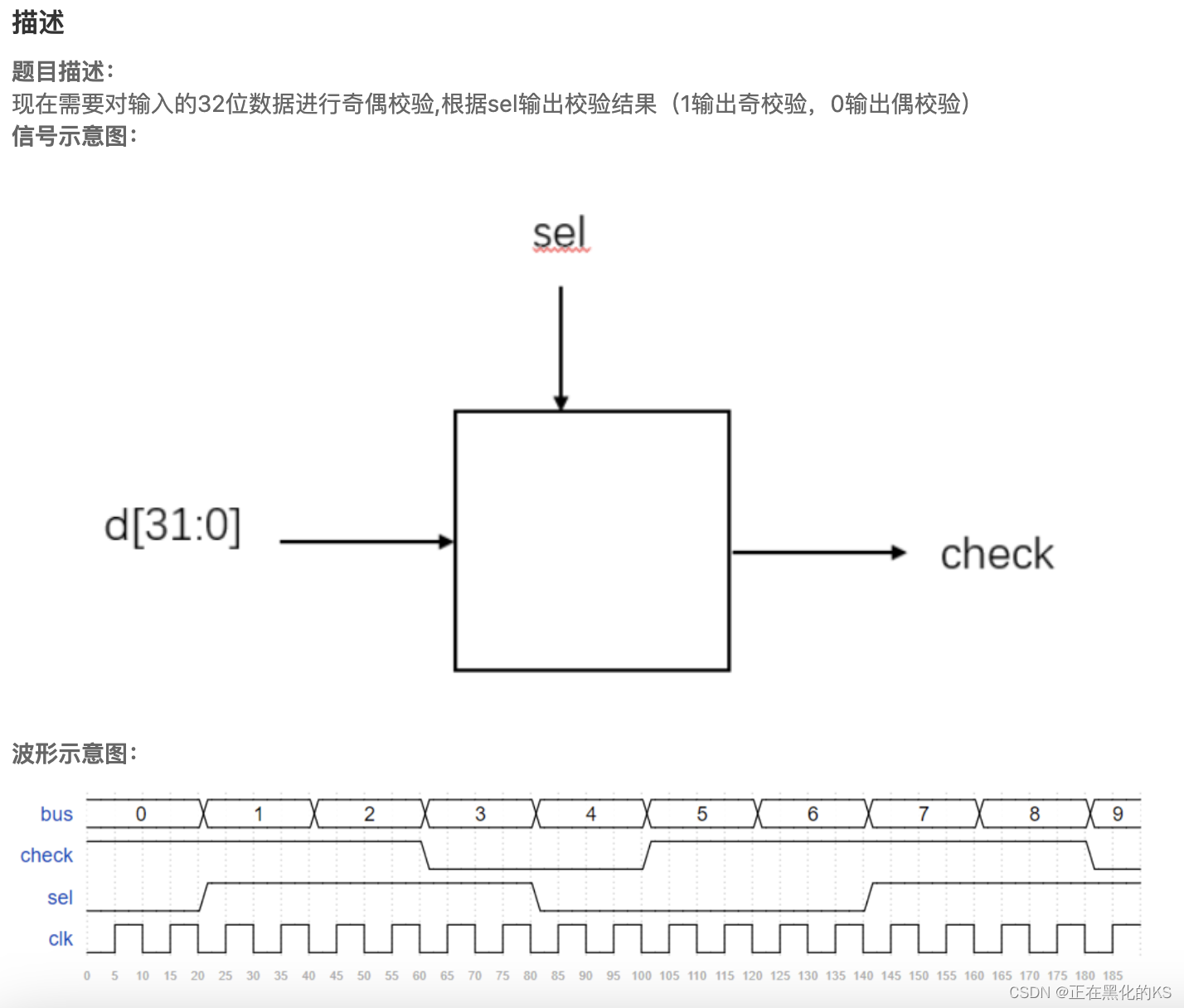

通常所说的奇偶校验:

奇校验:对输入数据添加1位0或者1,使得添加后的数包含奇数个1;

比如100,有奇数个1,那么奇校验结果就是0,这样补完0以后还是奇数个1;

奇校验:对输入数据添加1位0或者1,使得添加后的数包含偶数个1;

回到这个题目,应该是出题人搞反了,按照出题的意思,应该不能叫奇偶校验,应该是叫奇偶检测:

奇检测:输入的数据里有奇数个1就输出1;

偶检测:输入的数据里有偶数个1就输出1;

单目运算符 (|,&,^)

举例说明:

假设d = 3'b100 ; e = &d => e = d[2] & d[1] & d[0] = 1'b0 ;

假设d = 3‘b100 ; f = ^d => f = d[2] ^ d[1] ^ d[0] = 1'b1 ;

解题思路

判断bus中有奇数还是偶数个1,若为奇数则亦或结果为1,反之为0,根据sel的奇偶输出答案即可。

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

//*************code***********//

wire odd ;

assign odd = ^bus ;

assign check = sel ? odd : ~odd ;

//*************code***********//

endmoduleTestbench

`timescale 1ns/1ns

module testbench();

reg clk = 0 ;

reg sel = 0 ;

reg [31:0] bus = 32'b0 ;

wire check ;

always begin

# 5 clk = ~clk ;

end // Create clock with period=10

// A testbench

initial begin

# 20 sel = ~sel ;

# 60 sel = ~sel ;

# 60 sel = ~sel ;

# 50 sel = ~sel ;

$finish ;

end

always begin

# 20 bus = bus + 1 ;

end

odd_sel u1(

.bus(bus),

.sel(sel),

.check(check)

);

initial begin

$dumpfile("out.vcd");

// This will dump all signal, which may not be useful

//$dumpvars;

// dumping only this module

//$dumpvars(1, testbench);

// dumping only these variable

// the first number (level) is actually useless

$dumpvars(0, testbench);

end

endmodule

3885

3885

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?