专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

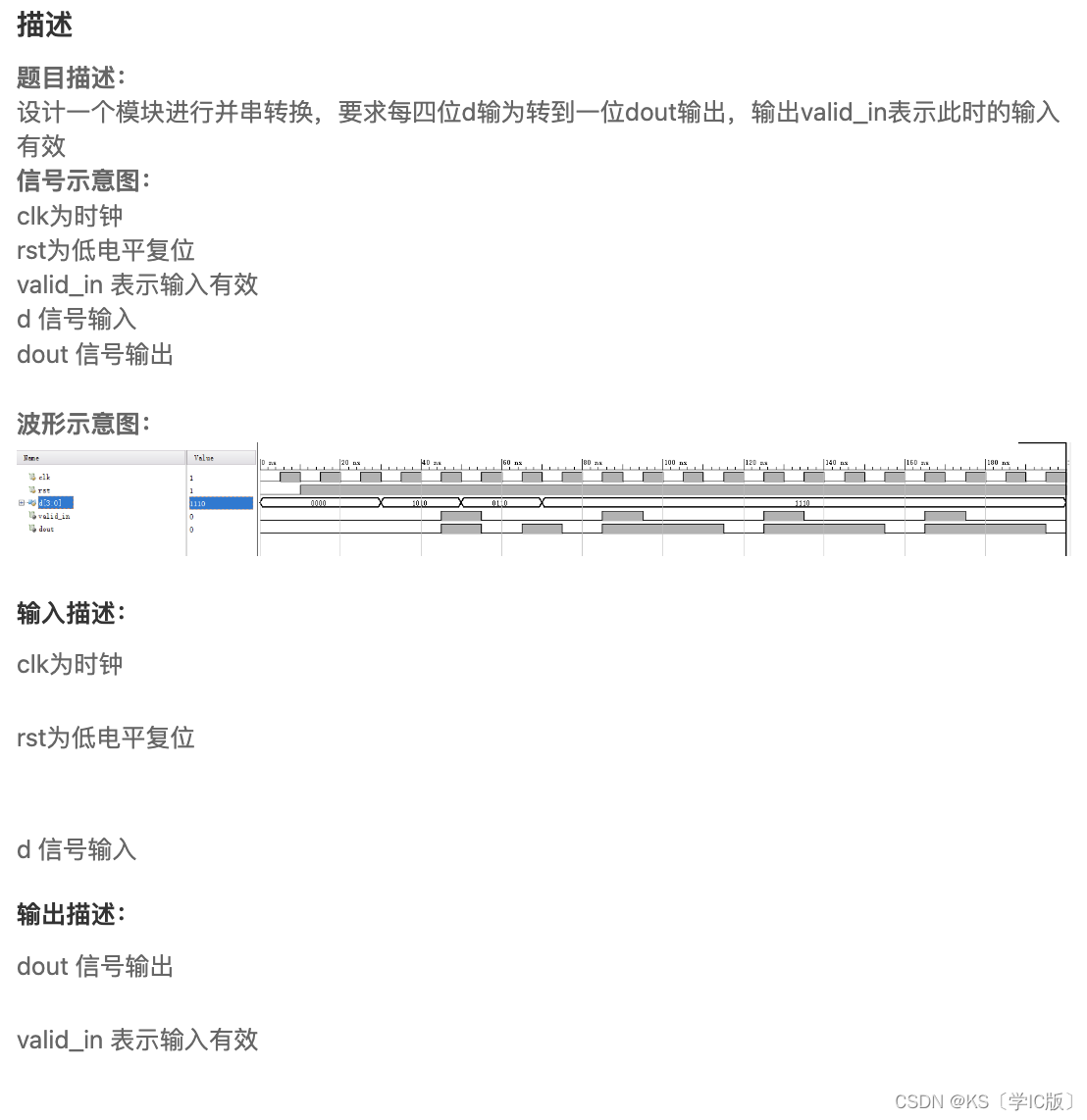

串并转换操作是非常灵活的操作,核心思想就是移位。串转并就是把1位的输入放到N位reg的最低位,然后N位reg左移一位,在把1位输入放到左移后的reg的最低位,这样循环,就可以得到,以最高位开始传输,最低位传输完成的N位数据了,最后将这N位数据同时输出,即为串行输入并行输出;并转串就是把并行的N位数据的最高位给1位输出,然后类似的循环左移就可以了。

串并转换操作是非常灵活的操作,核心思想就是移位。串转并就是把1位的输入放到N位reg的最低位,然后N位reg左移一位,在把1位输入放到左移后的reg的最低位,这样循环,就可以得到,以最高位开始传输,最低位传输完成的N位数据了,最后将这N位数据同时输出,即为串行输入并行输出;并转串就是把并行的N位数据的最高位给1位输出,然后类似的循环左移就可以了。

`timescale 1ns/1ns

module huawei5(

input wire clk ,

input wire rst ,

input wire [3:0]d ,

output wire valid_in ,

output wire dout

);

//*************code***********//

reg [3:0] data ;

reg [1:0] cnt ;

reg valid ;

always @ (posedge clk or negedge rst) begin

if (!rst) begin

data <= 0 ;

cnt <= 0 ;

valid <= 0 ;

end

else begin

if (cnt == 3) begin

data <= d ; // 并行输入

cnt <= 0 ;

valid <= 1 ;

end

else begin

cnt <= cnt + 1 ;

valid <= 0 ;

data <= {data[2:0], data[3]} ; // 每个时钟将数据左移,保证每位数据都能出现在最高位

end

end

end

assign dout = data[3] ; // 每个时钟上升沿读取当前数据的最高位,四个时钟读完

assign valid_in = valid ;

//*************code***********//

endmodule

1631

1631

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?