Verilog小案例-任意位宽并行数据转串行数据

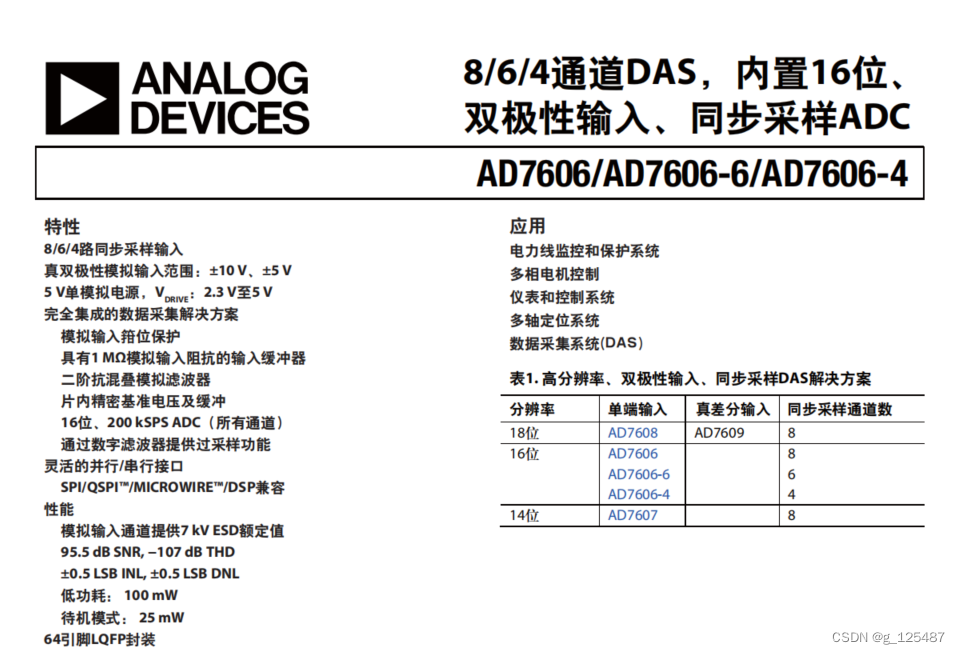

一、应用场景

将ad7606模块采集的电压值转化成串行进行输出,方便后续对数据进行编码通信。其实spi输出的数据本身就是串行的,我这个思路稍微麻烦了一点,不过问题不大。后续可能需要对不同通道之间的数据添加头、尾,这样应该更加方便。

二、实验代码

//可以自行结合修改输入位宽,同步修改cnt以及边界值即可

module data_change(

input i_sys_clk,

input i_rstn,

input [15:0] data_i,

output reg data_o

);

reg [14:0] cnt;

always@(posedge i_sys_clk or negedge i_rstn)begin

if(!i_rstn)begin

data_o <= 0;

cnt <= 15'b000000000000000;

end

else begin

if(cnt < 16)begin

data_o <= data_i[15-cnt];

cnt <= cnt + 1;

end

else begin

data_o <= data_i[15];

cnt <= 15'b000000000000001;

end

end

end

endmodule

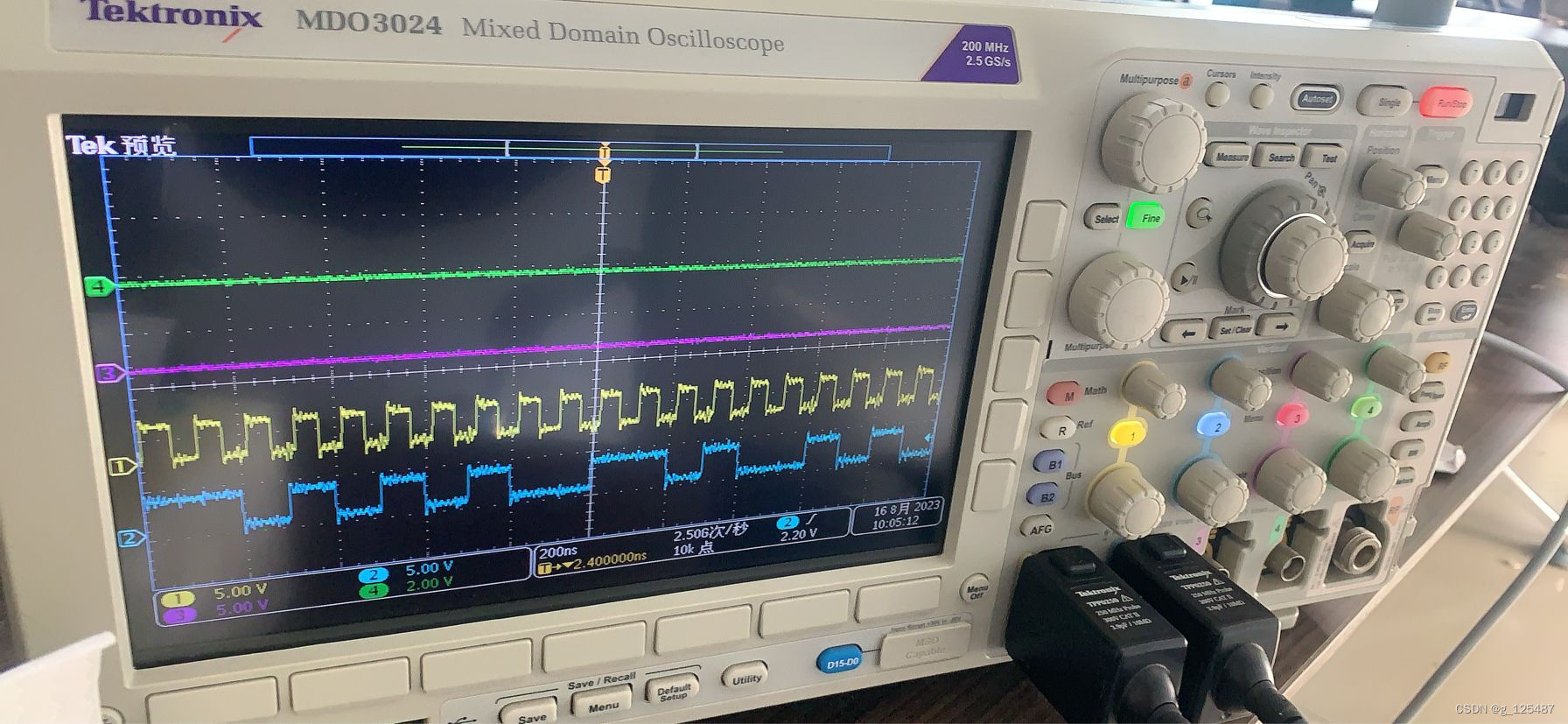

三、上板验证

可以根据时钟将你的并行数据按照你想要的速率进行串行输出~

总结

本文以16位并行数据输入为例,将该数据转化为串行数据进行输出,上板验证正确,不存在错误。同时可以进行修改,可以自行结合修改输入位宽,同步修改cnt以及边界值即可!

1456

1456

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?