APB概述

APB协议全称:先进外围总线(Advanced Peripheral Bus) ,属于AMBA总线协议的一种。特点:低速总线,低功耗,接口简单,每个数据的传输均需要两个时钟周期,带宽利用率较低。在APB总线中,只有唯一一个Master,即APB Bridge, 其他的外围设备如I2C,SPI,UART均为Slave。

APB总线与整体SOC框架

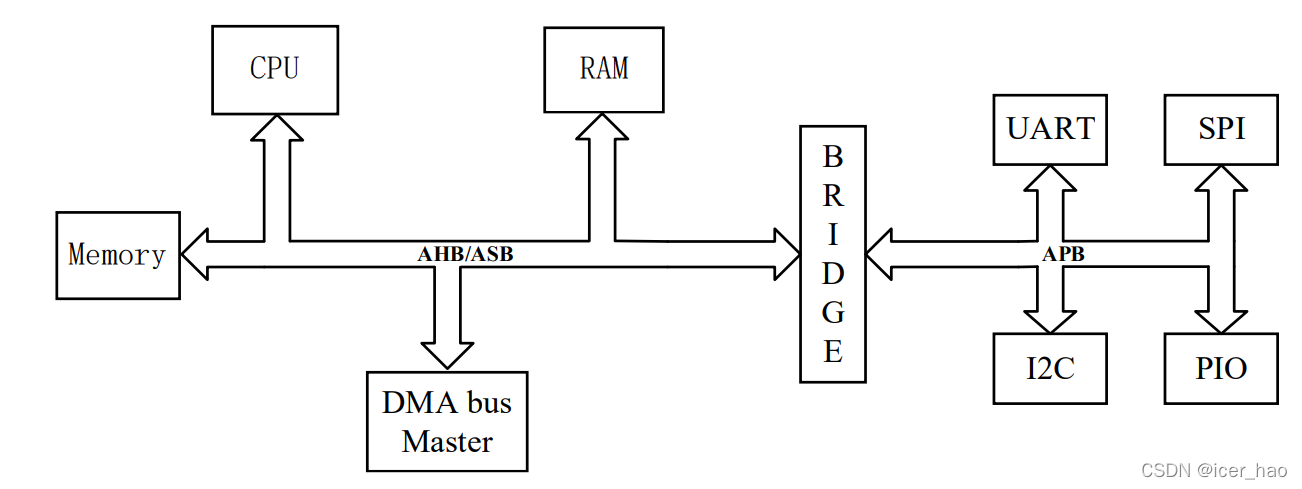

典型的基于 AMBA 总线的 SOC 系统结构如下图所示。这种 SOC 结构是在高速总线协议和低速总线协议的互连支持下,将工作在不同频率的各个系统模块进行整合,最终协同处理器完成运算工作。其中高速总线往往采用 AHB 或者 ASB协议,而低速总线一般使用 APB 协议,两种总线之间使用转接桥(bridge)模块完成协议转换。

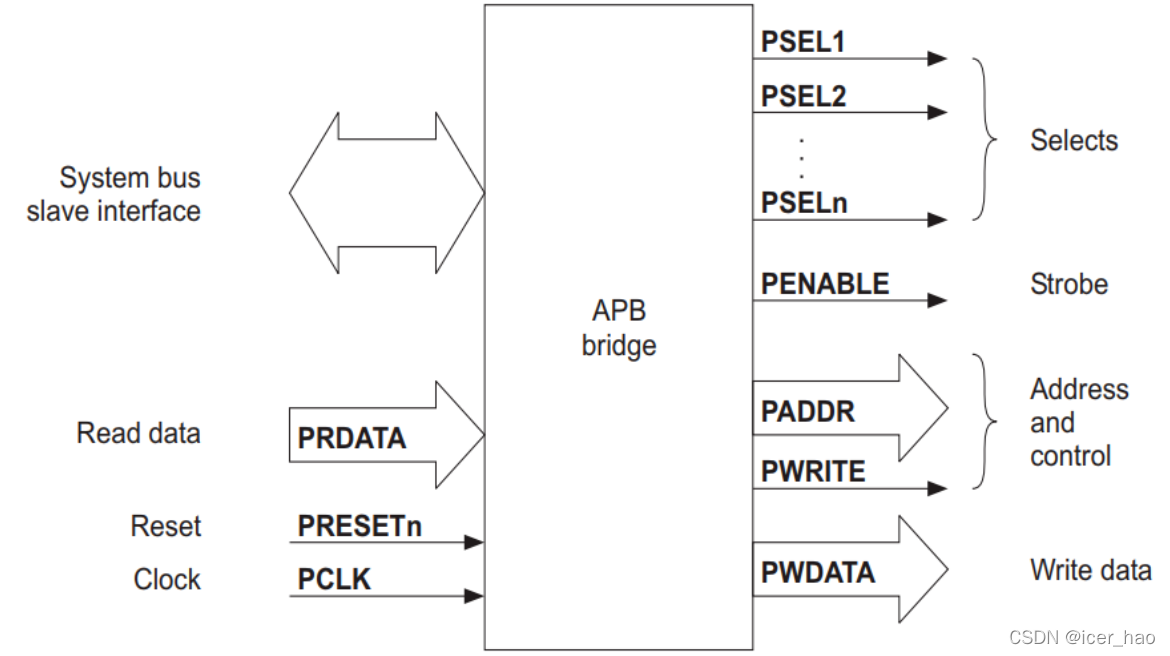

APB2.0接口示意图如下:

相比于APB2.0协议,APB3.0增加了PREADY和PSLVERR信号。Slave通过PREADY信号直接来告诉master现在Slave已经READY了,可以接受读写操作,如果此时READY信号为低,那么master必须等到它拉高以后,才能进行读写操作。而PSLVERR信号即反馈错误,当slaver中数据有错误时反馈给master。

APB总线的读写时序

读时序

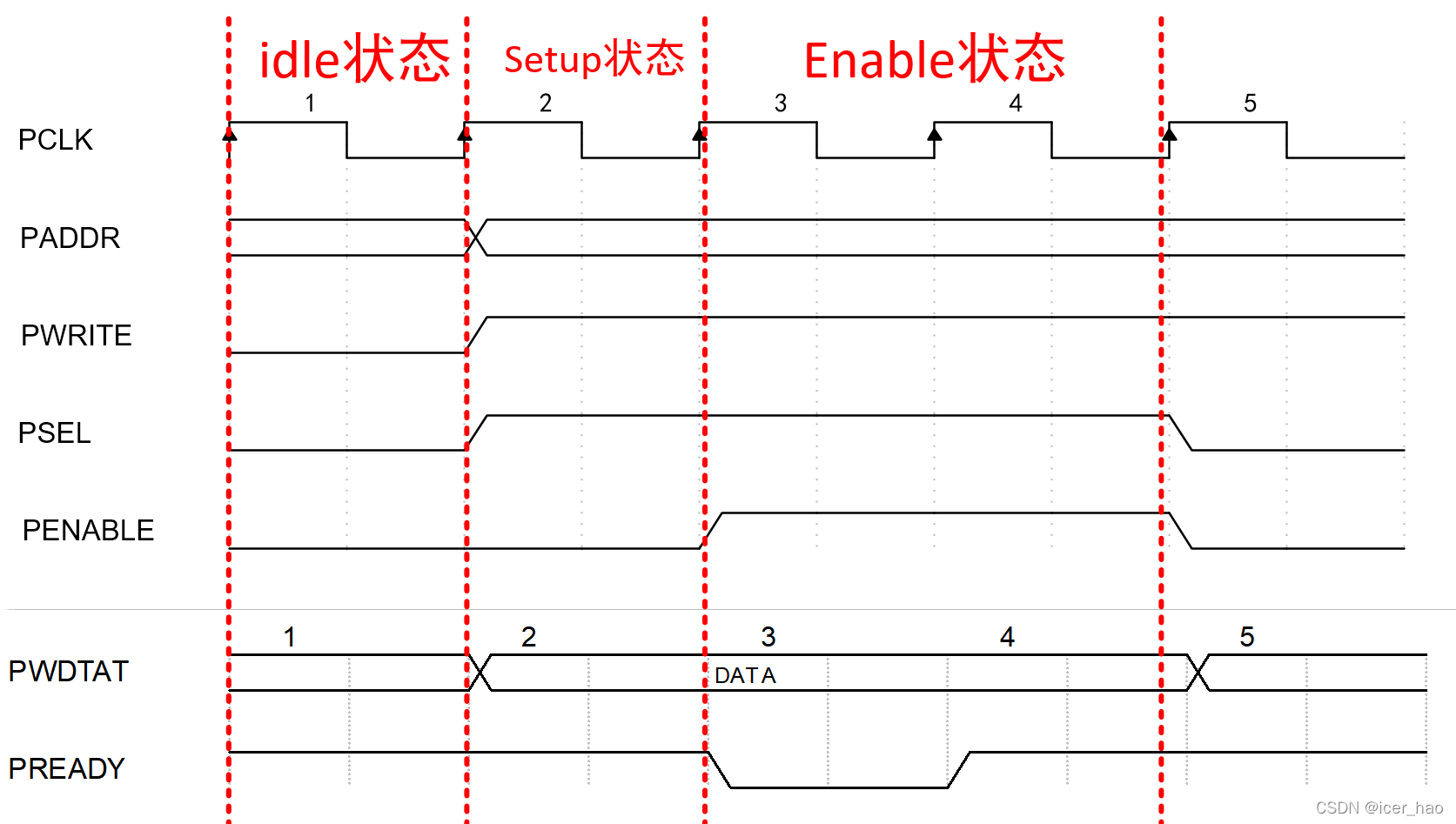

如上图所示,在APB的第一个上升沿,APB内状态机进入 idel 状态。当第二个上升沿来临时,地址信号、读写控制信号和选择信号会在上升沿被触发,APB 状态机进入 Setup 状态。一个周期后,PENABLE 信号被拉高,此时状态机进入Enable状态,进行数据的写入。如果没有后续的操作,一个周期后 PSEL 和PNEABLE 都被拉低,代表此次传输结束。若有传输需求,则重新进入idle状态。而 PADDR 和 PWRITE 等信号可以保持不变,以减少信号翻转从而降低功耗。上图中加入了PREADY信号,APB协议中默认其保持拉高,当READY信号拉低时,需要等待其拉高以后再进行读写操作。

写时序

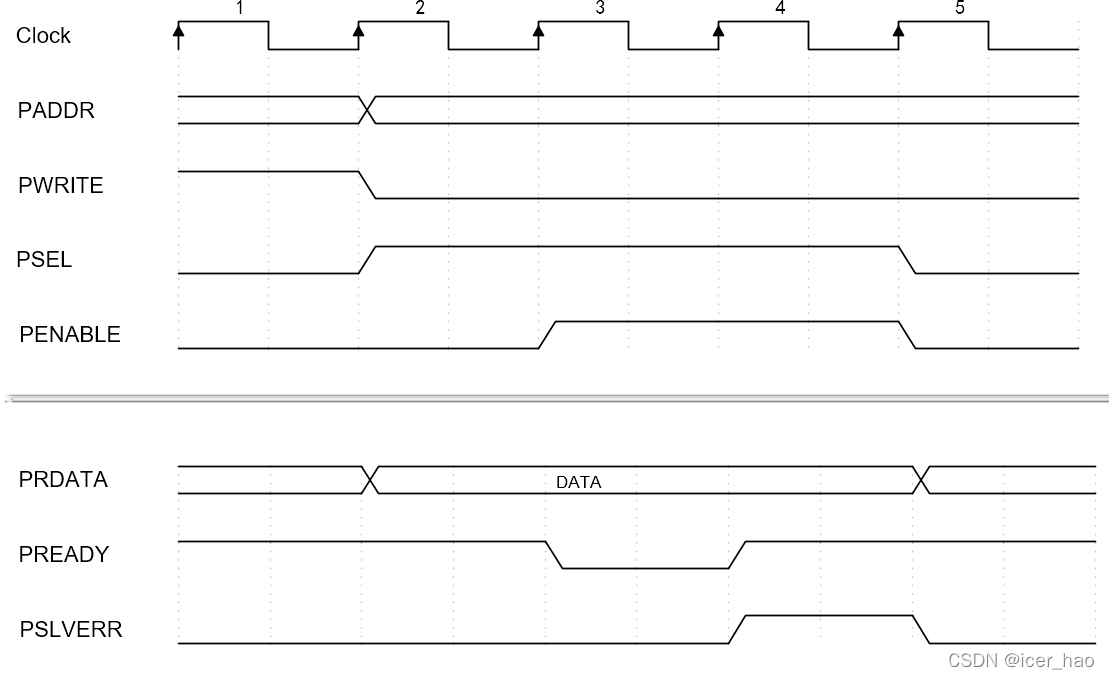

APB总线的读传输操作与上述类似,在T3开始后,有效数据会被放到PRDATA信号线上,供 CPU 等模块读取,这里加入了PSLVERR信号,当传输有错误时,会拉高此信号。

本文详细介绍了APB(Advanced Peripheral Bus)总线协议,作为AMBA总线家族的一员,APB主要用于低速外设连接。内容包括APB的特性、在SOC系统中的角色、APB2.0和APB3.0接口的区别以及读写时序。APB总线只有一个主设备(APB Bridge)和多个从设备,并且在APB3.0中引入了PREADY和PSLVERR信号以增强错误处理和同步机制。

本文详细介绍了APB(Advanced Peripheral Bus)总线协议,作为AMBA总线家族的一员,APB主要用于低速外设连接。内容包括APB的特性、在SOC系统中的角色、APB2.0和APB3.0接口的区别以及读写时序。APB总线只有一个主设备(APB Bridge)和多个从设备,并且在APB3.0中引入了PREADY和PSLVERR信号以增强错误处理和同步机制。

1860

1860

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?