One drawback of the ripple carry adder (See previous exercise) is that the delay for an adder to compute the carry out (from the carry-in, in the worst case) is fairly slow, and the second-stage adder cannot begin computing its carry-out until the first-stage adder has finished. This makes the adder slow. One improvement is a carry-select adder, shown below. The first-stage adder is the same as before, but we duplicate the second-stage adder, one assuming carry-in=0 and one assuming carry-in=1, then using a fast 2-to-1 multiplexer to select which result happened to be correct.

纹波进位加法器的一个缺点(参见前面的练习)是加法器计算进位的延迟(从进位,在最坏的情况下)相当慢,并且第二级加法器无法开始计算其执行直到第一级加法器完成。这使加法器变慢。一种改进是进位选择加法器,如下所示。第一级加法器与之前相同,但我们复制第二级加法器,一个假设进位=0,一个假设进位=1,然后使用快速2对1多路复用器选择哪个结果碰巧是正确的。

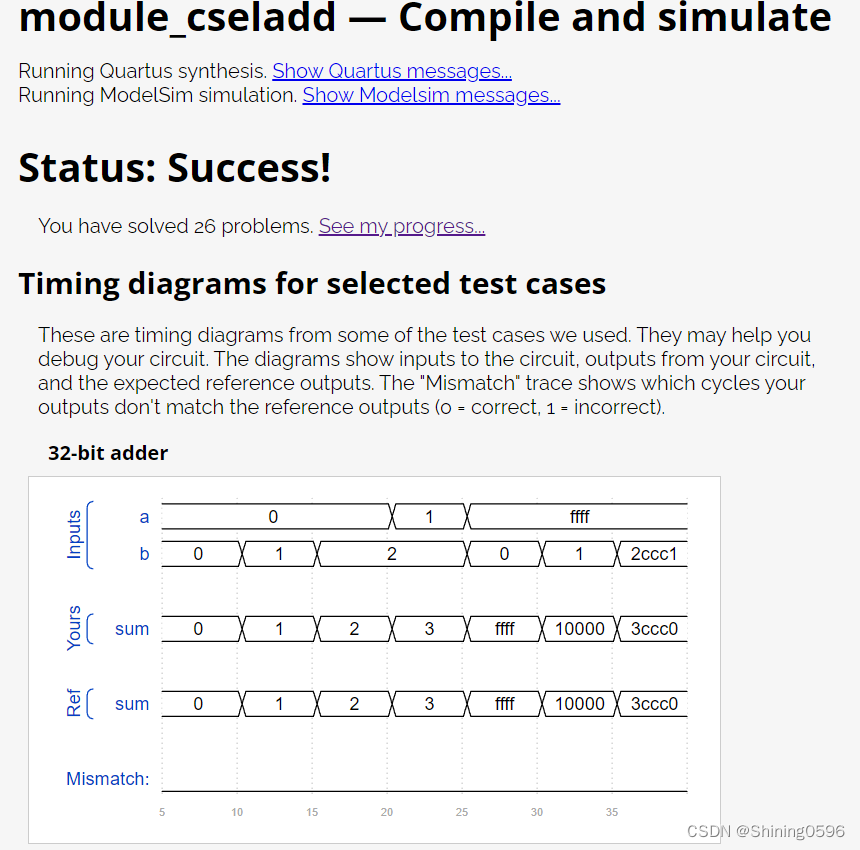

In this exercise, you are provided with the same module add16 as the previous exercise, which adds two 16-bit numbers with carry-in and produces a carry-out and 16-bit sum. You must instantiate three of these to build the carry-select adder, using your own 16-bit 2-to-1 multiplexer.

在本练习中,为您提供与前一练习相同的模块 add16,它将两个 16 位数字与进位相加,并产生一个进位和 16 位和。您必须使用您自己的 16 位 2 对 1 多路复用器来实例化其中的三个以构建进位选择加法器。

Connect the modules together as shown in the diagram below. The provided module add16 has the following declaration:

如下图所示将模块连接在一起。提供的模块 add16 具有以下声明:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

Module Declaration

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire carry;

wire [31:16] sum0;

wire [31:16] sum1;

add16 al(a[15:0],b[15:0],1'b0,sum[15:0],carry);

add16 ah0(a[31:16],b[31:16],1'b0,sum0[31:16],);

add16 ah1(a[31:16],b[31:16],1'b1,sum1[31:16],);

assign sum[31:16] = carry?sum1:sum0;

endmodule

358

358

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?