-

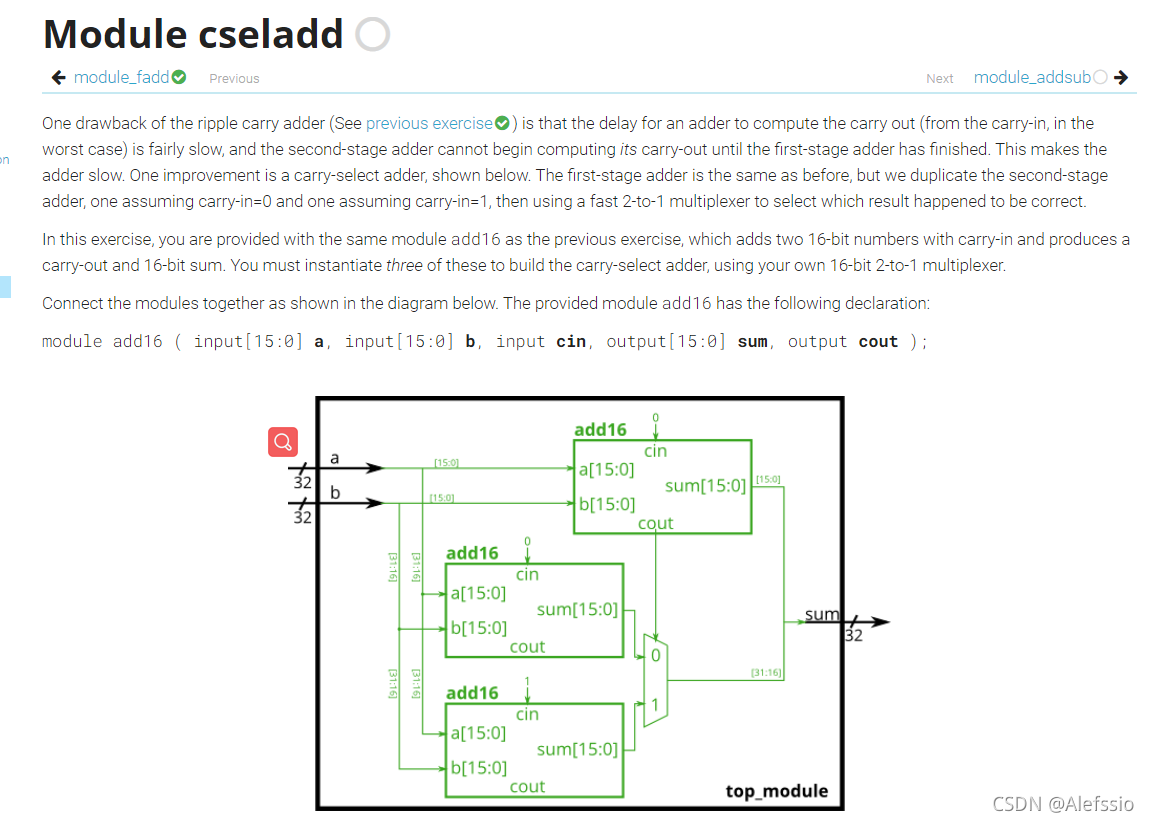

Module cseladd

用一个多路选择器选择使用哪一个的后8位.

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire [15:0]sum1;

wire [15:0]sum2;

wire cout1;

add16 addbuff1(a[15:0],b[15:0], 0,sum[15:0], cout1);

add16 addbuff2(a[31:16],b[31:16], 0,sum1);

add16 addbuff3(a[31:16],b[31:16], 1,sum2);

assign sum[31:16] = cout1?sum2:sum1; //作为一个两路选择器

endmodule-

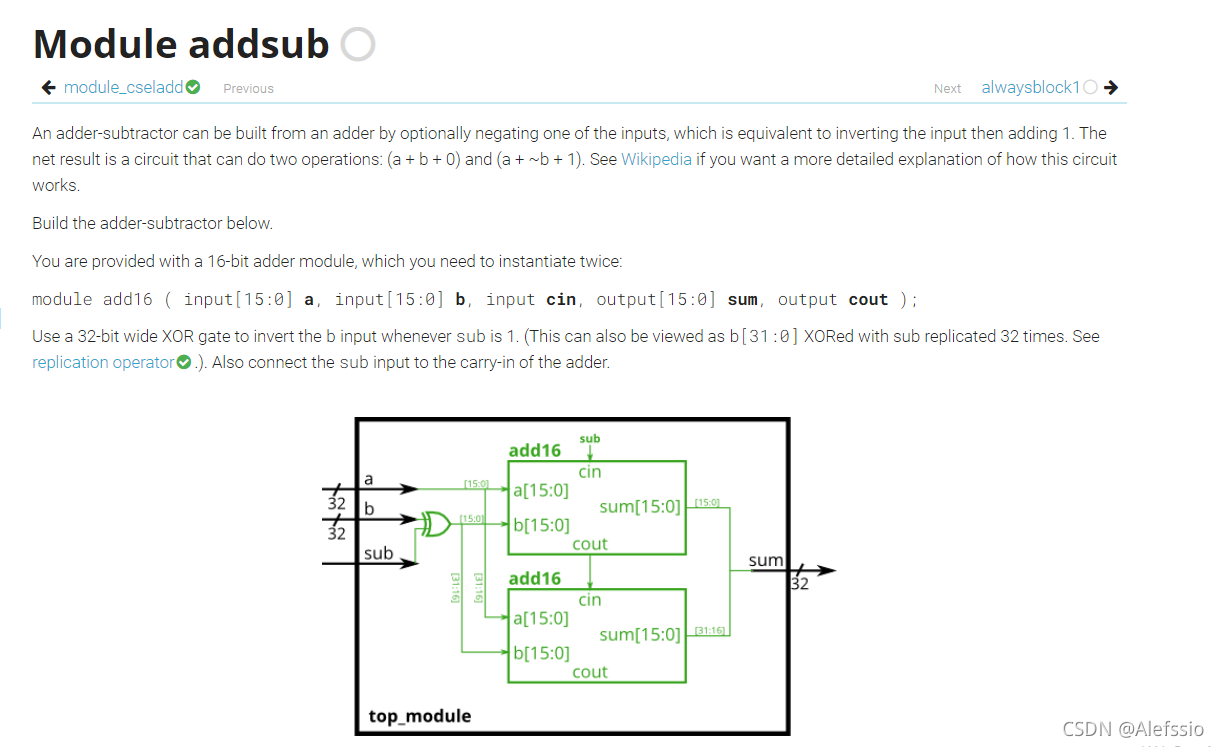

Module addsub

加减法器:减法取反+1

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0] sum

);

wire [31:0] Re_b;

wire cout1;

assign Re_b = {32{sub}}^b; //复制32次 sub^b只有一次

add16 addbuff1( a[15:0], Re_b[15:0], sub, sum[15:0],cout1);

add16 addbuff2( a[31:16], Re_b[31:16], cout1, sum[31:16]);

endmodule-

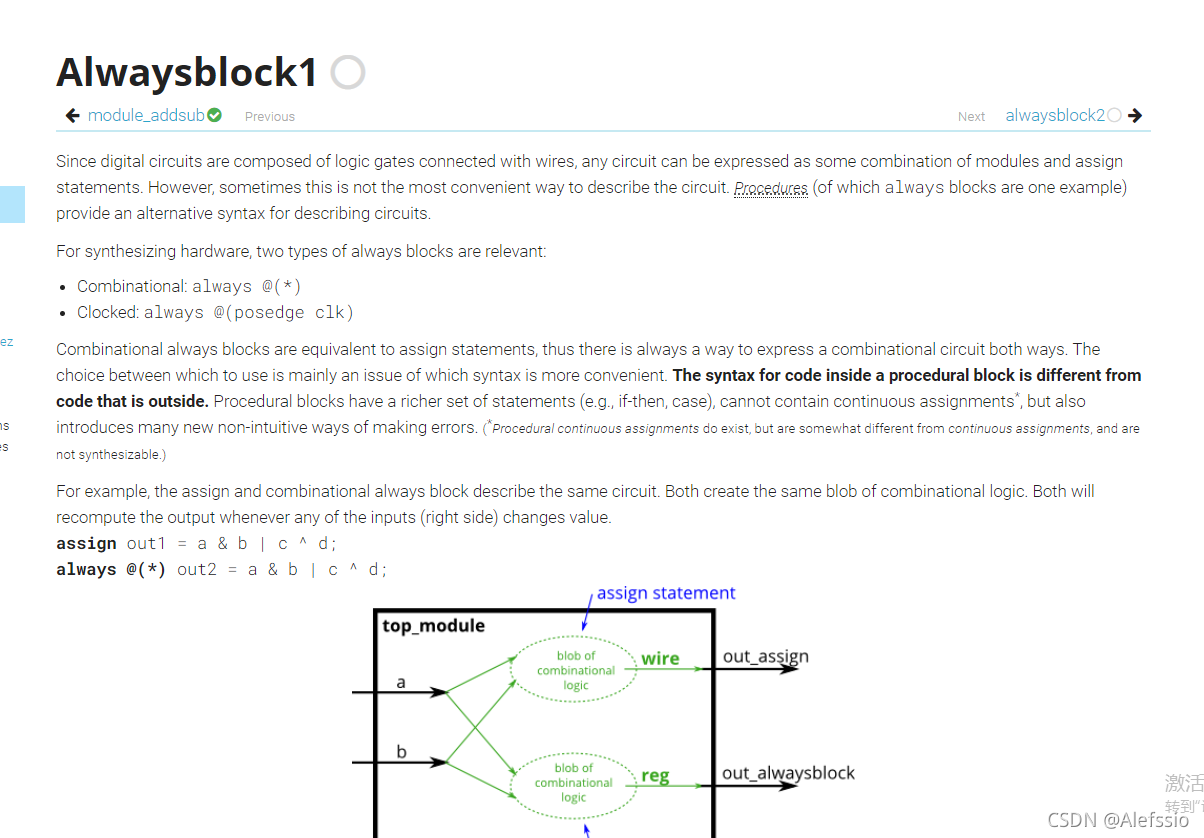

Alwaysblock1

组合逻辑和时序逻辑

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

output wire out_assign,

output reg out_alwaysblock

);

assign out_assign = a&b;

always@(*) out_alwaysblock = a&b;

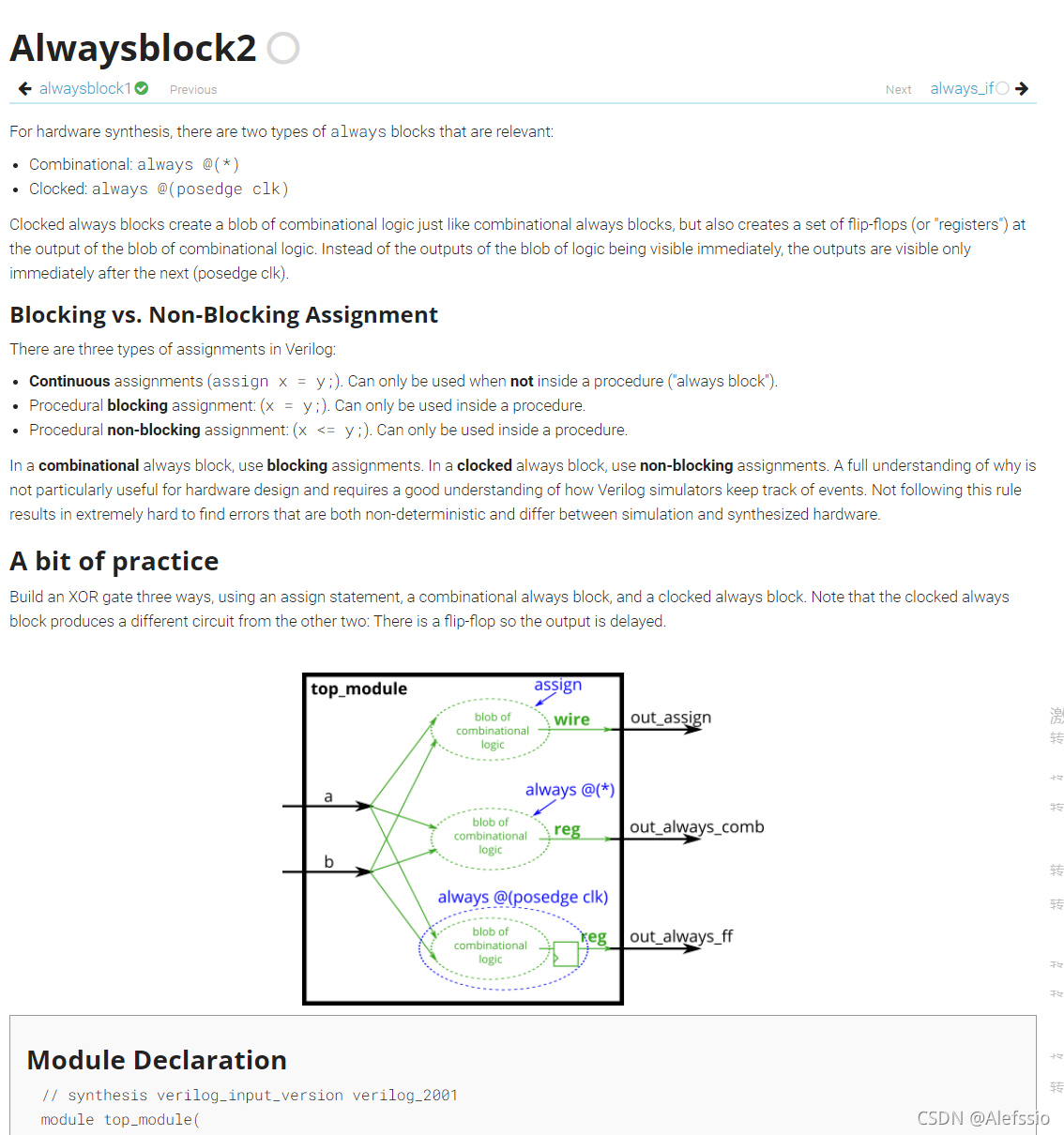

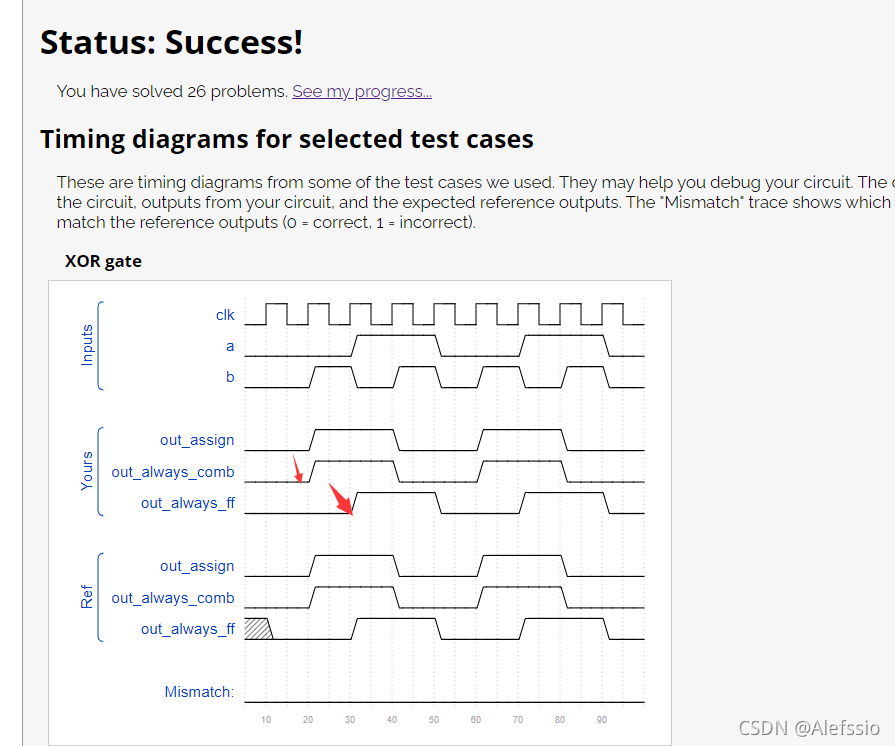

endmodule- Alwaysblock2

本题主要描述组合逻辑和时序组合逻辑以及时钟always块的区别在,时序图里面可以看到时钟always有延迟,是因为他有一个触发器。

module top_module(

input clk,

input a,

input b,

output wire out_assign,

output reg out_always_comb,

output reg out_always_ff );

assign out_assign = a^b;

always@(*) out_always_comb = a^b;

always@(posedge clk) out_always_ff = a^b;

endmodule

-

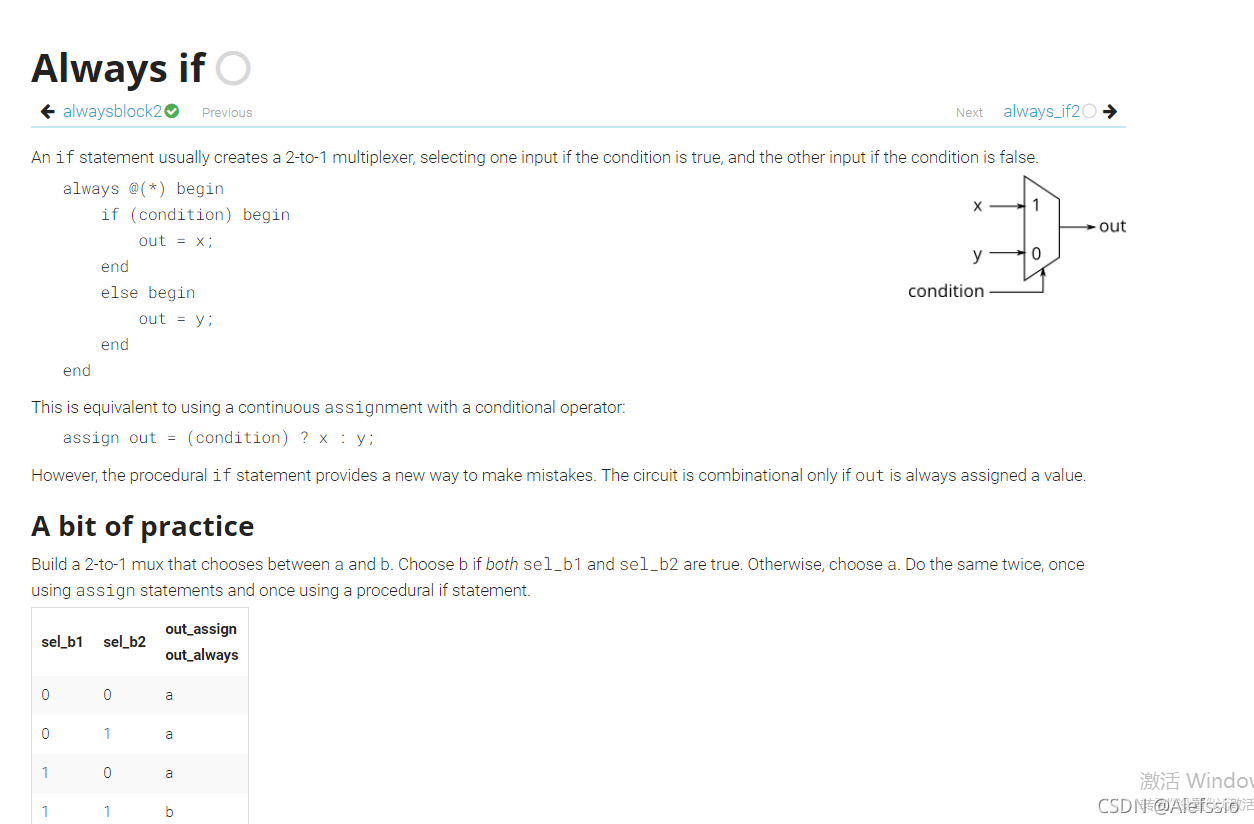

Always if

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

input sel_b1,

input sel_b2,

output wire out_assign,

output reg out_always );

assign out_assign = (sel_b1&sel_b2)?b:a;

always@(*)

begin

if(sel_b1&sel_b2)

out_always = b;

else out_always = a;

end

endmodule-

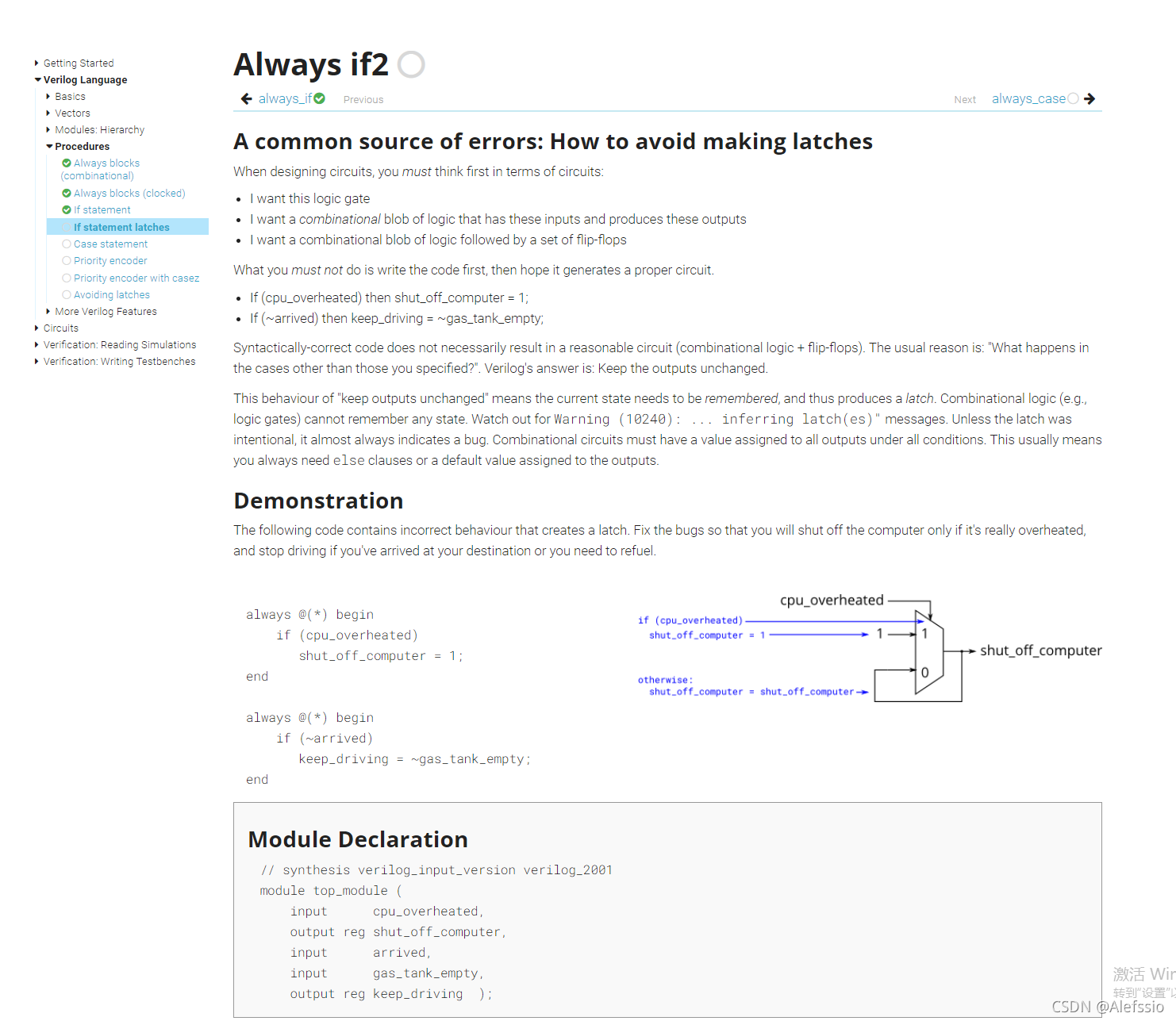

Always if2

描述锁存错误的情况。上面图片的代码就是错误实例。在条件为真的情况下,赋值没问题,但是在其他情况下仍然保持赋值情况,导致数据一直被锁存。

module top_module (

input cpu_overheated,

output reg shut_off_computer,

input arrived,

input gas_tank_empty,

output reg keep_driving ); //

always @(*) begin

if (cpu_overheated)

shut_off_computer = 1;

else shut_off_computer = 0;

end

always @(*) begin

if (~arrived)

keep_driving = ~gas_tank_empty;

else

keep_driving = 0;

end

endmodule-

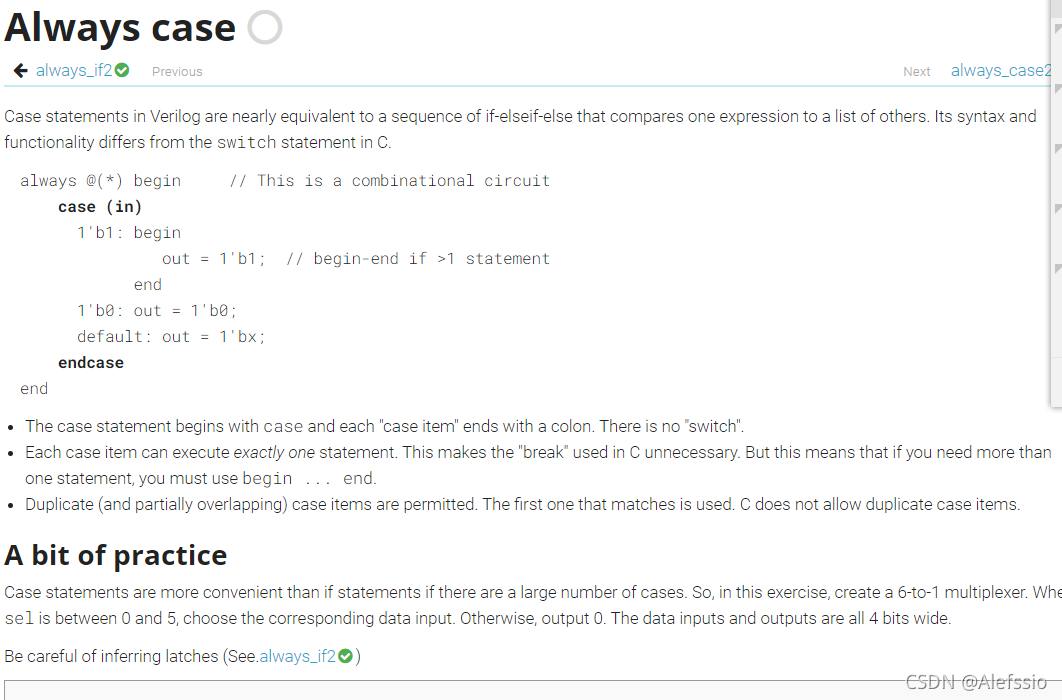

Always case

如何使用case

module top_module (

input [2:0] sel,

input [3:0] data0,

input [3:0] data1,

input [3:0] data2,

input [3:0] data3,

input [3:0] data4,

input [3:0] data5,

output reg [3:0] out );//

always@(*) begin // This is a combinational circuit

case(sel)

3'b0: out = data0;

3'd1: out = data1;

3'd2: out = data2;

3'd3: out = data3;

3'd4: out = data4;

3'd5: out = data5;

default:out = 4'd0;

endcase

end

endmodule

455

455

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?