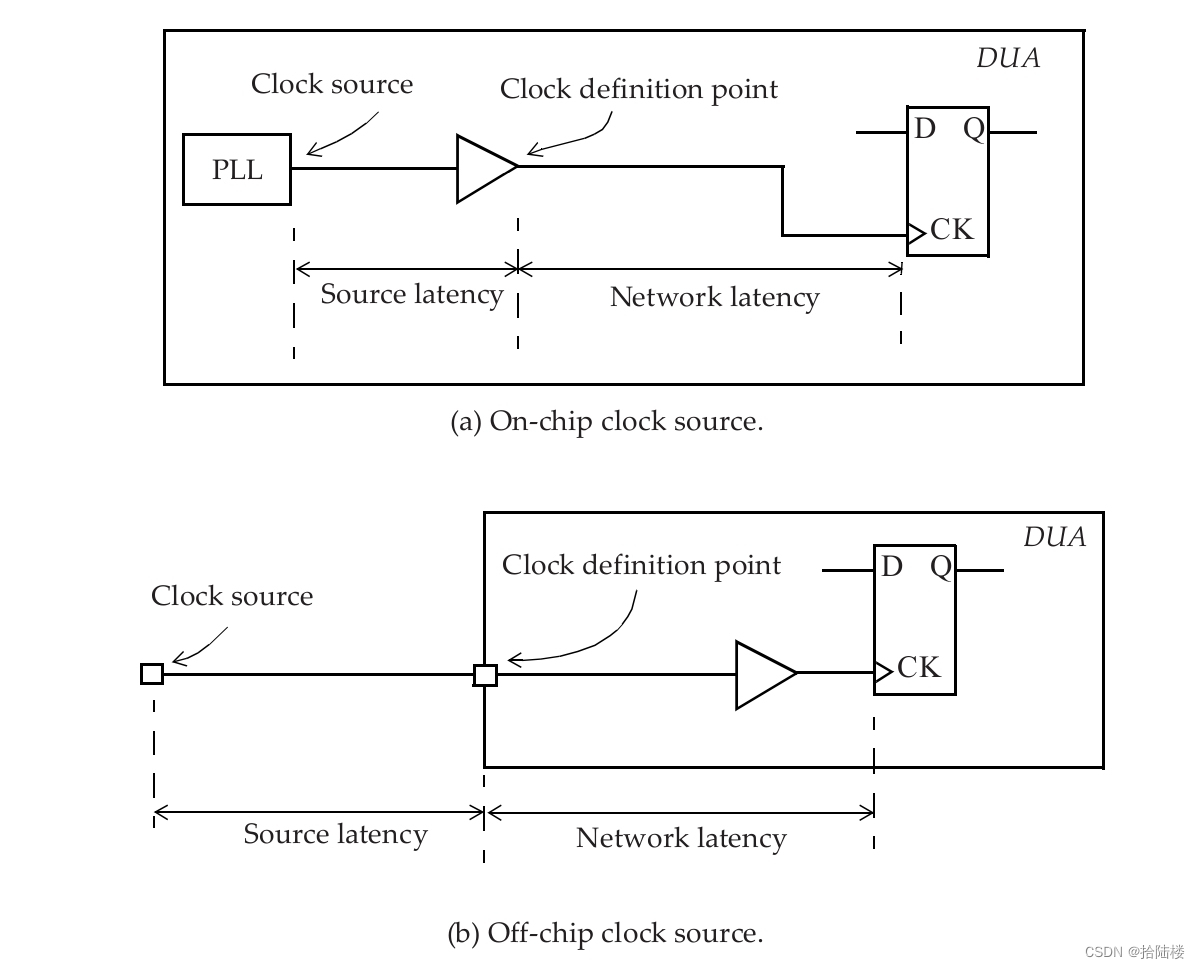

clock latency分为两类:source latency和network latency,其中network latency指的是时钟定义点(create_clock)到flip flops的clock pin的延迟,而source latency(也叫insertion delay)是从时钟源头到时钟定义点的延迟,source latency可以是片上(on-chip)延迟,也可以是片外(off_chip)延迟,如下图。flip flops的clock pin上总的clock latency就是source latency与network latency的和。

source latency与network latency一个很重要的区别在于,一但经过了时钟树综合(CTS)构建了真实的时钟树ÿ

本文详细介绍了静态时序分析中的时钟延时,包括source latency和network latency的区别。source latency是从时钟源头到时钟定义点的延迟,而network latency是从时钟定义点到触发器的时钟引脚的延迟。经过时钟树综合后,network latency可忽略,总时钟延迟由source latency和实际路径延迟构成。此外,文章还探讨了generate clock的源时钟概念及其应用场景,如时钟门控和PLL在时钟系统中的作用。

本文详细介绍了静态时序分析中的时钟延时,包括source latency和network latency的区别。source latency是从时钟源头到时钟定义点的延迟,而network latency是从时钟定义点到触发器的时钟引脚的延迟。经过时钟树综合后,network latency可忽略,总时钟延迟由source latency和实际路径延迟构成。此外,文章还探讨了generate clock的源时钟概念及其应用场景,如时钟门控和PLL在时钟系统中的作用。

订阅专栏 解锁全文

订阅专栏 解锁全文

4440

4440

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?