PFD+CP,是频率合成器、时钟生成电路的主要设计方案

特点:当PLL失锁,可以锁频。

1. 工作原理

PFD结构基于状态机,可以记住之前的状态

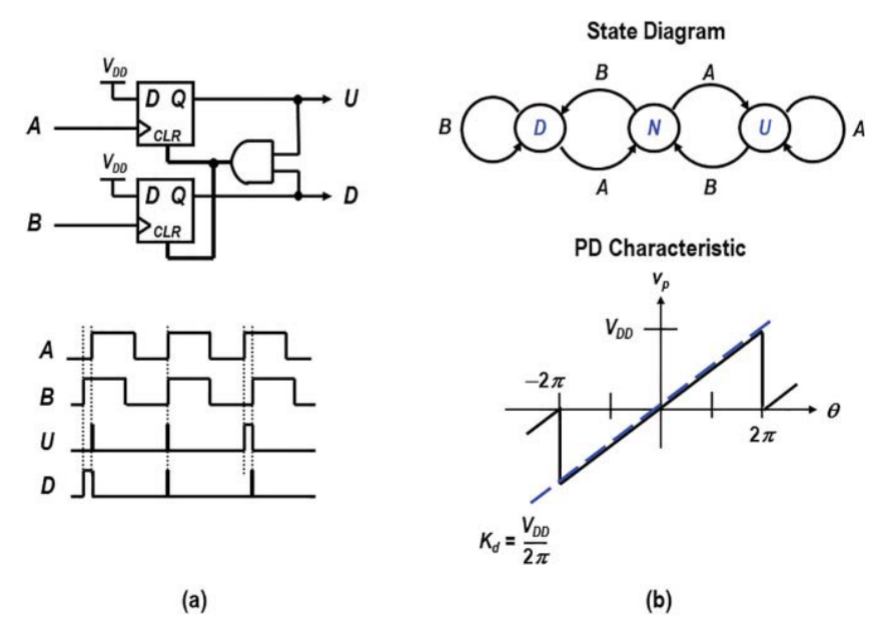

PFD结构

(a)PFD常见结构

由两个D触发器,和一个与门构成。

- 假设反馈时钟B较早到来,并且DFF由时钟B的上升沿触发。

- 由于每个DFF的 【D端口】 连接到电源电压,所以当时钟B的上升沿到达时,D输出高信号

- 参考时钟A的上升沿到达。一旦检测到时钟A的上升沿,U,变高。

- 与门的输出变为高状态,从而复位两个DFF。

D的脉冲宽度由两个时钟之间的相位偏移确定。

在PLL的相位锁定状态期间,PFD仅产生由PLL的固有锁定状态引起的小的逻辑毛刺,

PFD仅产生由反馈路径中的固有逻辑延迟引起的小的逻辑毛刺

与其他PD不同,PFD有三种状态(上、下、中性),在锁相状态下的相位偏移为0°

线性范围

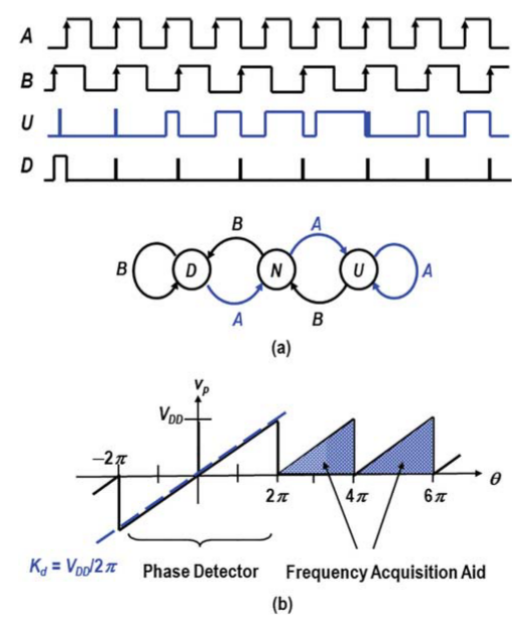

PFD辅助锁频

- 假设PLL在锁定范围之外

- 相位误差不受限制,并且随着时间推移进行周期滑移

- 与其他PD不同,PFD仅在 【时钟A的频率】高于 【时钟B的频率】 时的周跳期间产生向上信号U

- 如果【时钟A的频率】 低于 【时钟B的频率】 ,则PFD将仅在周跳期间产生下降信号D

任何类型2 PLL最终都可以通过拉入行为获得所需频率。

然而,PLL的拉入时间太长,没有用处。

因此,当在PLL中使用其它PD时,需要采用额外的频率捕获辅助电路。

PFD实际上作为【相位或频率检测器】而不是【相位和频率检测器】工作。

换句话说,PFD本身作为相位检测器或频率检测器工作 取决于 工作的边界。

- 当PLL在锁定范围内时,PFD作为正常PD工作,

- 当PLL在锁定范围外时,PFD通过生成正或负脉冲来执行频率检测。

- 严格地说,PFD成为频率采集辅助电路,而不是频率检测器,

- 因为PFD在失锁范围内的单极输出有助于频率采集,而不是代表频率差的量。

如图b所示

- PLL在小信号区域的相位检测和PLL在大信号区域的频率捕获辅助。

- 与触发器PD相比,PFD具有更宽的线性范围(

)和相同的PD增益(

)

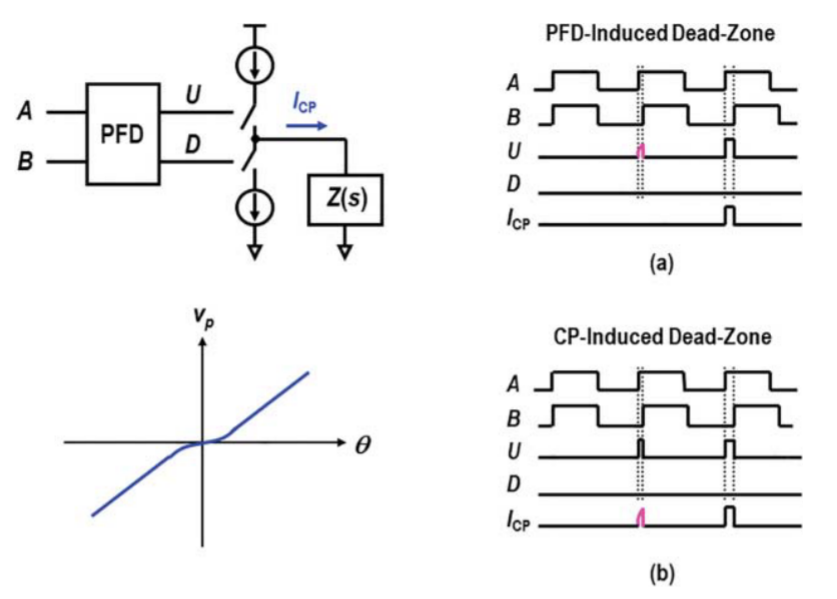

2. 死区问题

- 当相位误差接近零时,PFD产生非常窄的脉冲,其宽度太窄而不能完全开启电荷泵。

- 因此,电荷泵仅产生全电流的一小部分,导致PD增益较弱。

- 这种现象称为PFD死区。

- PFD的死区显着降低了环路带宽。

- 由于PLL的窄带宽不能很好地抑制VCO的相位噪声,

- 因此这种减小的带宽降低了带内噪声性能。

- 在电荷泵根本无法开启的极端情况下,

- PLL不提供任何反馈信息来校正VCO相位,

- 从而使PLL的带内相位噪声接近开环VCO的相位噪声。

死区分类:PFD引起的死区、CP引起的死区

CP-PLL中的死区效应可以分为两种:

- PFD引起的死区

- 电荷泵引起的死区

(b)电荷泵引起的死区

对于给定的负载电容,PFD引起的死区是由输出级(通常是反相器)的弱驱动能力引起的。

图(a)

PFD由于非常小的相位误差而产生的U信号电压电平不足,

没有打开电荷泵的上升电流的情况。

这个问题可以通过在PFD的输出级设置适当的晶体管尺寸来解决。

图(b)

电荷泵引起的死区问题更大

即使在PFD输出端设计了强缓冲器,由于电荷泵本身的开关时间有限,电荷泵可能无法在短时间内完全导通。

这主要是由于MOSFET开关的寄生电容和导通电阻。

电荷泵引起死区产生部分电荷泵电流,而PFD引起死区完全关闭电荷泵电流。

一旦遇到死区问题,PLL带宽的变化对工艺、电压和温度(PVT)变化极其敏感。

如果在PLL芯片的测试中,即使电源电压发生轻微变化,带宽也会发生数倍变化,则很可能PLL存在死区问题。

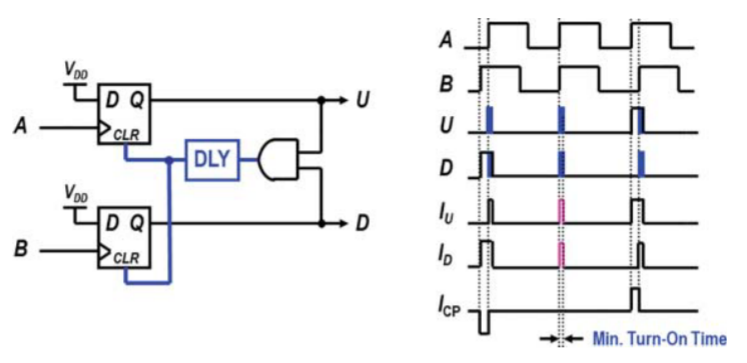

PFD死区解决办法

有一种简单的方法可以解决仅使用逻辑门的PFD的死区问题。

通过使上脉冲和下脉冲设置具有固定的最小脉冲宽度,

而不管相位误差如何,

可以使电荷泵即使在零相位误差的情况下也导通。

- 如图所示,这种操作可以通过在与门和复位输入端之间增加一个延迟单元来完成。

- PFD的最小导通时间Δton(turn-on time)使电荷泵在PFD产生U和D输出时都有电流流过。

- 如图所示,即使在锁相条件下,向上和向下电流IU和ID也会导通。由于两个电流具有相等的脉冲宽度,因此没有净电流从电荷泵流向环路滤波器。

最小导通时间Δton(turn-on time)是PLL性能的重要参数,应该和电荷泵一起被设计。

3. PFD开启时间对PLL建立的影响

当PLL处于锁定范围之外且出现周跳时,PFD用作频率检测器。

如果Tref与Δton的比值较低,则PFD的最小导通时间Δton会降低PLL的建立性能。

(B)Δton对PLL建立的影响

图(a)显示复位延迟如何影响PLL的建立时间。

- 如果Δton占参考时钟周期Tref的很大一部分,则图(a)所示的PD增益反转发生在相位差大于

的情况下,其中

。

- 当PLL使用高参考频率时,PD增益反转的部分可能很大。

- 在

的极端情况下,PFD表现为触发器PD。

图(B)显示了一个三阶2型PLL在相同Tref下不同Δton值的瞬态响应。

Δton/Tref值为12%的图显示出锁定范围之外的最低转换速率。

频率采集期间的大信号建立时间取决于PFD的最小导通时间。

4. PFD的噪声性能

CMOS数字电路工作在轨到轨信号区时的热噪声贡献比模拟电路工作在小信号区时的热噪声贡献小得多。

因此,与电荷泵相比,PFD对PLL的相位噪声贡献可以忽略不计。

另一个问题是电源噪声耦合,因为PFD由单端逻辑门组成。逻辑门的门延迟时间对电源电压变化高度敏感。

PFD可以在一定程度上提供电源抑制,因为它的工作方式类似于PLL中的伪差分模块

由于电源电压引起的延迟调制几乎同时影响U和D输出,因此在PLL中,U和D之差产生的净误差可以忽略不计。

- 为了提供更好的抗电源噪声能力,我们可以考虑采用全差分实现,即使是PFD。

- 然而,具有小信号电压摆幅的全差分PFD不是实现高分辨率或低功耗性能的好方法。

- 即使PFD工作在低参考频率,它仍然需要陡峭的上升和下降斜率,以实现良好的时序分辨率。

如果PFD采用电流模式逻辑(CML)电路设计,则需要巨大的偏置电流才能获得与CMOS标准逻辑电路相似的门延迟时间。

此外,具有小信号电压摆幅的差分PFD会带来时序抖动增加的潜在问题,而这在单端PFD设计中通常不是问题。

9180

9180

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?