由于具有噪声整形特性,ΔΣ调制器的量化噪声对小数N分频PLL的相位噪声的影响可以忽略不计。

当设计宽带PLL时,由于PLL的低通滤波不足,量化噪声可能会增加带外相位噪声。

高带外相位噪声可能会破坏某些无线系统中的频谱屏蔽,或者显著增加有线系统时钟的短期抖动。

抑制量化噪声的一种简单方法是在给定带宽下增加更多的高阶极点,但这会显著降低相位裕度,特别是在宽带PLL设计中。

必须通过附加电路来抑制量化噪声,以充分发挥宽带小数N分频PLL设计的优势。

文献中提出了几种方法,其中大多数被分为两类:

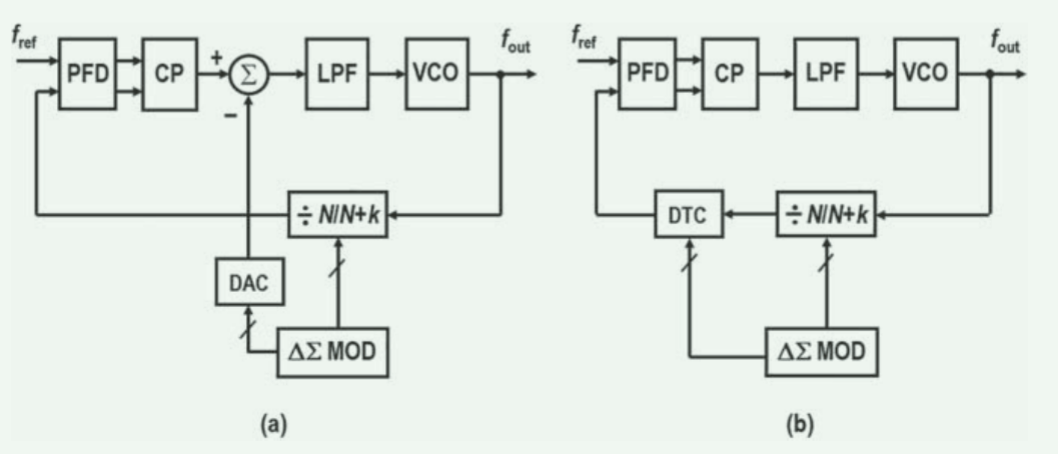

- 基于模拟域中的相位补偿

- 基于数字或混合信号域中的噪声滤波

1. 相位补偿

即使高阶ΔΣ调制器产生几乎不相关的输出,输出序列对于给定的控制字也是可预测的,如伪随机数发生器。

可以考虑在PD输出端进行直接相位补偿。

1.1 DAC补偿

消除ΔΣ调制产生的瞬时相位误差的一种简单方法是使用电流DAC补偿电荷泵输出端的残余电荷。

由电流DAC补偿的电荷量Qn:

- Δt是时间上的相位误差

- e是量化误差。

与采用几位累加器的传统小数N分频PLL不同,Δ Σ小数N分频PLL要求DAC具有较大的动态范围。

为了提高补偿性能,文献中提出了几种技术,包括动态元素匹配(DEM)和基于最小均方(LMS)算法的自适应校准。

电流DAC的电荷补偿不能完全消除电压涟漪,因为PFD通过时域中的脉宽调制来传递相位误差信息。

1.2 DTC补偿

因此,基于图(b)所示DTC的时域相位补偿方法将更为有效。

得益于先进的CMOS技术,如今具有背景数字校准的高分辨率DTC设计已经问世,实现了不错的降噪效果。随着数字密集型PLL(DPLL)架构的出现,已经提出了通过使用TDC、DTC或两者来降低噪声的各种方法。

1.3 多相环形VCO

多相环形VCO的使用也降低了量化噪声。

通过使用k个相位,量化步长将是原始大小的1/k,导致20 logk dB的量化噪声降低。

在高频下实现多相工作并保持良好匹配的线性度对于Δ Σ小数N分频PLL的性能至关重要。

通常,基于模拟域中的相位补偿的量化噪声降低在PVT角上遭受大的性能变化。

2. 噪声滤波

在集成电路中,在PVT变化上具有更好的最差情况性能和更差的最佳情况性能被认为比具有更好的最佳情况性能更有价值。

一个好的方法来减少带外量化噪声时,适度的降噪是足以满足系统的要求。

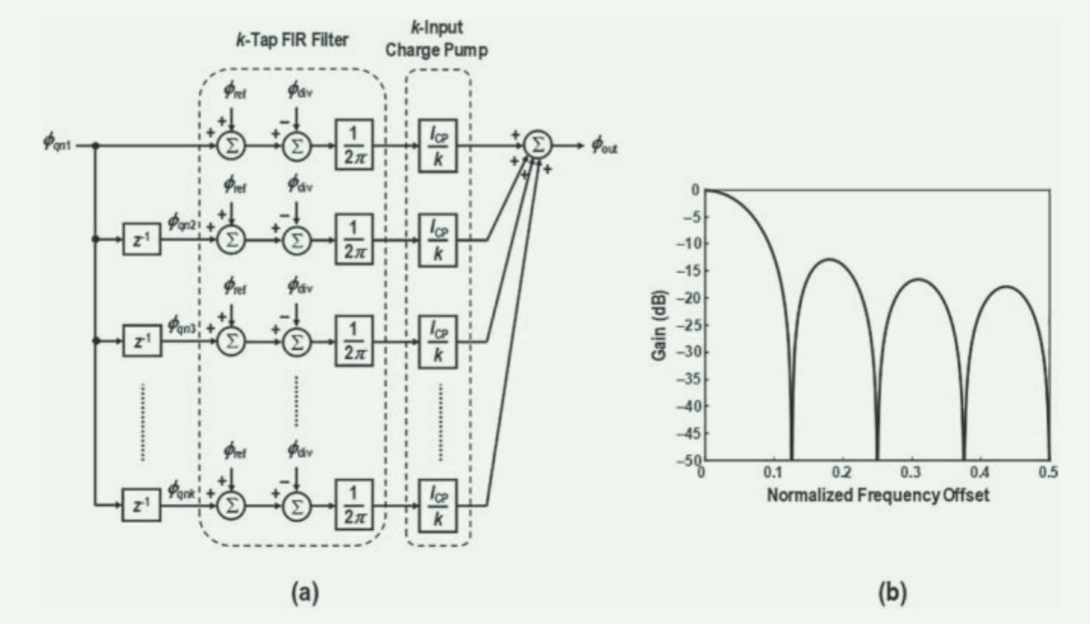

混合有限冲激响应(FIR)滤波方法,该方法可有效降低电荷泵输出端的高频量化噪声,同时在数字域中形成量化噪声的噪声传递函数。

由于FIR滤波在并行路径中执行,不会在环路中产生任何延迟,因此不会影响PLL的环路动态特性。

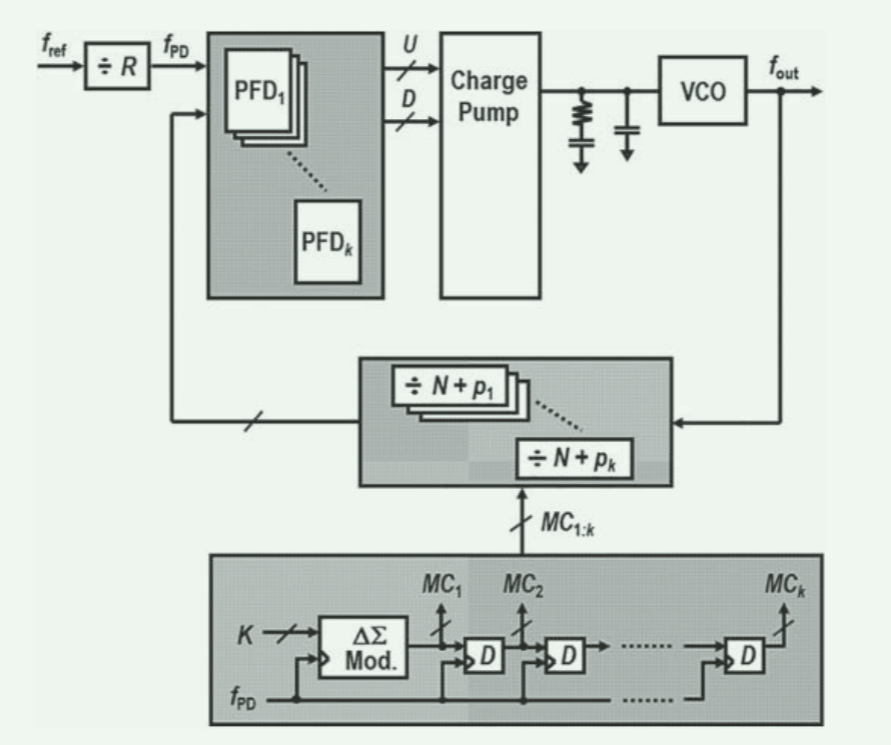

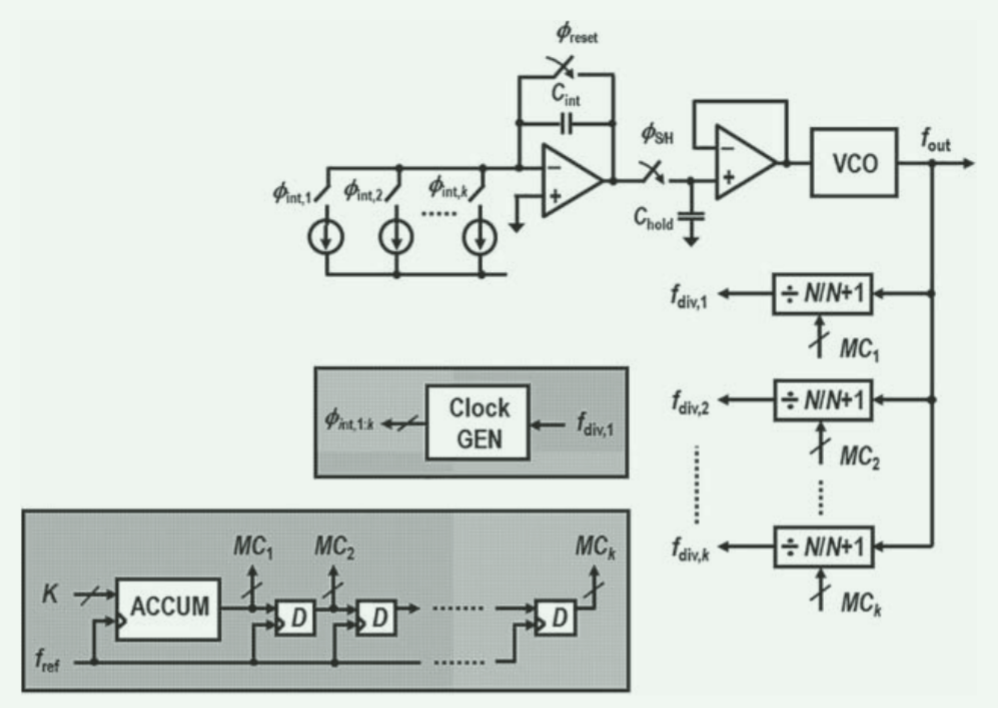

为了实现混合FIR滤波器,使用了多个PFD、多输入电荷泵和多模分频器(MMD)。

- PFD和MMD的数量设置FIR滤波器抽头的数量。

- ΔΣ调制器的输出被加载到D型触发器(DFF)中,

- 然后由随后的DFF顺序移位。

- 并行的多个MMD由来自DFF的顺序控制位控制

- 并行路径中的每个PFD产生相位误差,该相位误差被馈送到多输入电荷泵

- 来自并行路径的相位误差在多输入电荷泵的输出端相加,

- 实现针对ΔΣ调制器量化噪声的FIR滤波器。

频率偏移Δf处的电荷泵输出可以推导为:

:参考信号的相位

:分频器的相位

:量化噪声

:调制器输出的延迟深度

:多输入电荷泵的每个分支的电流

:参考频率

:FIR滤波器的传递函数

FIR滤波器仅针对量化噪声进行滤波

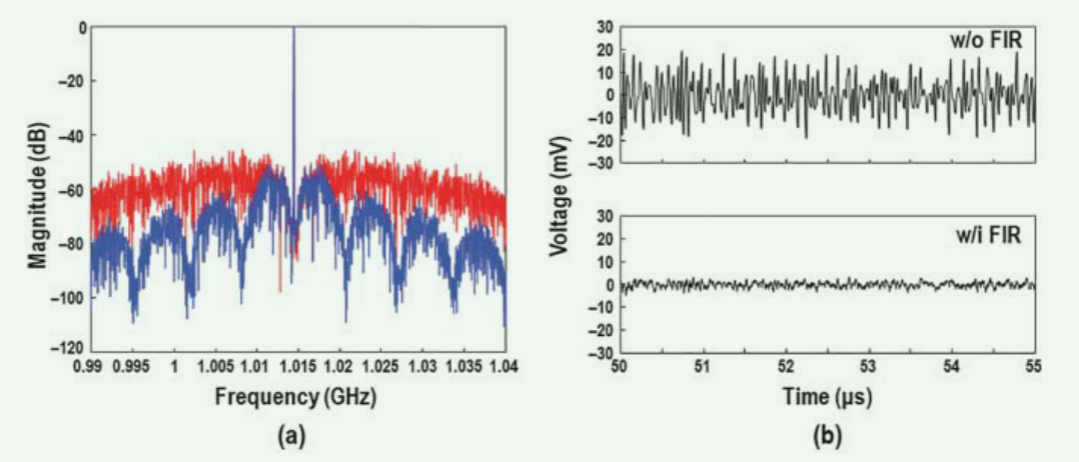

混合FIR滤波器对输出频谱的影响以及PLL在时域中的瞬时相位误差。

PLL的高阶极点被放置在高于最佳位置的位置。

图(a)显示了两个小数N分频PLL的输出频谱;

- 上面一个没有FIR滤波器,

- 下面一个有FIR滤波器。

- 可以清楚地看到,FIR滤波器大大降低了高频相位噪声。

如图(b)所示,

- 在电荷泵输出端对所有相位误差求和后,峰峰值相位误差也显著减小,

- 这有利于电荷泵电路的线性度。

- 多输入电荷泵的时间交错操作可以进一步增强线性度,从而改善带内噪声和分数杂散性能。

混合FIR滤波方法通过简单地实现多个分频器和PD提供了一种简单的降噪方法。

噪声降低是通过半数字滤波方法完成的,可以很好地预测量化噪声抑制,而对PVT变化的依赖性较小。

当采用相位选择多模分频器时,FIR滤波电路的功率和面积可以与先进的CMOS工艺成比例。

例子:使用FIR滤波器降低量化噪声

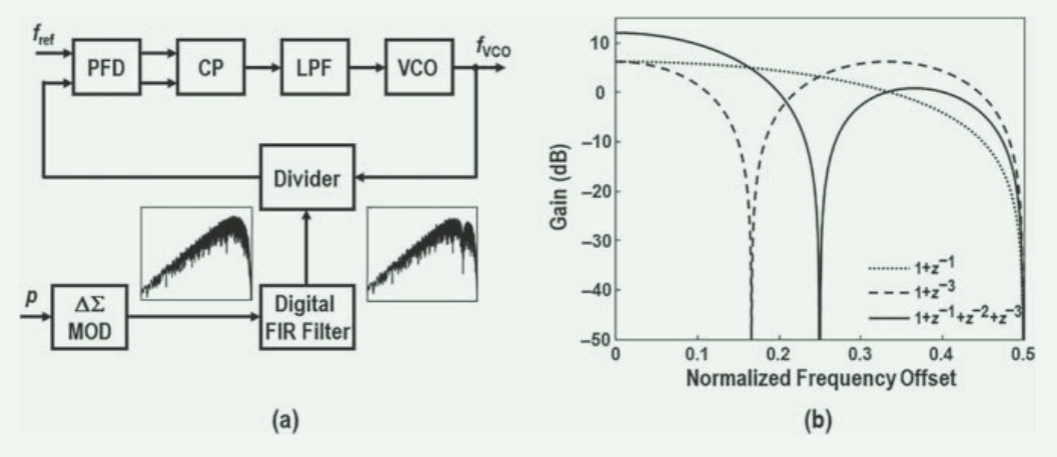

采用数字Δ Σ调制器,可以考虑在数字调制器的输出端使用数字FIR滤波器,而不是在电荷泵的输出端使用混合FIR滤波器。

如图(a)所示,数字FIR滤波器置于Δ Σ调制器的输出端,高频量化噪声被滤波器抑制。

这种方法不会受到任何模拟失配的影响。

诸如1/2的分数系数可以仅通过比特移位来实现。

在这种操作过程中,数据的LSB将丢失,从而导致截断误差。

- 数字FIR滤波器的传递函数可以仅采用整数系数,这导致DC增益。

- 例如,考虑一个单级数字FIR滤波器,其传递函数由(

)给出。

- 与混合FIR滤波器不同,数字FIR滤波器在z = 0时具有6 dB DC增益。

图(B)显示了不同阶数的数字FIR滤波器的噪声传递函数。

尽管增加FIR滤波器的阶数会使高频滚降更陡

但增加的增益会使高阶数字滤波器在小数-N PLL设计中对量化噪声抑制不那么有效。

例子:利用S/HPD抑制模数杂散

FIR滤波方法还可用于有限模小数N分频PLL中的杂散降低。

使用S/H PD在电压域中实现了良好的相位误差消除。

多输入S/H PD电路设计紧凑,假设完全匹配时,不会产生高频电压波纹。

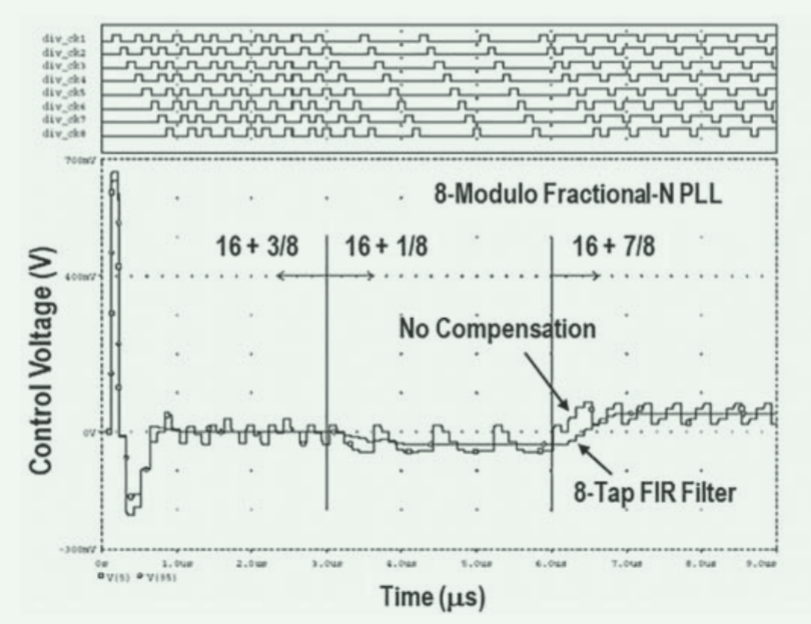

带3位累加器的8模小数N分频PLL以八分之一的参考频率产生周期性音调。

由于8抽头FIR滤波器在八分之一参考频率的整数倍处产生零点,可以抑制所有小数杂散。

分频比变化为(16+ 3/8)、(16+ 1/8)和(16+ 7/8)

当FIR滤波器使能时,可以完全消除周期信号音。

在使用PFD的情况下,由于脉冲宽度调制,无法实现完全杂散降低,但FIR滤波技术仍可用于显著降低小数杂散。

5157

5157

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?