ΔΣ调制技术不仅在数据转换领域,而且在时钟和频率产生领域都已成为一种重要的技术。

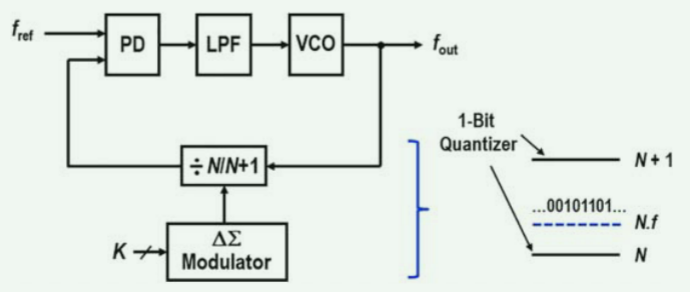

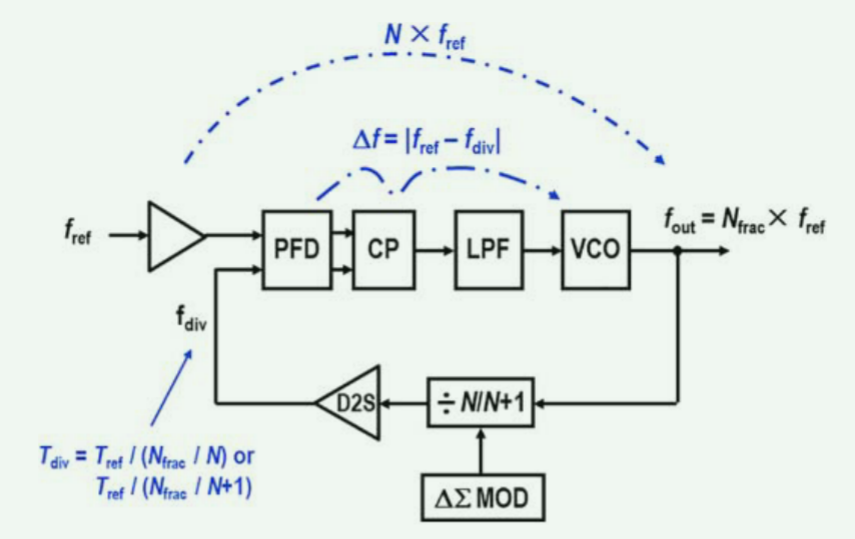

是使用过采样Δ Σ调制器,通过整数分频器内插小数频率。

- 由于Δ Σ调制器的噪声整形特性,Δ Σ小数N分频PLL在载波附近具有良好的相位噪声,

- 而传统的有限模小数N分频PLL在VCO频率越高时杂散抑制越困难,

- 而Δ Σ小数N分频PLL的频率分辨率不依赖于VCO频率,不存在同样的问题。

- 通过简单地增加调制比特数,可以获得非常精细的频率分辨率。

- 如果使用20位Δ Σ调制器和10 MHz参考时钟,则PLL输出端的频率分辨率可小于1 Hz。

- 利用如此精细的频率分辨率,

- 如果动态调制Δ Σ调制器的控制输入,则也可以在Δ Σ小数N分频PLL的输出端实现频率调制。

Δ Σ小数N分频PLL的主要特性总结如下:

- 高阶调制无杂散随机化

- 带内相位噪声贡献低,具有噪声整形功能

- 通过数字过采样实现高频率分辨率

- 可选直接数字频率调制

Δ Σ分频PLL,频率合成器的整体性能得到了显著的提高。

此外,Δ Σ PLL调制方法使小数N分频PLL能够执行直接数字频率调制,以实现低成本发射机设计,使小数N分频PLL成为现代收发器系统中的关键构建模块。

1. 𝚫𝚺 调制器

随着先进CMOS技术的发展,高速数字电路的功耗和面积变得越来越不重要

采用ΔΣ调制的过采样数据转换器被广泛用于高分辨率数据转换。

- 冗余输出位可使系统在模拟不匹配导致的可能位错误方面具有鲁棒性。

- 噪声整形特性通过使用抽取滤波器滤除高频量化噪声来提高信噪比(SNR)。

将ΔΣ调制用于小数N分频频率合成还可缓解PLL的模拟设计约束,并提供优于标准方法的多个优势。

在传统的ΔΣ ADC理论的基础上,讨论其基本工作原理和量化噪声的影响。

1.1 𝚫𝚺 ADC和量化噪声

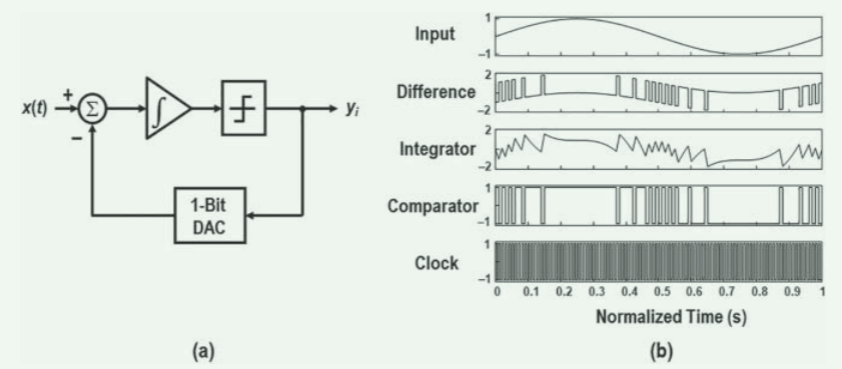

将量化器的输出与输入信号进行比较,由积分器累积差信息。

根据描述的方式,即“基于框图的差(Δ)然后积分(Σ)。

ΔΣ ADC的关键特性是过采样和噪声整形,这无需高性能运算放大器即可实现高SNR或高分辨率。

1位量化器的使用增加了环路中的非线性,特别是对于高阶调制器,需要仔细设计。

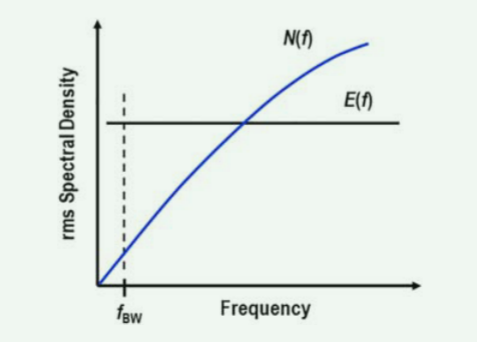

通过在前馈路径中具有积分器,量化噪声将被反馈系统的噪声传递函数高通滤波,从而表现出噪声整形特性。该特性类似于PLL内VCO噪声的高通滤波特性。

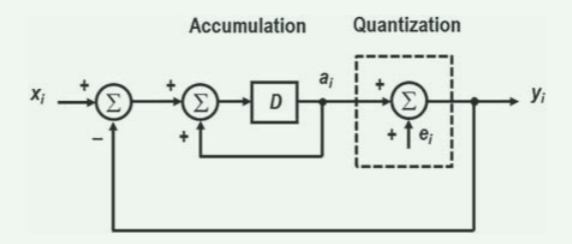

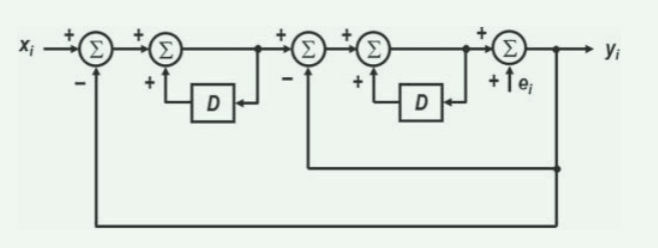

分析基于采样数据模型的量化噪声的影响,其中积分器被累加器代替,如图所示。

对于输入信号xi,量化输出yi:

- 其中ai是累加器的输出

- ei是量化误差

公式表示ΔΣ调制器对量化误差进行微分,除采样延迟外,不影响输入信号。

假设量化误差表现为白色噪声,调制噪声ni:

调制噪声N(f)的谱密度:

是

的谱密度

- T是采样周期,采样频率fs的倒数

是量化误差

的均方根值

信号频带中的总噪声功率:

总噪声功率的rms值:

OSR加倍,SNR改善9 dB

1.2 高阶调制器

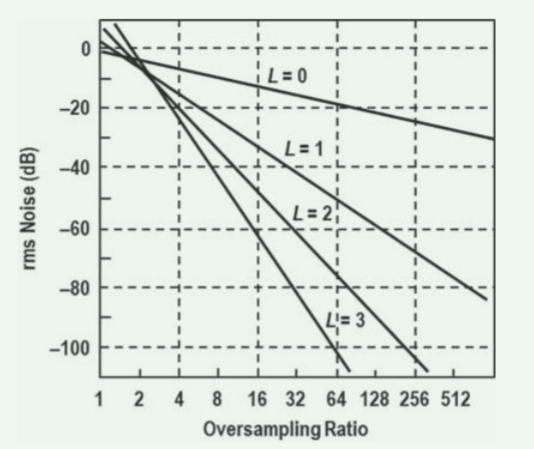

当考虑高阶Δ Σ调制器时,SNR可以进一步提高。

量化输出:

调制噪声被表示为量化误差的2阶微分。

调制噪声的谱密度:

假设一个忙碌输入信号,N(f)的绝对值变为:

的rms值:

二阶调制器在采样频率每增加一倍,信噪比提高了15 dB,

一阶调制器在采样频率每增加一倍,信噪比提高了9 dB。

对于给定的OSR,更高阶的环路可以显著改善SNR性能。

高阶调制器的调制噪声可通过增加更多反馈环路来获得。

对于L阶调制器,调制噪声的频谱密度NL(f):

no的 rms值为:

采样速率每增加一倍,SNR就提高3(2L − 1)dB

在ΔΣ ADC设计中提供(L− 0.5)额外位分辨率。

高阶调制器对输入动态范围和环路动态稳定性有一些限制,需要仔细设计。

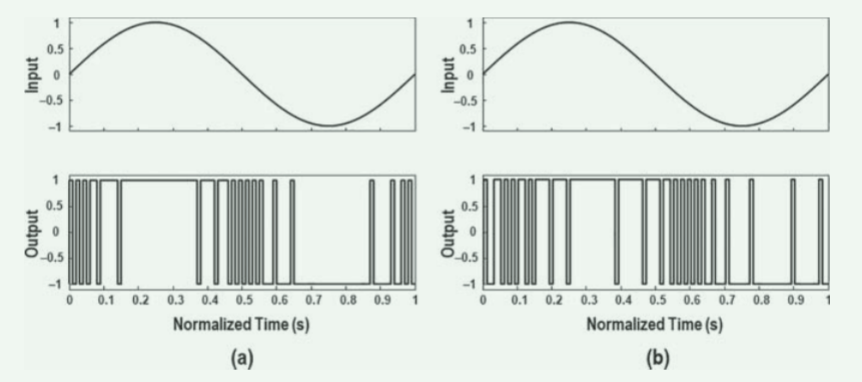

调制器的输出取决于输入信号的脉宽调制信号。

与一阶调制器的输出相比,二阶调制器的输出在平均保持相同水平的同时,表现出更多的高频波动。

1.3 级联调制器

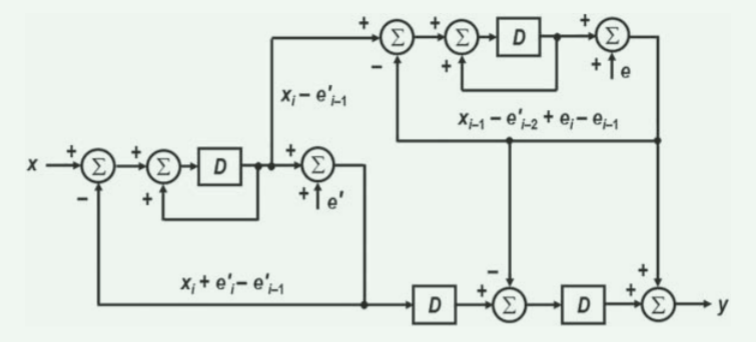

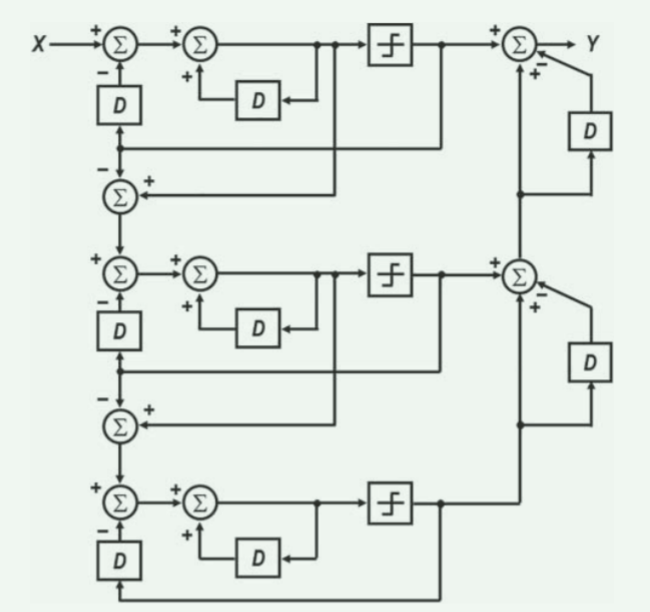

高阶Δ ∑调制器也可以通过级联一阶调制器来实现,如图所示。

级联调制器也被称为“多级噪声整形”(MASH)调制器。

- 第二级调制器采用第一级“多级噪声整形”(MASH)调制器的积分器输出

- 第二级调制器将第一级调制器的积分器输出作为输入

- 从第一级调制器的输出中减去第二级调制器的输出

- 从而消除第一级调制器的量化噪声

- 在最后一级中添加第二级调制器的输出之后

- 剩余的噪声是来自第二级调制器的量化误差的第二差

考虑误差因子g,则:

e':第一级量化器中的量化误差

在理想的匹配和线性度下,g变为1

在实践中难以使误差因子g接近于1。

噪声整形性能受到来自第一级调制器的噪声拖尾的限制,并且使用高阶MASH调制器几乎没有优势。

- MASH调制器通常与高阶单环Δ ∑ 调制器(SLDSM)结合使用。

- 可以通过在二阶SLDSM之后跟随二阶MASH调制器来设计具有两级拓扑的四阶ΔΣ调制器。

对于ΔΣ小数N PLL,采用全数字ΔΣ调制器。数字MASH调制器可以具有单位g。

2. 用于小数N频率合成的全数字锁相环ΔΣ调制器

对于分数N频率合成,由于调制器的输入和输出都是数字的,因此设计了一种全数字Δ ∑调制器。

Δ ADC中的积分器被累加器取代,1位量化只需取累加器的进位输出即可完成。

有效过采样比【】可以由PD频率【

】与PLL噪声带宽【

】的比率来定义

- 因此,高【

】或低【

】都有利于通过具有高OSReff来降低量化噪声。

- 请注意,使用Bn而不是系统传递函数的3 dB频率,来分析动态范围性能。

- PLL的阶数应高于Δ PLL调制器的阶数,因为量化噪声由PLL的低通滤波器(LPF)特性过滤。

频率合成器的Δ ∑调制器设计有一些不同的方面。

- 它是一个全数字调制器,调制器的系数可以精确设置。

- MASH调制器不具有来自第一级的由于不完美的增益失配而导致的噪声拖尾问题

- 数字MASH调制器因其简单的实现和有保证的稳定性而成为Δ N小数N PLL的主导架构

- 分数N PLL的调制器设计仍然面临匹配和非线性问题

- 因为当与PLL组合时,数字信息被转换成模拟域中的相位误差

2.1 MASH调制器

| 由级联的一阶调制器组成的MASH调制器具有固有的稳定性 使得MASH调制器的输入范围得到充分利用。 | 当输入值接近调制器输入范围的上电平或低电平时 SLDSM会使累加器的输出饱和,从而面临稳定性问题。 |

| 在没有反馈或前馈路径的情况下,高阶MASH调制器的设计相对容易,因为不需要仔细选择环路参数 | |

量化噪声在z域中表示:

高阶MASH调制器通过消除前一级的残余噪声而具有高阶噪声整形。

对于n阶调制器,噪声传递函数(NTF):

分数N PLL的这种架构的缺点是,

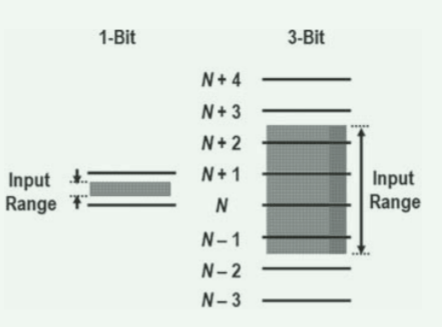

- 高阶调制器生成较多的输出位模式,n阶MASH调制器具有n位输出

- 三阶和四阶MASH调制器分别需要8模和16模分频器

- 分布广泛的位模式不仅增加了多模分频器的设计复杂性,也增加了PD的设计复杂性

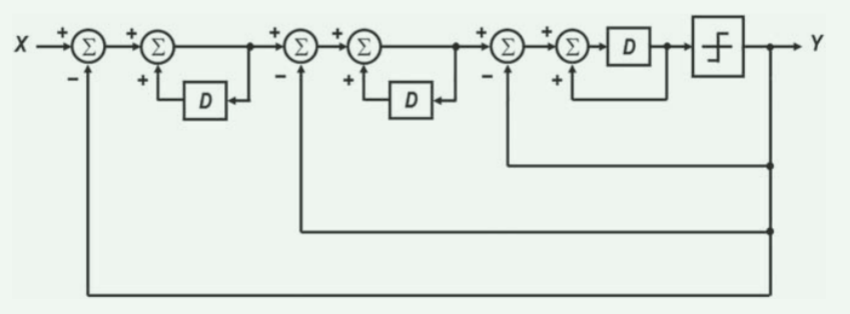

2.2 带1位量化器的SLDSM

由于单比特量化器仅产生两级输出,可以在小数N分频PLL的设计中使用双模分频器。

三阶SLDSM的噪声传递函数NTF:

n阶SLDSM的NTF与MASH调制器的NTF相同。

在SLDSM的情况下,可以通过添加前馈和反馈系数来设计不同的NTF。

- 可以基于已知类型的高通滤波器来设计定制的NTF,

- 以进一步抑制高频区域中的量化噪声。

- 一个例子是一个三阶巴特沃思高通滤波器,它具有平坦的通带增益,并且在高频下的NTF实现了更多的量化噪声降低。

小数N分频PLL的SLDSM的主要缺点是调制器的输入范围由于稳定性而受到限制。

对于高阶SLDSM,有限输入范围的问题变得更加严重。

无法使用双模分频器的满量程范围,从而导致小数N分频频率合成的死区问题。

- 一种可能的解决方案是使用高参考频率或通过使用N/(N+ 2)双模分频器而不是N/(N+ 1)双模分频器来扩展量化器电平。通过将整数边界与由(N+ 1)/(N+ 3)双模除法器设置的量化器电平重叠,可以以增加量化噪声为代价覆盖所有信道范围。

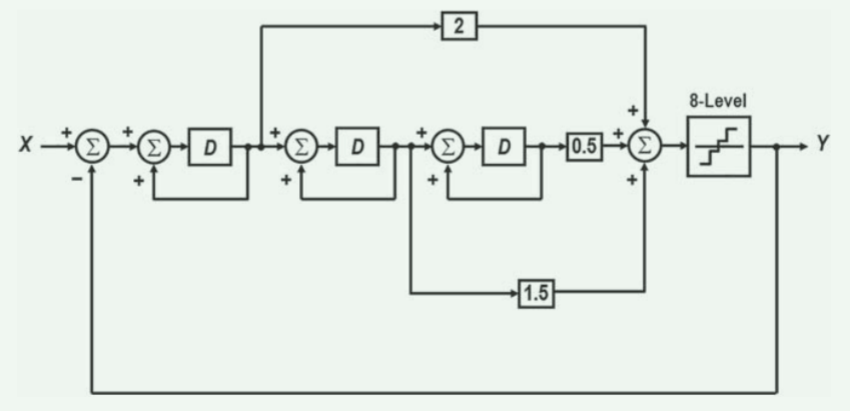

2.3 带多级量化器的SLDSM

如果SLDSM设计有多电平量化器,则可以解决由于有限的输入范围而导致的Δ Σ小数N PLL的死区问题。

8量化电平的有效分频范围:{N,N+1}到 {N-3, N-2, N-1, N, N+1, N+2, N+3, N+4}

请注意,总量化噪声功率几乎相同,最小量化误差仍由VCO的单个周期设置。

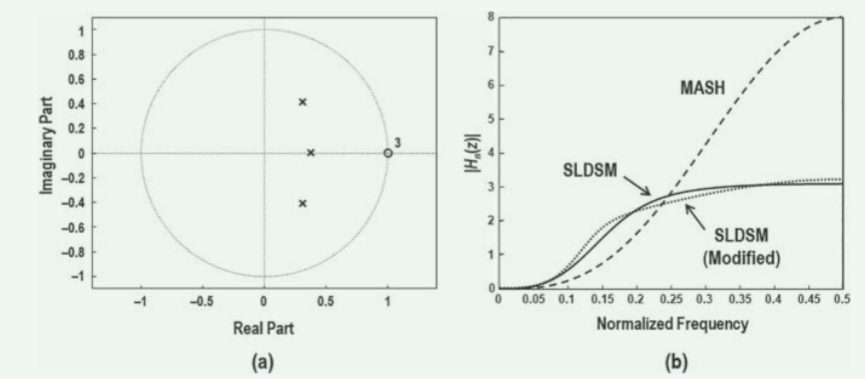

图中SLDSM的实际NTF:

用于频率合成的N/(N+ 1)双模分频器所占用的实际范围约为八电平量化器全范围的12%,该范围足够低以确保三阶SLSDM的良好稳定性。

SLDSM具有前馈系数,可实现定制的NTF,例如具有平坦通带增益的巴特沃思高通滤波器。

基于巴特沃思滤波器设计,NTF可以设计为:

- 为了稳定,NTF的极点应该在z域的单位圆内,如图(a)所示。

- 与MASH调制器相比,低Q巴特沃思极点显著降低了高频整形噪声能量,如图(b)所示。

在频域中减少的高频噪声导致在时域中的低扩展输出比特模式。

在多电平输出SLDSM的设计中,使用更多数量的量化器电平允许NTF的更高的通带增益。

结果,对于相同的噪声功率,NTF的转角频率可以进一步增加。

可以利用多级量化器更多地抑制低频中的量化噪声。

例如,图(b)所示的NTF的通带增益为3.1,转折频率为时钟频率的0.18倍。

SLDSM的噪声传递函数需要满足的条件

为了保证高阶SLDSM的稳定性和噪声性能,NTF必须进行精心的设计。

为了得到一个有效的NTF,SLDSM的NTF必须满足三个条件:

第一个是防止无延迟循环的因果关系条件;否则,SLDSM电路不能实现,因为无延迟环路不存在于硬件中。

通过将Hn(z)的分子和分母多项式的前导系数设置为1,可以满足因果关系要求,或者

也就是说,分子中的常数与分母中的常数之比必须正好为1

第二个条件是小信号稳定性。NTF的极点必须在z域的单位圆内。

即使数字调制器精确地控制系数,必须仔细检查极点的位置。

第三个条件是大信号或非线性稳定性,这与输入动态范围有关。

非线性稳定性的实验研究表明,通带增益应加以限制。

- 基于巴特沃思高通滤波器的NTF设计是在通带上具有平坦频率响应的良好选择

- 它还降低了高频噪声能量,从而产生低扩展输出位模式。

- 对于给定的滤波器,一旦设定了转折频率,就确定了通带增益。

- 不存在选择系数以满足因果关系和通带增益要求的自由度。

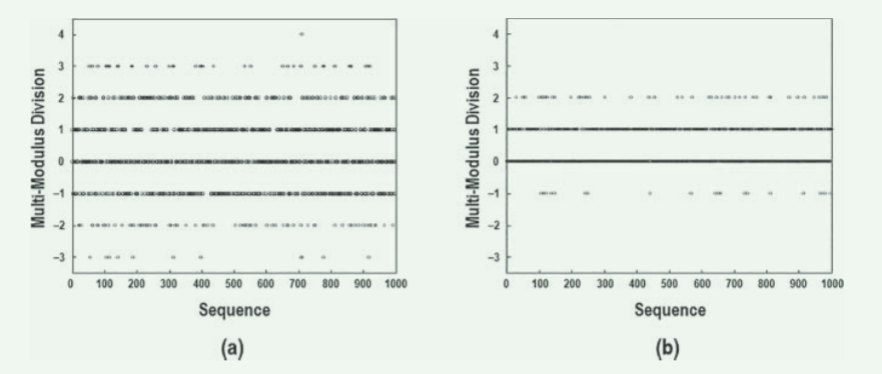

MASH和SLDSM的输出对比

MASH调制器呈现出比SLDSM更大的模式。

三阶MASH具有3位输出,输出位最多分布在8个电平上。

相反,即使三阶SLDSM也具有八电平量化器,输出比特范围也主要限于1,000个样本上的4个电平。

仿真结果验证了频域高频噪声功率的降低会导致时域的扩展方向图减小。

3. 量化误差引起的相位噪声

假设量化误差是均匀分布的。

噪声功率由最小量化器电平的1/12给出。

使噪声功率在PD频率【】的带宽上扩展,z域中的频率波动【

】与NTF Hn(z):

相位波动【】是频率波动的积分,

如果

是双边带功率谱密度,则单边带功率谱密度

与

一样。

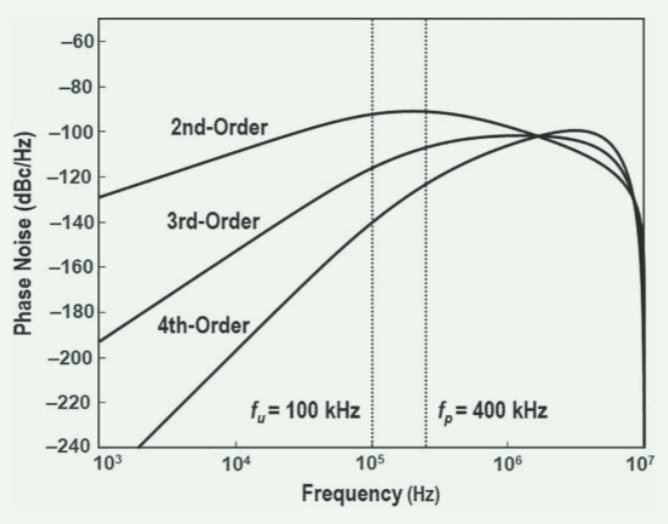

将其转换到频域并推广到任何调制器阶数,将量化误差的相位噪声表示为:

m是调制器的阶数

| 调制器阶数 | 相位噪声斜率(dB/dec) |

| 二阶 | 20 |

| 三阶 | 40 |

| 四阶 | 60 |

如果假设PLL带宽为100 kHz,极点频率为400 kHz

- 即使四阶调制器的带内噪声比其他调制器低得多,但高频相位噪声抑制仍不足以抑制四阶调制器。

- PLL的阶数应高于Δ PLL调制器的阶数,以便量化噪声在高频处逐渐降低。

- 如果带外相位噪声对某些无线应用很重要,则需要以降低相位裕度为代价添加高阶极点,

- 或者进一步降低环路带宽。

- PLL输出端的相位噪声贡献与分频比无关。

- 这是因为双模或多模分频器会吞下周期与VCO相同的脉冲

- 换句话说,相位域中的最小量化电平由VCO的周期设置,使得ΔΣ调制器的相位噪声贡献与分频比无关。

- 另一种减轻量化噪声效应的有效方法是为Δ Σ调制器使用高时钟频率。

- 可以在参考时钟路径中设计倍频器电路,以使PD频率加倍。

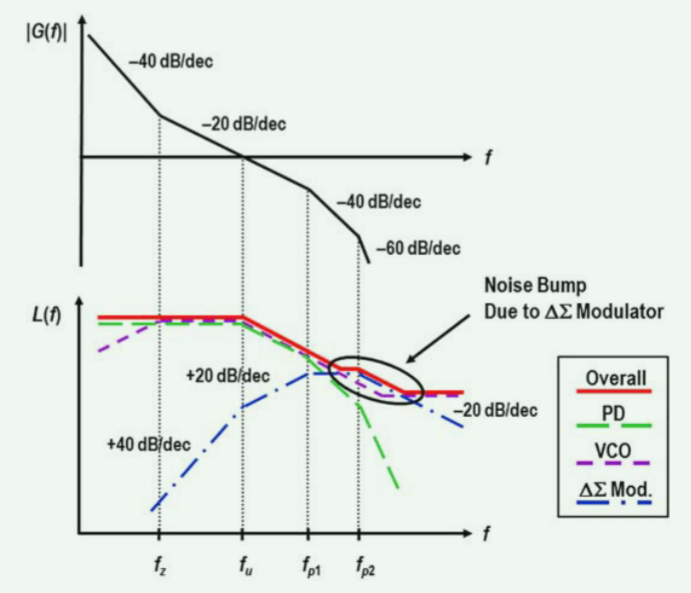

例子:ΔΣ分数锁相环的环路动态

在ΔΣ小数N分频PLL设计中,确定ΔΣ调制器的相位噪声贡献对于优化相位噪声至关重要。

由于量化噪声是由分频器调制产生的,因此PLL具有针对量化噪声的低通滤波器传递函数。

- 量化噪声的贡献不取决于分频比,因为分频器调制具有一个VCO时钟周期的分辨率。

- 如果PLL不受PD非线性的影响,ΔΣ调制器产生的带内相位噪声远低于其他噪声源。

- 如果环路带宽不够窄,带外相位噪声可能由ΔΣ调制器决定。

量化噪声如何通过噪声凸起影响PLL的带外相位噪声的示例。

- 三阶调制器的相位噪声呈现出40 dB/dec的噪声斜率,

- PLL的第三极点之后具有平坦的噪声响应,

- 从PLL的第四极点开始降低。

这种高频噪声平台是宽带ΔΣ小数N分频PLL的独特特性。

与传统小数N分频锁相环中的杂散抑制方法一样,宽带ΔΣ小数N分频锁相环的设计也需要考虑量化噪声抑制方法。

例子:量化噪声影响

考虑一个带有三阶Δ Σ调制器的四阶PLL,并假设环路参数、参考频率和输出频率保持不变。

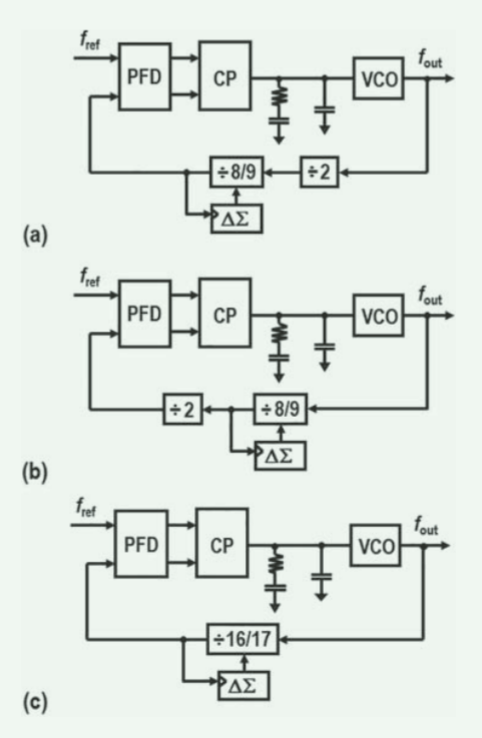

唯一的区别是PLL内Δ Σ调制的位置。

- 电路采用2分频电路,后接8/9双模分频器,反馈通道采用Δ调制;

- 电路采用8/9双模分频器,后接2分频电路

- 只有16/17双模分频器

- 相位域中最小量化误差仍为一个VCO周期,因此双模分频器本身不会放大Δ Σ调制器的量化噪声。

- 但是,如果8/9双模分频器在反馈路径中跟随2分频电路,

- 则8/9双模分频器将以两个VCO周期执行ΔΣ调制,导致VCO输出端的相位噪声增加6 dB

图(a)中的PLL比图(b)中的PLL具有更差的噪声性能。

- 使用16/17双模分频器,也会以等于一个VCO周期的最小量化误差进行调制。

- 因此,VCO输出端的量化噪声不会导致相位噪声增加6 dB。

- 图(b)中Δ ∑调制器的时钟频率是参考频率的两倍

- Δ ∑调制是在2分频电路之前进行的。

- 调制器在PLL带宽内的量化噪声可以通过更高的PD频率来降低。

图(c)中PLL的量化噪声应该比图(b)中的量化噪声更差。

Δ Σ调制器之后的2分频电路将在分频器输出端引起混叠效应,从而显著增加带内相位噪声。

图(c)中的PLL具有最佳噪声性能。

图(c)噪声性能最好,图(b)次之,图(a)最差

4. 动态范围和带宽

- 在分数N频率合成器中,Δ Σ调制器的量化误差表现为相位噪声,

- 但它可以作为Δ Σ数据转换器的电压噪声进行分析。

- 通过使用Δ ADC的成熟理论,可以在频域中定义Δ Σ ADC调制的动态范围,并推导出给定积分相位误差的PLL带宽上限的闭环方程。

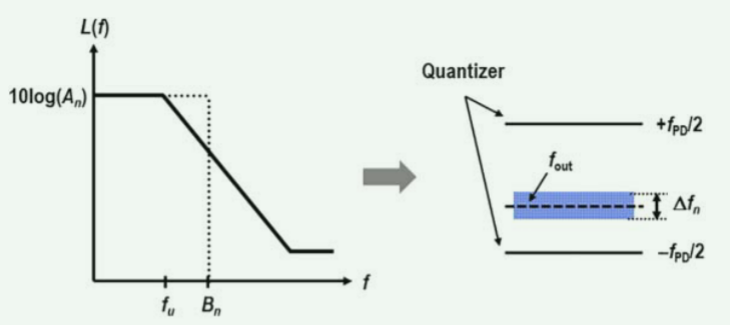

如何定义Δ Σ调制的动态范围以及小数N分频PLL设计的带宽和带内噪声要求的概念图。

如果给定以为单位的带内相位噪声An和噪声带宽Bn,则Bn内的积分频率噪声Δfn计算为

f1为最小噪声积分频率,假定f1 ≤ Bn。

如图所示,量化器电平在频域中用和

表示。

基于ADC中L阶Δ Σ调制器的动态范围要求,

针对分数N PLL中的L阶Δ Σ调制器获得类似的推导,其中动态范围由与

的比率设定。

积分相位误差是:

噪声带宽的近似上限:

对于过阻尼环路,Bn近似为单位增益频率fu乘以

PLL带宽的上限:

例如,如果使用三阶ΔΣ调制器,则量化噪声在PLL的第四极点之后逐渐减小,而不是在Bn之后逐渐减小。

高阶极点的作用不仅对杂散抑制很重要,而且对Δ Σ小数N分频PLL设计中的量化噪声降低也很重要。

5. 非理想效应

与整数N分频PLL不同,Δ Σ分频PLL存在PD非线性和耦合问题。

- PD非线性会降低带内相位噪声和分数杂散性能

- 当输出频率接近参考频率的整数倍时,耦合会导致严重的杂散产生。

5.1 非线性

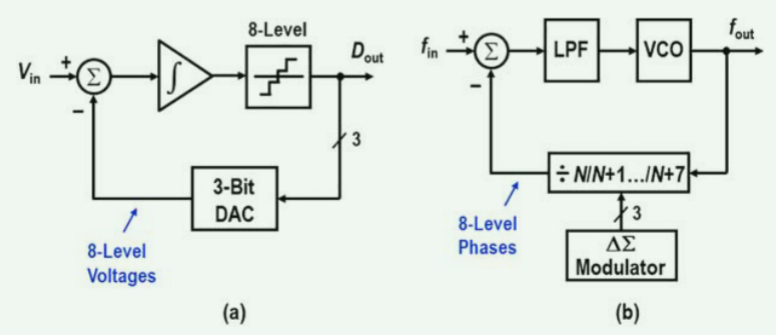

考虑一下Δ Σ小数PLL是否类似于Δ Σ DAC或Δ Σ ADC。

前一种情况是合理的,因为数字Δ Σ调制器的输出控制PLL的模拟相位。

在这种情况下,很难理解Δ Σ分频PLL的非线性问题。

(b)采用三阶MASH的Δ Σ小数N分频PLL

两者均采用8电平量化器和三阶Δ Σ调制器。

八电平量化器类似于8模除法器,三阶Δ ∑调制器生成多达八个量化相位。

在设计CP-PLL时,电荷泵是在环路滤波器处将多个相位转换为多个电压的模块。

电荷泵的作用类似于ΔΣ ADC中的多位DAC。

在采用多电平量化器的ΔΣ ADC中,多位DAC的线性度对于决定ΔΣ ADC的整体性能至关重要。

电荷泵的非线性在小数N PLL中显著地恶化了Δ Σ小数N PLL的性能。

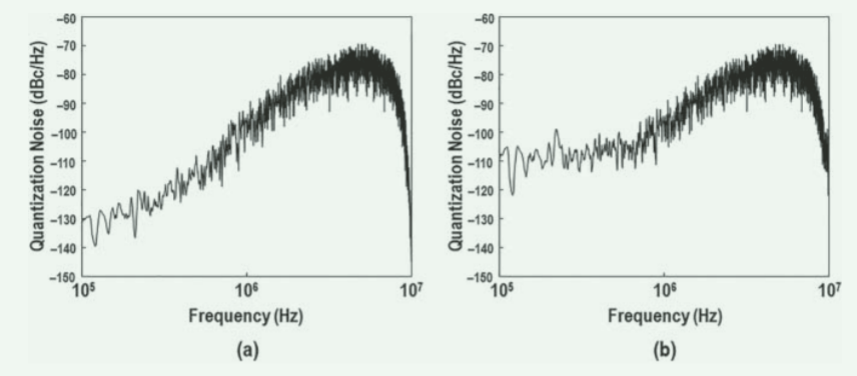

- 使用带有三阶MASH调制器的四阶小数N分频PLL

- 小数分频比为1/32

- 参考频率为10 MHz

- PLL带宽为1 MHz

为了只关注量化噪声,图中显示的是多模分频器输出端的相位噪声图,而不是VCO输出端的相位噪声图。

- 当使用理想电荷泵时,分频器输出端的相位噪声显示出清晰的噪声整形,没有任何小数杂散,如图(a)所示

- 然而,当电荷泵非线性增加10%时,带内相位噪声严重降低,如图9.29(b)所示。

在312.5 kHz(=1/32×10 MHz)的偏移频率处观察到分数杂散。

遇到非线性问题时,使用高阶Δ ∑调制器并不一定能改善噪声和杂散性能。

5.2 分数杂散(整数边界杂散)

在整数N分频PLL中,参考杂散的产生很容易理解。

Δ Σ小数N分频PLL的杂散产生相当复杂,很难在电路级仿真中预测。

当PLL输出调谐到参考频率的整数倍附近时,可以很好地观察到小数杂散的出现。

分数杂散通常被称为整数边界杂散。

整数边界杂散主要由三种机制引起:

- PLL的非线性

- Δ Σ调制器

- 耦合

Δ Σ调制器

理论上,高阶Δ ∑调制器不产生空闲音调。

在数字调制器的设计中,特别是当控制字接近有理数时,来自数字调制器的有限序列长度可以产生空闲音。

例如,1/8的小数分频比仅激励最高有效位(MSB)的三个位,导致小数杂散位于参考频率的八分之一处。

缓解空闲音调的常见方法是对控制字应用抖动,这会扩展序列长度。

一种简单的抖动方法是始终将最低有效位(LSB)设置为高。

- 等于最小分辨率频率的偏移频率被添加到期望频率以解相关量化误差。

- 例如,使用24位MASH调制器和10 MHz时钟频率时,1 LSB对应的频率误差小于1 Hz,或1 GHz输出时小于0.001 ppm。

- 然后,使用(

)的有效分数分频比,这不影响输出频率的精度。

为了进一步扩展序列长度,还可以考虑动态抖动方法。

- 当分数分频值被设置为诸如1/2或1/4的大有理数时,即使抖动也可能难以抑制杂散。

- 对于这些分数分频值,需要针对给定通道自动禁用抖动。

- 由于1/2或1/4的分数分频值导致的分数杂散高于PLL带宽,

- 可以通过PLL的环路滤波器来抑制这些杂散。

在ΔΣ ADC中,高阶SLDSM提供随机性优于同阶MASH调制器

当为ΔΣ N小数N PLL考虑数字调制器时,高阶MASH调制器不具有第一级调制器由于不完美增益而产生的拖尾效应。

另一方面,如果数字系数是通过移位、加法和减法实现的,SLDSM会产生内部截断误差。

与ΔΣ ADC的情况相反,数字MASH调制器产生的不相关输出比SLDSM更好,空闲音更少。

因此,MASH调制器是大多数商业应用的热门选择,除非PLL非线性成为带内相位噪声的主要因素。

耦合产生小数杂散

由于耦合而产生的小数杂散是一种非常复杂的行为,很难从Δ N小数N分频PLL的电路设计中预测。

如图所示,有三种机制导致小数杂散产生。

第一种机制是VCO频率与参考频率的谐波之间的直接耦合。

- 当VCO频率是参考频率的非整数倍时,

- 它会引起与参考的谐波频率的交叉耦合,从而导致整数边界杂散。

- VCO频率越接近基准电压源的谐波频率,整数边界杂散越高

第二种机制是电荷泵和VCO之间的耦合。

- 电荷泵以参考时钟周期工作,

- 通过电源和衬底噪声的任何耦合路径都会导致电荷泵频率谐波的整数边界杂散。

第三个是由参考频率和分频器输出频率之间的互调引起的拍音。

- 由于小数分频比Nfrac是通过N/(N+ 1)双模分频器的周期性操作实现的,

- 参考时钟路径和反馈时钟路径之间的噪声耦合可以产生差拍音,从而调制VCO,如图所示

PLL锁定时,PFD输入fd处的互调频率由参考频率fref和分频器输出频率fdiv的倍数组成。

PFD输入端的频率差Δf:

- 函数round()用于获得最接近的整数值,

- N是分频比Nfrac的整数部分

- α是分频比Nfrac的小数部分

的有效频率差是一组离散频率分量,成为VCO的调制频率

6. 分数锁相环的实际设计

| 电荷泵 |

|

| 耦合影响 | 即使使用线性电荷泵,也会出现小数杂散, 这是由于参考频率的谐波与VCO输出处的分数频率之间或 参考频率与分频器的输出频率之间的互调耦合所致。 由于互调机制而产生的这种耦合有点类似于数字PLL中的分数杂散生成 |

| 噪声特点 | 由于带宽较宽,可以观察到高频相位噪声平坦。 由于参考时钟的数字调制,可以观察到参考杂散附近的噪声整形。 |

| PLL高阶极点 | 高阶极点不仅对基准杂散很重要,而且对带外相位噪声也很重要 由于频率到相位转换的积分因子,由n阶ΔΣ调制器贡献的相位噪声呈现(n− 1)阶噪声整形。 为了使量化噪声在高频下逐渐降低,一个(n+ 1)阶ΔΣ分数N分频PLL应设计为具有n阶ΔΣ调制器 |

| ΔΣ调制器的阶数 | 根据经验,ΔΣ调制器的阶数需要大于或等于3。 即使二阶Δ调制器能够满足相位噪声要求,并且在仿真中不产生空闲音,但在硬件中可能会观察到时变杂散或相位噪声波动。 |

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?