前言

非常遗憾的一件事情是,在选修课程时我避开了FPGA,选择了其他方向的课程。然而,令我没有想到的是,通信项目设计的题目竟然使用FPGA,这简直是背刺。在仅有的半个月时间里,准备这个项目确实是非常紧张的。为了下载FPGA相关的软件,我不得不将我的深度学习项目全部转移到硬盘上,还删除了虚拟机和其他一些软件,才终于腾出足够的空间来安装所需的软件。

Vivado安装教程

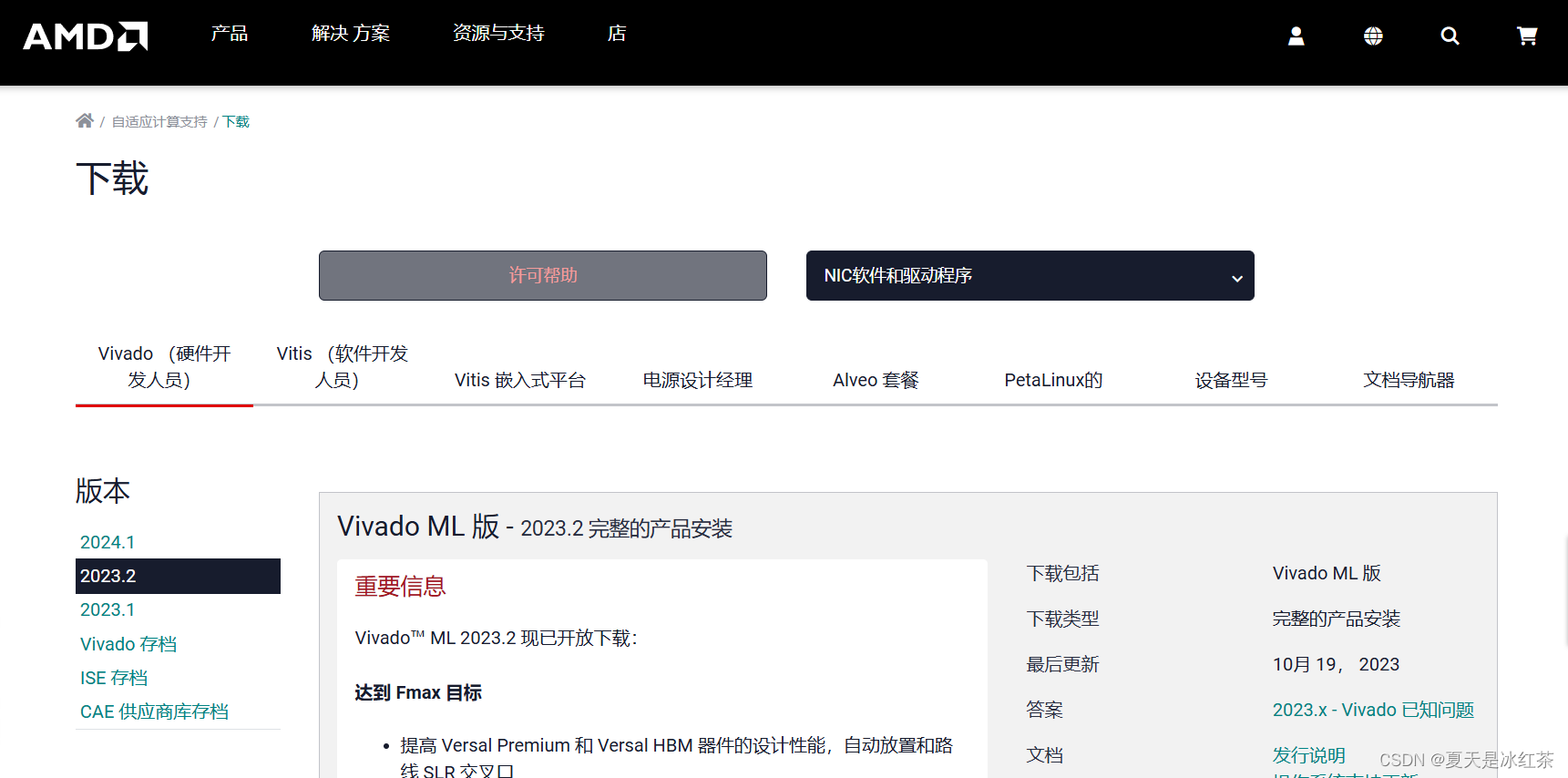

通过官网下载安装包

- www.xilinx.com (英文)

- www.china.xilinx.com (官方中文网站)

安装直达链接:

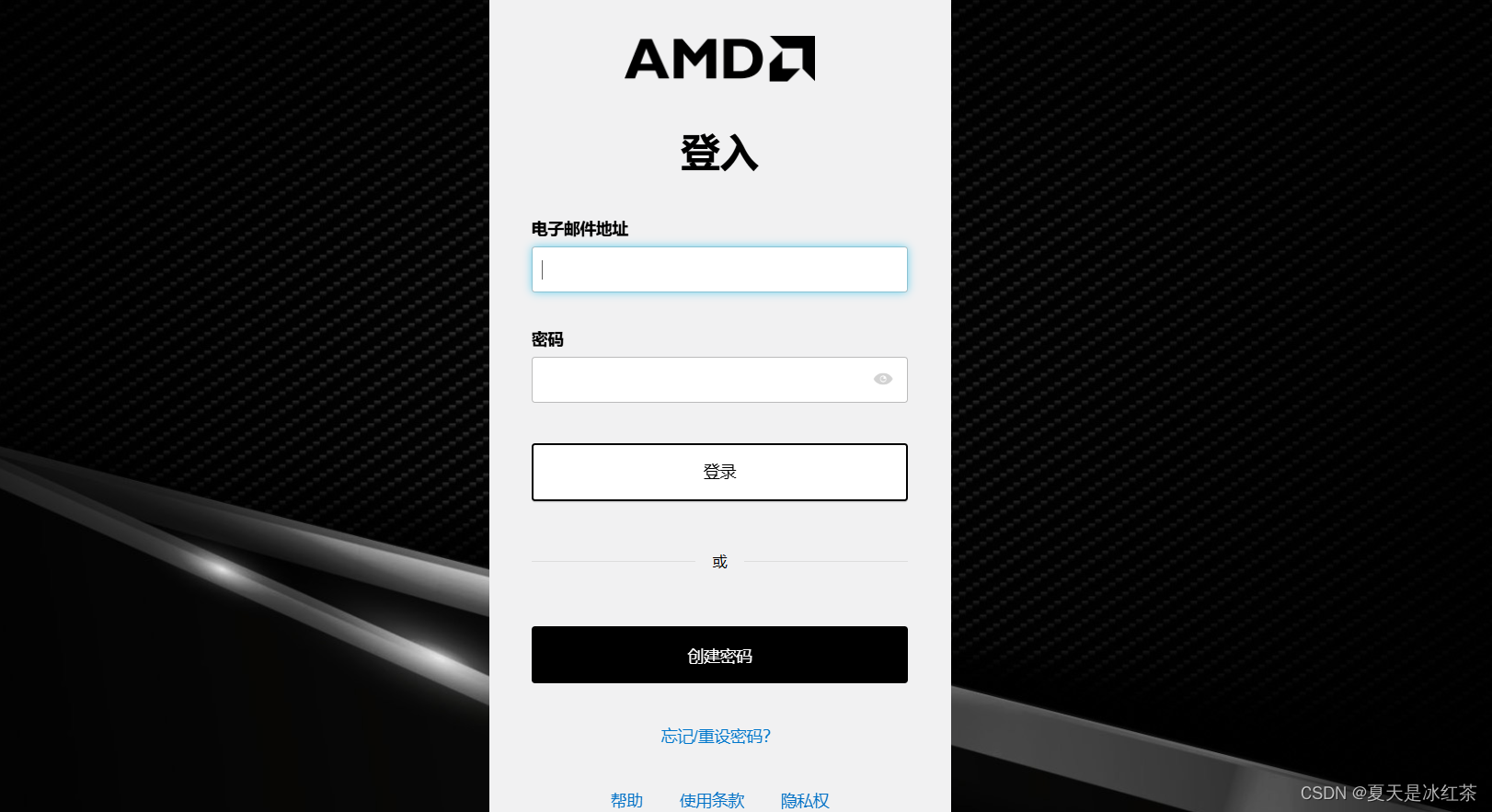

当然选择你当前合适的版本就可,这里我选择的是安装2022的版本,一般比最新版低一到两个就可以了。点击之后会进入一个登录页面,没有注册的就进行注册后再登录。

接着还要填写一些基础信息(挺麻烦的)。

完了等待下载即可

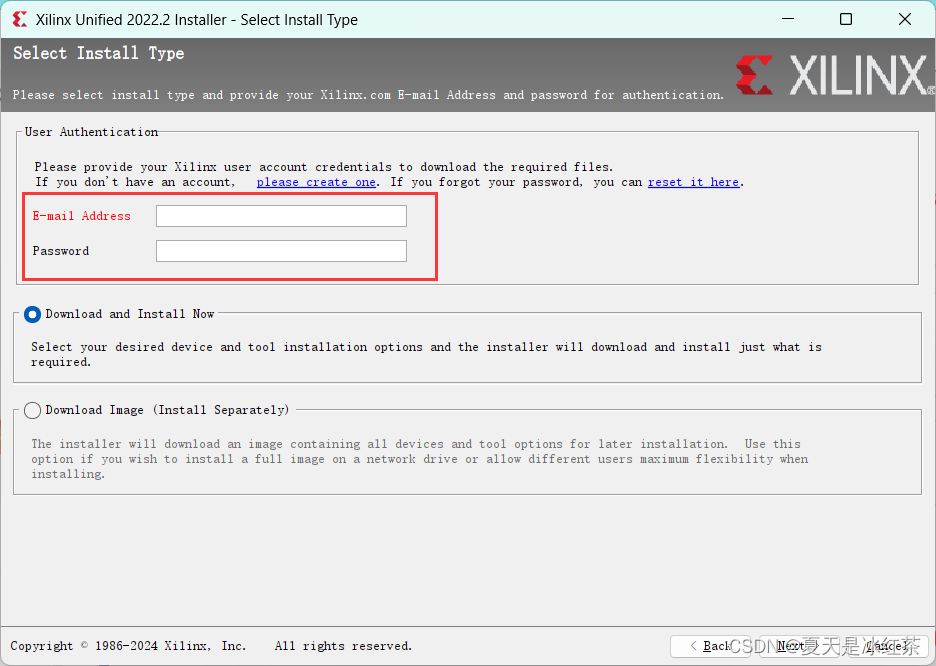

点击Next

再次输入账户信息后点击Next

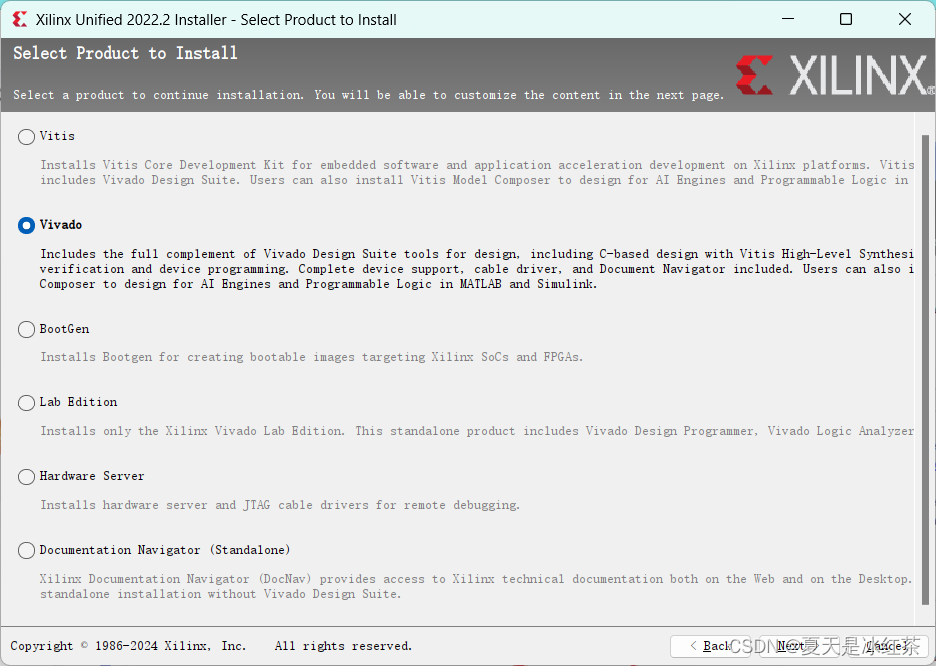

选择Vivado后点击Next

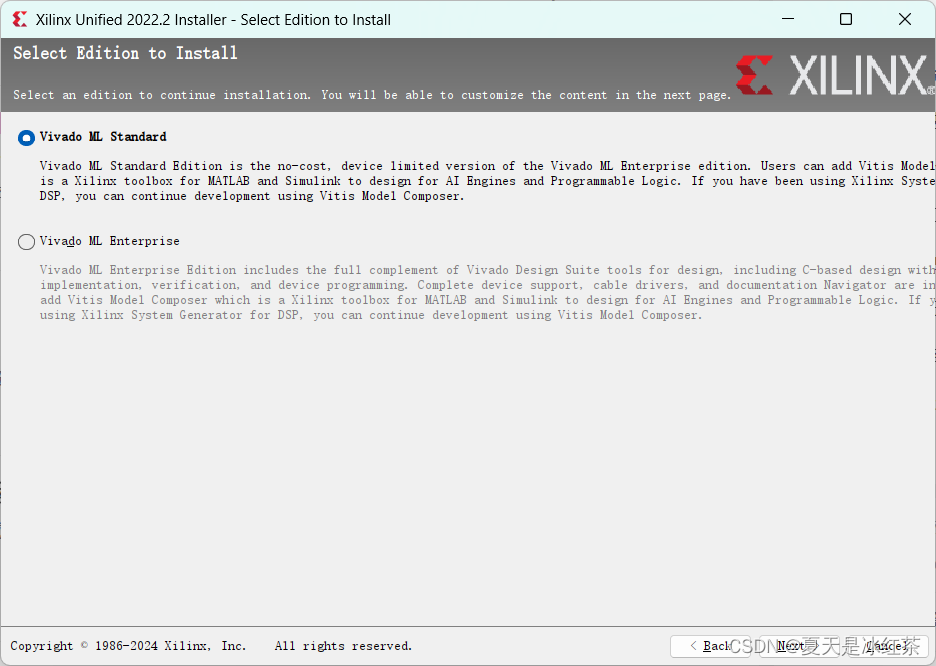

选择Vivado ML Standard标准版,点击Next

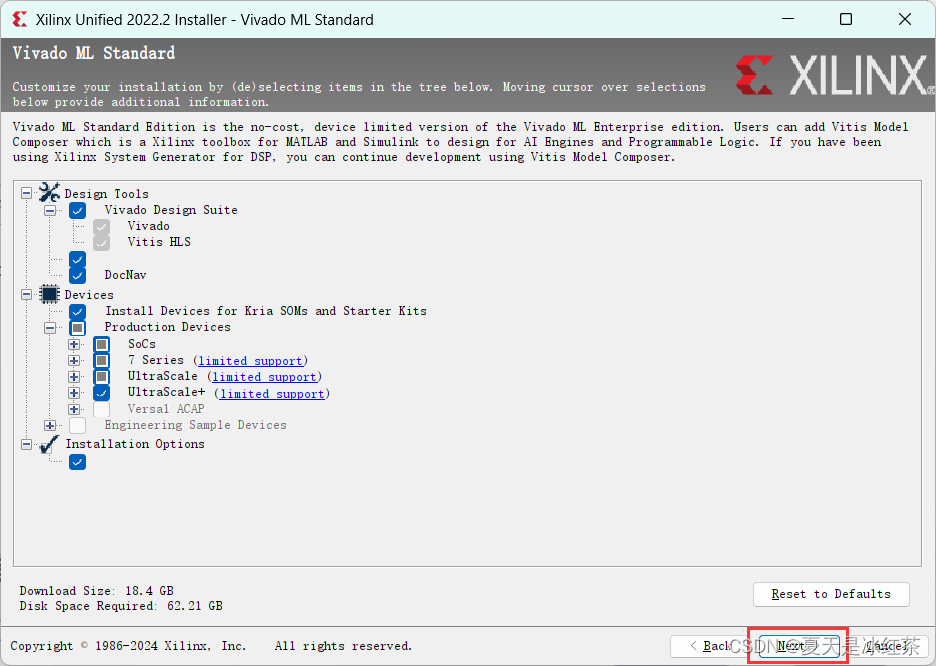

开头也说了,我的磁盘空间不够,而且我的项目只要有simulink仿真即可,有足够空间的可以去安装Vivado ML Entexprise企业版。

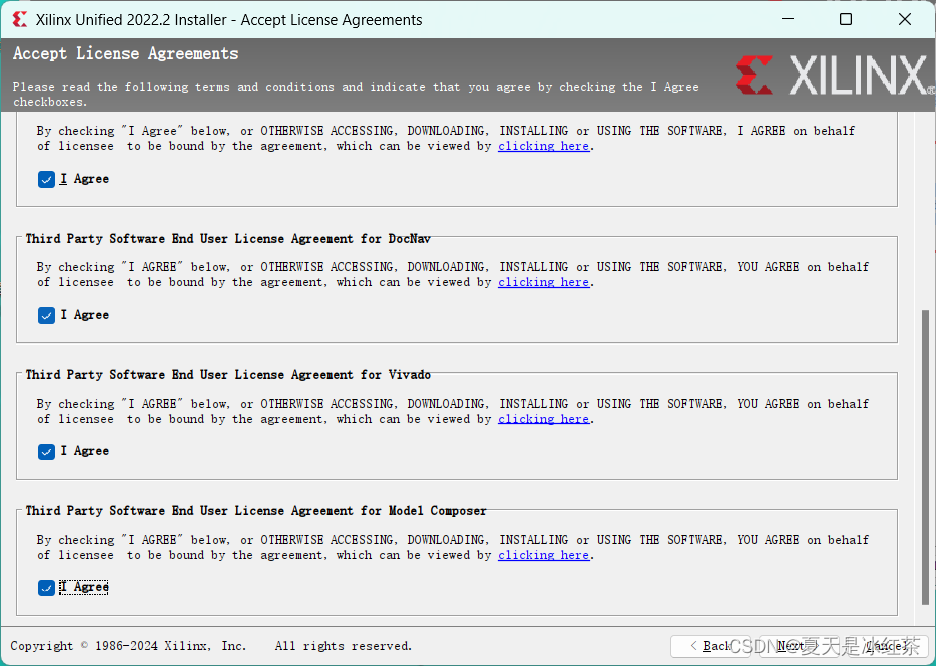

在全部同意后进入下一页

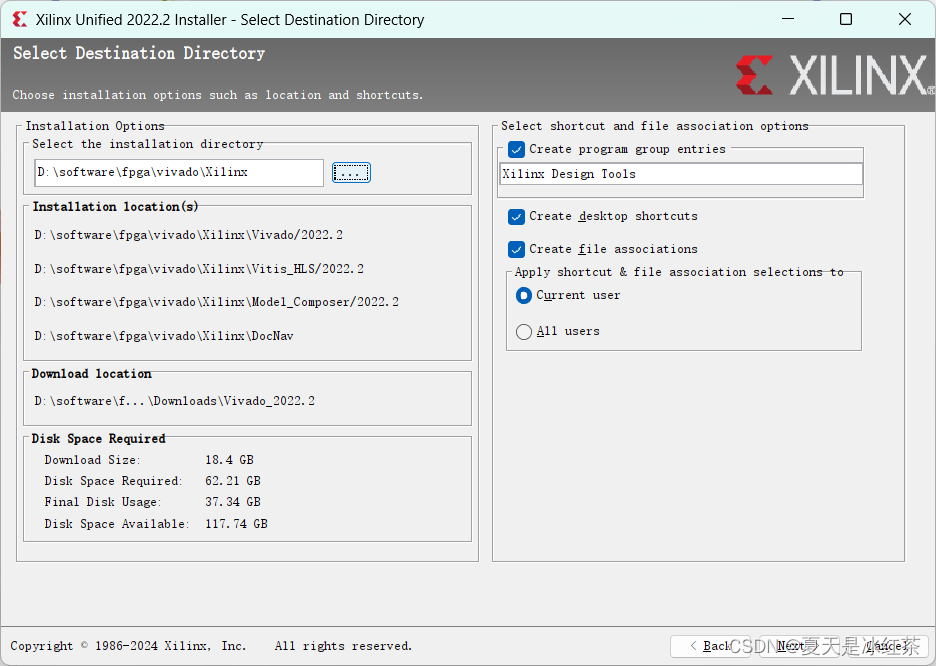

它这里默认安装是C盘的,切换到其他盘即可

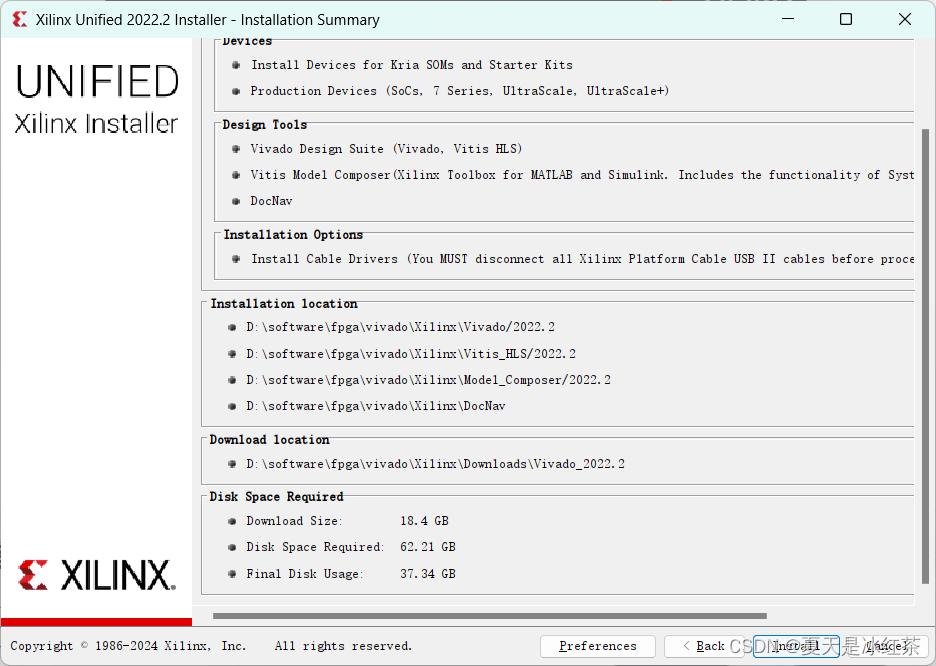

开始安装,接下来等待蛮久......

最后下载成功

创建工程

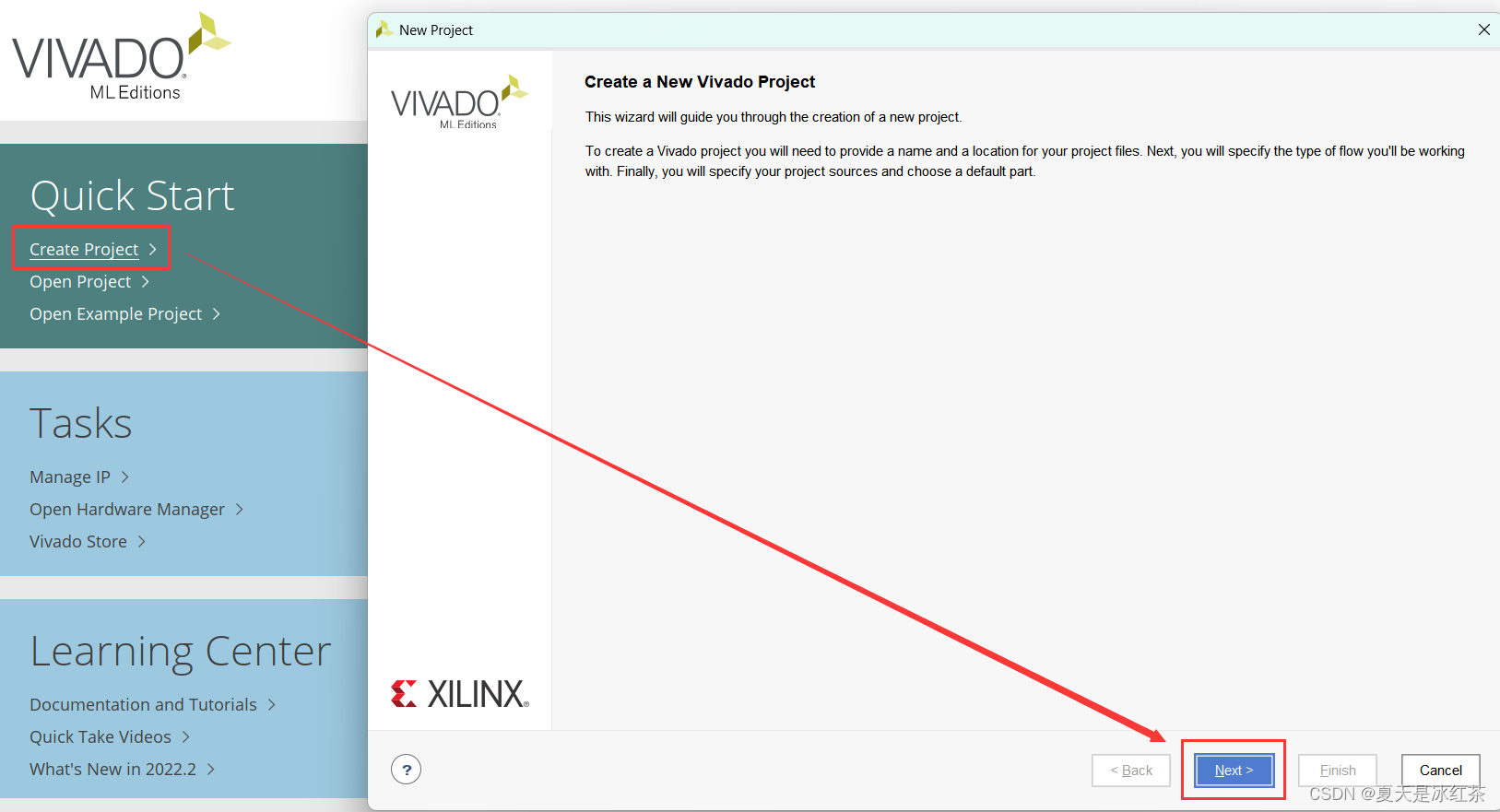

点击三棱的图标,选择创建工程

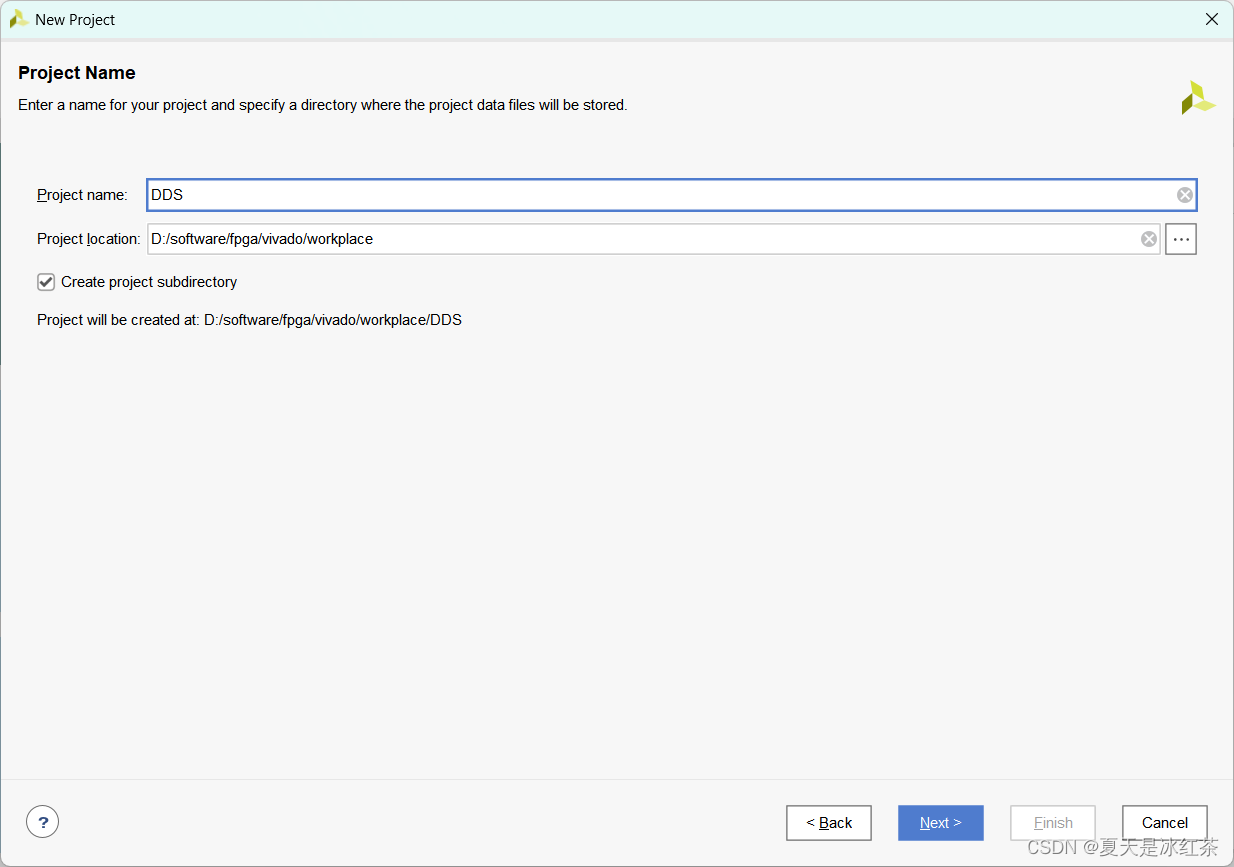

好的习惯就是有独特的项目名称,以及统一的项目路径,注意项目名称和路径不能有中文。

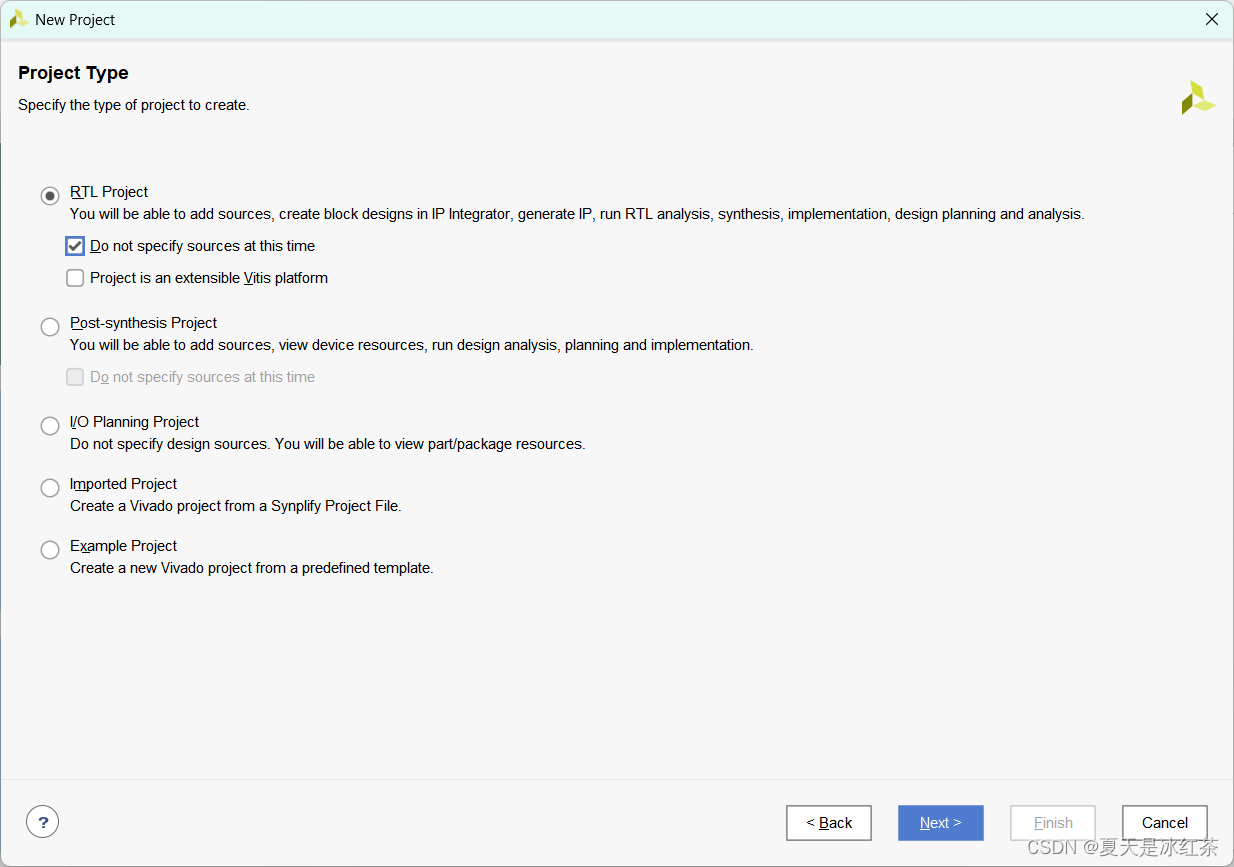

接下来是选择项目类型

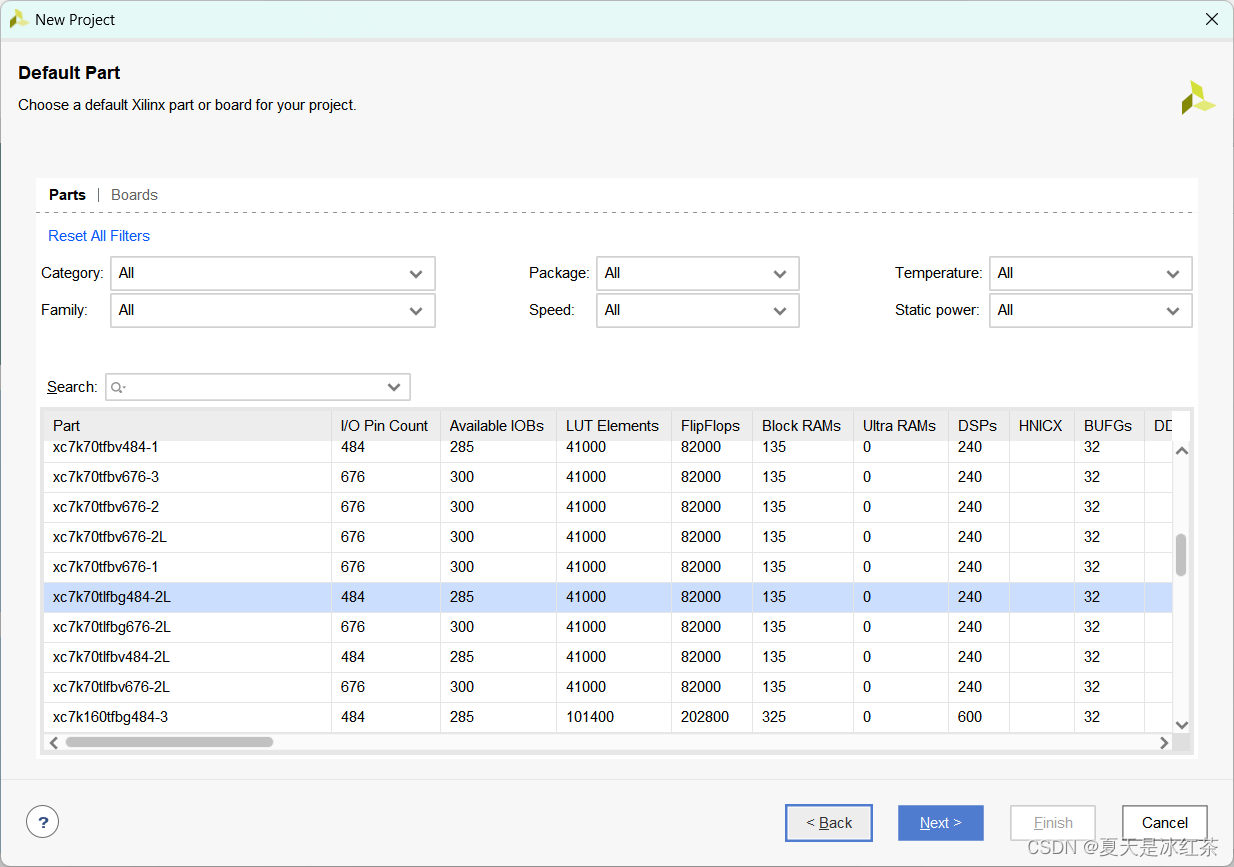

这里是芯片类型,可以先选一个进去

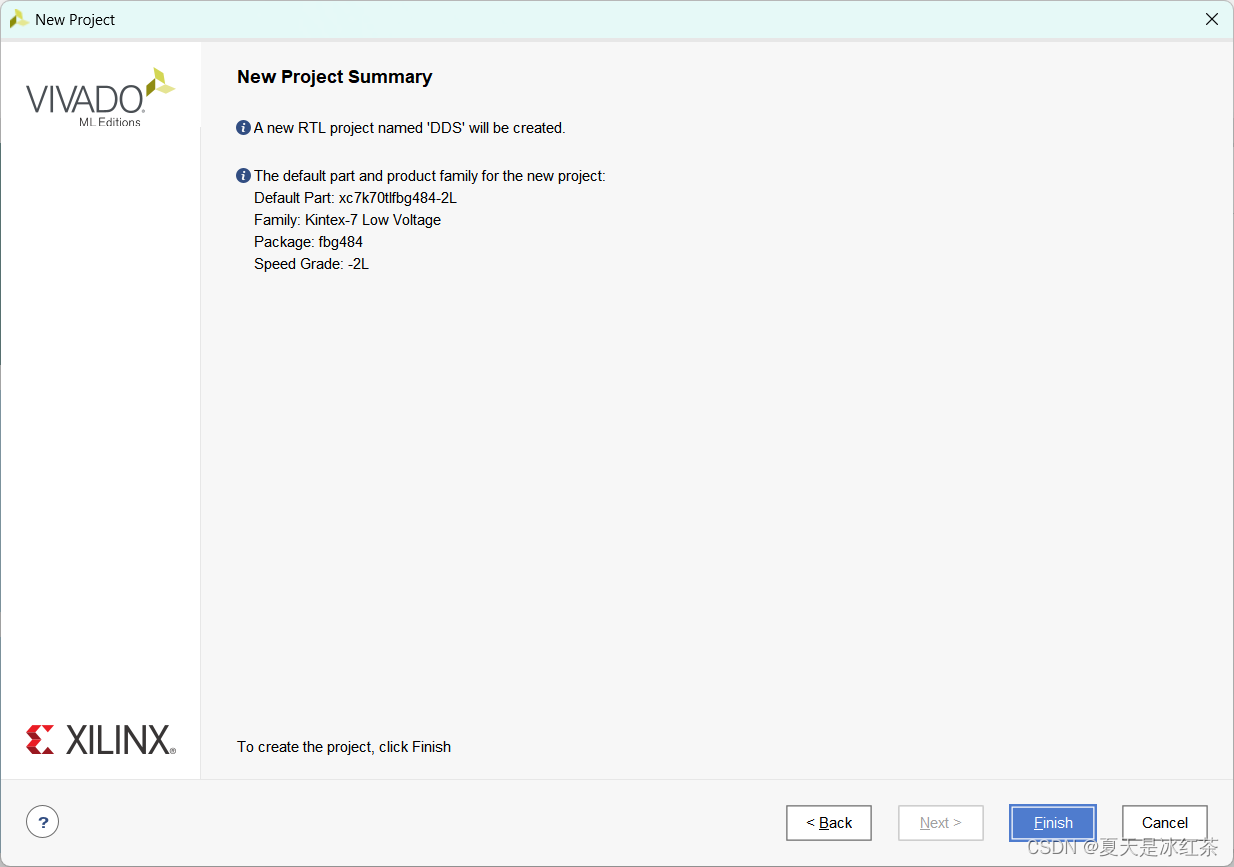

点击完成,进入界面。

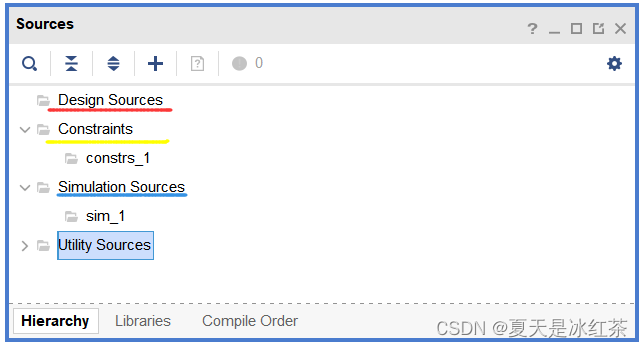

进入界面,在这个地方,红色是我们写程序的地方,黄色是约束文件,是连接主文件的输入输出和板子上的管脚连接的重要部分,蓝色横线部分是仿真文件,用于验证程序是否写的正确。

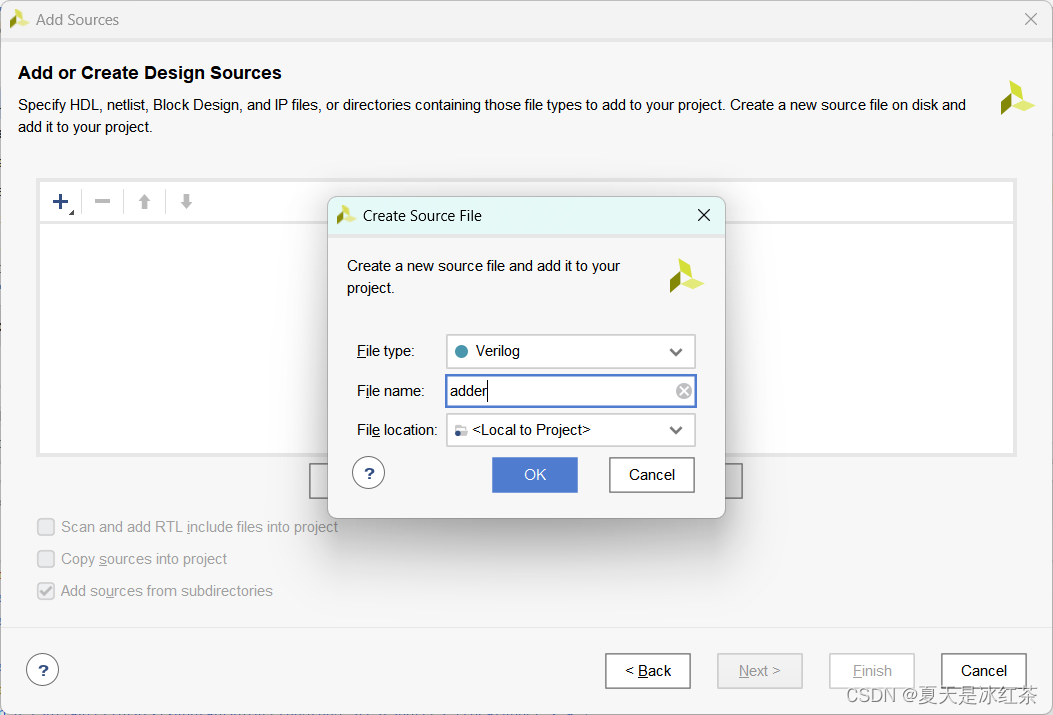

这里右键点击红色横线部分点击添加文件,注意它这里添加的文件类型一点要看清,就是是否是这个文件夹的类型,说起来有点绕,自己看看就明白了。

然后点击finish,会有一个弹窗让你选择文件的管脚,因为我们有约束文件,所以直接关掉就好了。

`timescale 1ns / 1ps

// adder.v

module adder(

input wire [7:0] a,

input wire [7:0] b,

output reg [8:0] sum

);

always @(*) begin

sum = a + b;

end

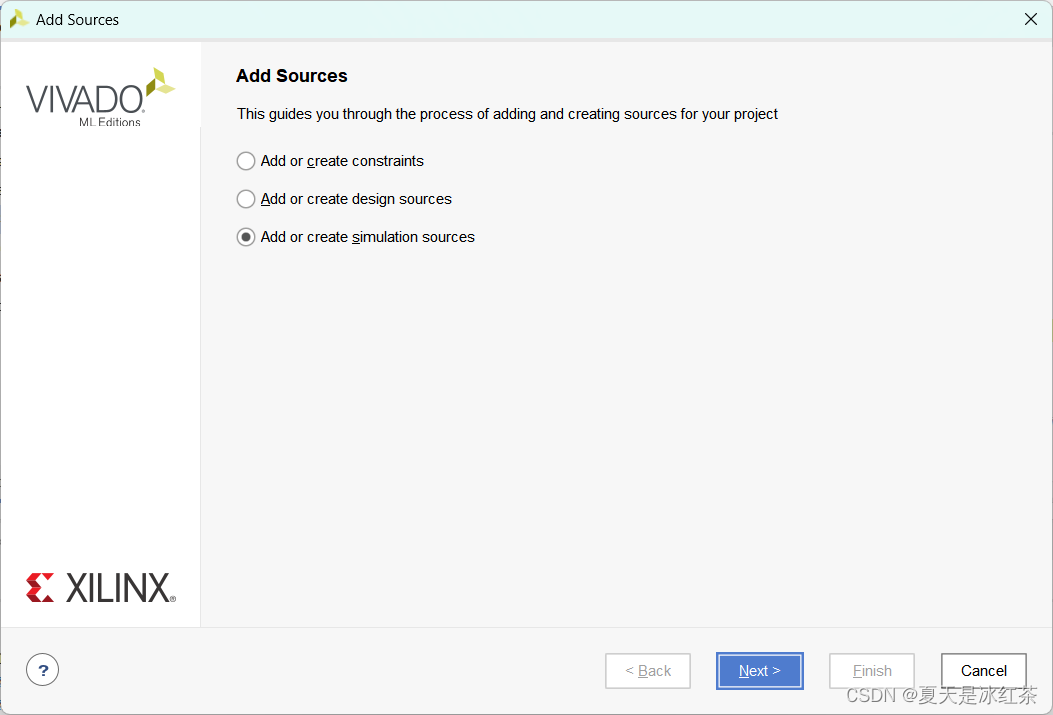

endmodule在Simulation Sources下新建一个adder_tb文件

// adder_tb.v

`timescale 1ns / 1ps

module adder_tb;

reg [7:0] a;

reg [7:0] b;

wire [8:0] sum;

adder uut (

.a(a),

.b(b),

.sum(sum)

);

initial begin

// 初始化输入

a = 8'h05;

b = 8'h0A;

#10;

a = 8'hFF;

b = 8'h01;

#10;

$finish;

end

initial begin

$monitor("At time %t, a=%h, b=%h, sum=%h", $time, a, b, sum);

end

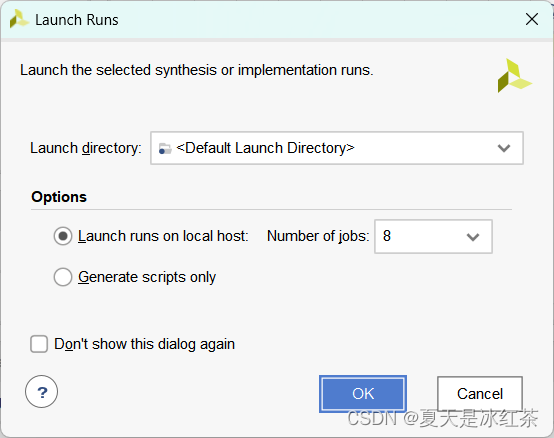

endmodule点击左侧栏中的SYNTHESIS,此时正在进行编译操作,然后在控制台没有报错就行了。

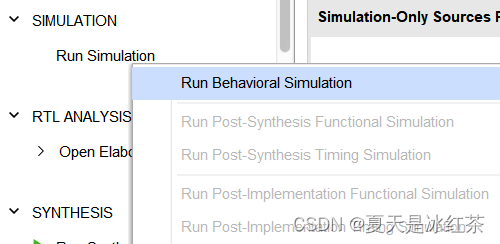

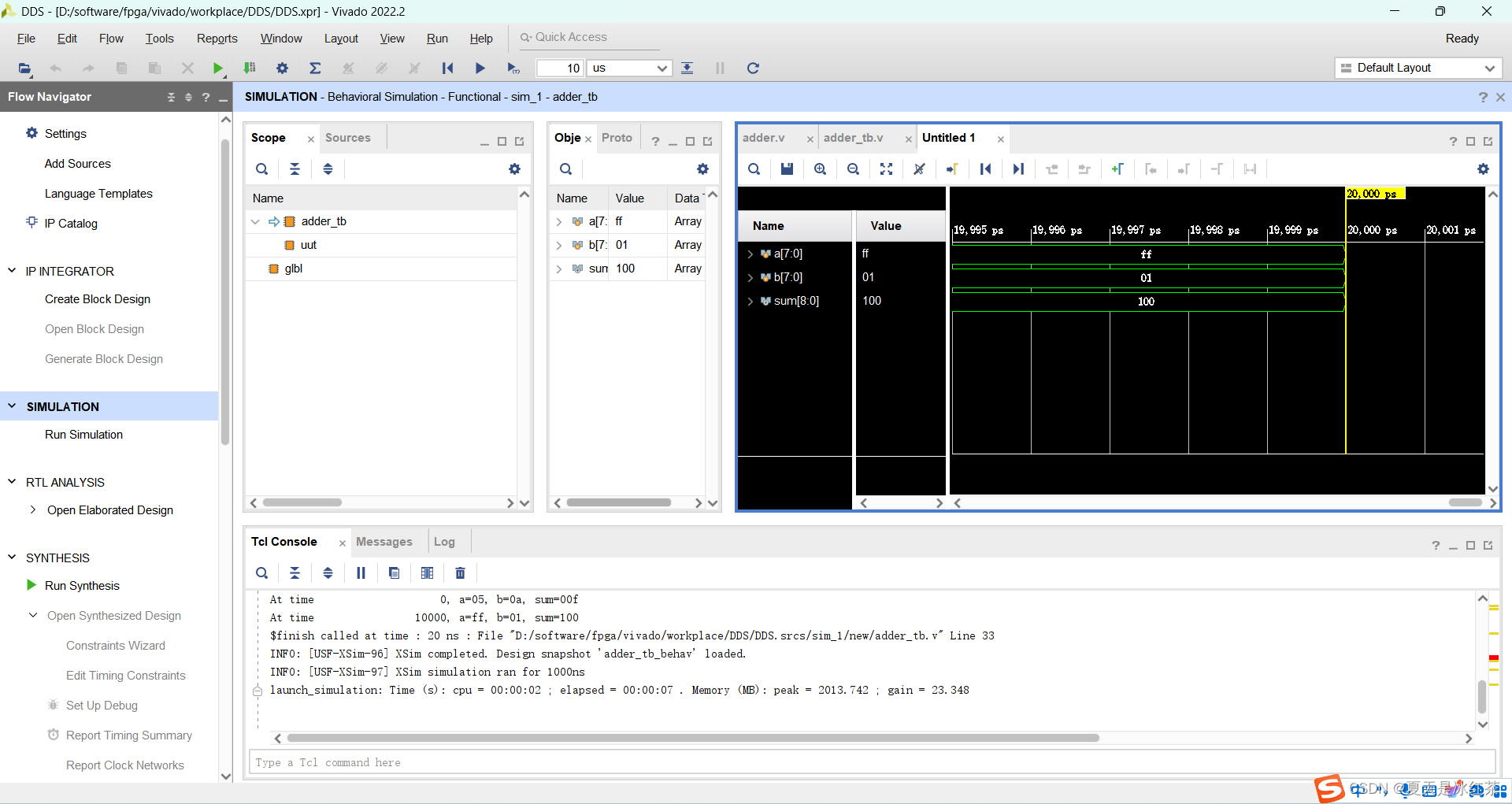

接着,点击SIMULATION进行仿真

参考文章

vivado工程创建(从新建到下板)_vivado怎么新建工程-CSDN博客

【FPGA】Vivado 保姆级安装教程 | 从官网下载安装包开始到安装完毕 | 每步都有详细截图说明 | 支持无脑跟装_vivado安装教程-CSDN博客

【FPGA】Vivado软件使用教程_vivado使用教程-CSDN博客

7595

7595

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?