模块代码:

module BCD_Count(Clk,Rst_n,Cin,Cout,q);

input Clk;

input Rst_n;

input Cin;

output reg Cout;

output [3:0] q;

reg [3:0] cnt;

always@( posedge Clk or negedge Rst_n )

begin

if( Rst_n==0 )

cnt<=0;

else if( Cin==1 )

begin

if( cnt==9 )

begin

cnt<=0;

Cout<=1;

end

else

cnt<=cnt+1;

end

else if( Cin==0 )

Cout<=0;

end

assign q=cnt;

endmodule

`timescale 1ns/1ns

`define Time_Periord 20

module BCD_Count_tb;

reg clk;

reg rst;

reg cin;

wire cout;

wire [3:0] q;

BCD_Count BCD_Count0

(

.Clk(clk),

.Rst_n(rst),

.Cin(cin),

.Cout(cout),

.q(q)

);

initial

clk=1;

always

#(`Time_Periord/2) clk=~clk;

initial

begin

rst=0;

#100;

rst=1;

repeat( 30 )

begin

cin=0;

#(`Time_Periord*10);

cin=1;

#(`Time_Periord*1);

end

$stop;

end

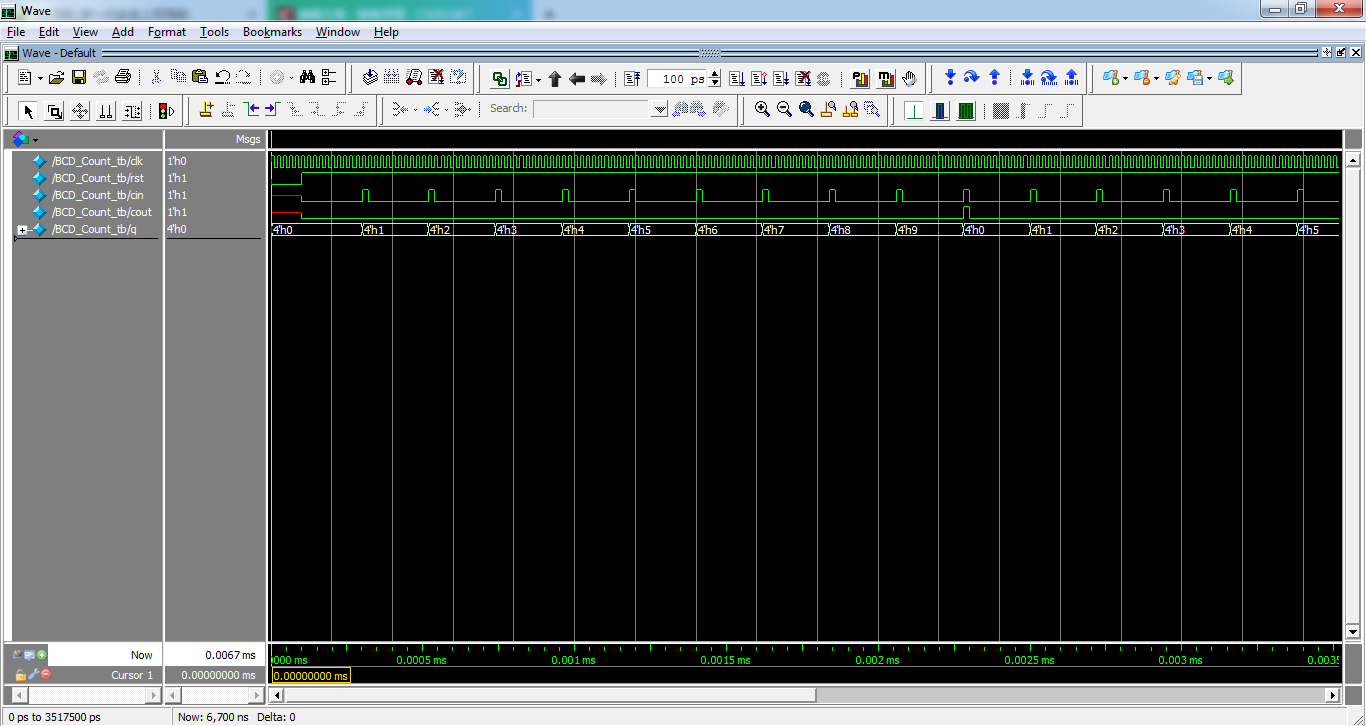

endmodule RTL仿真结果:

1431

1431

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?