axi传输线分为:

(1)axi-full

(2)axi-lite

(3)axi-stream

arm官方文档:AMBA AXI and ACE Protocol Specification Version E (arm.com)

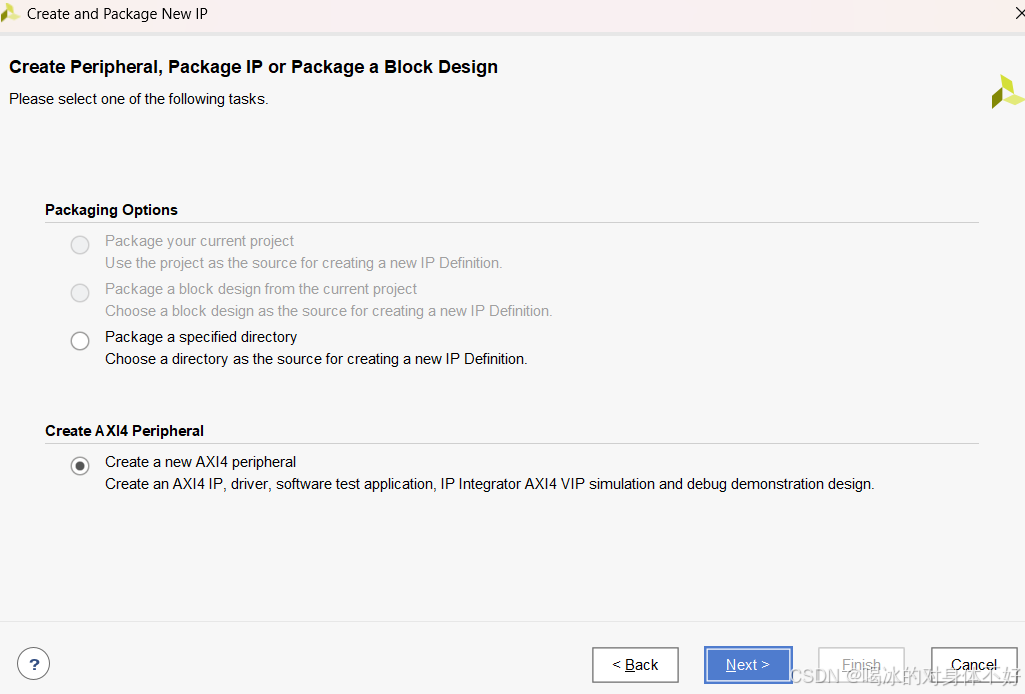

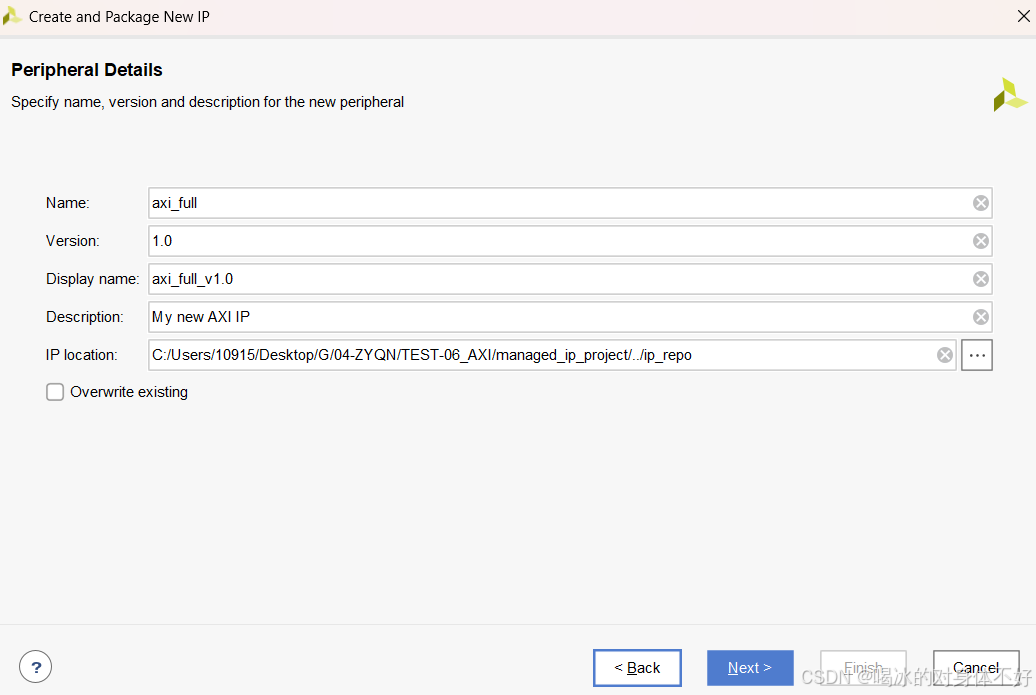

create一个IP

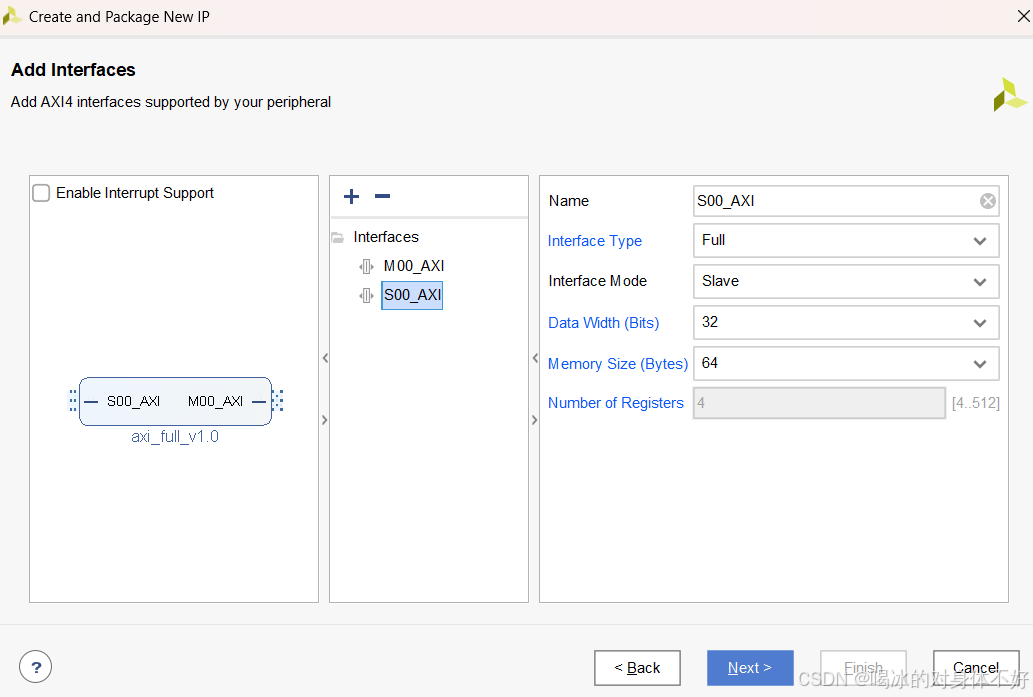

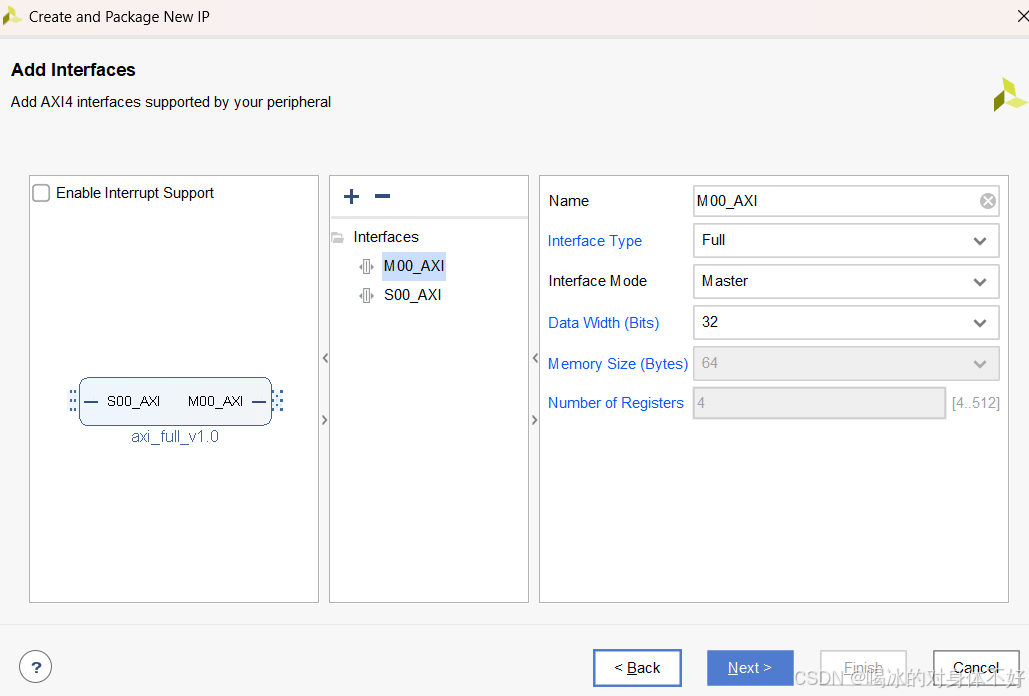

选择AXI接口

设置一个主接口和一个从接口

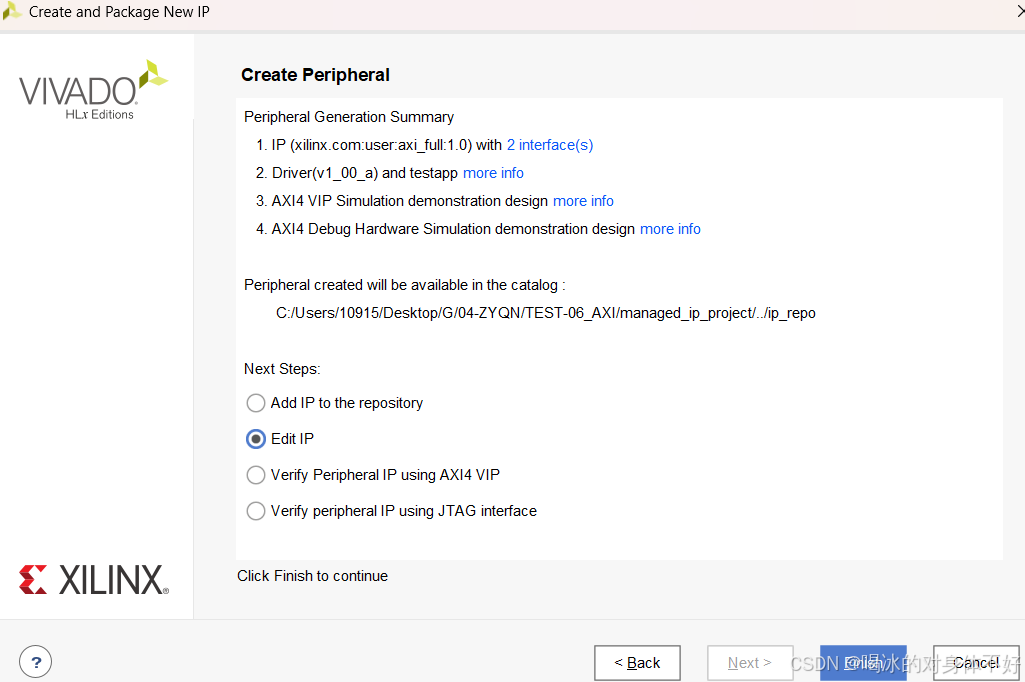

下一步选择编辑IP

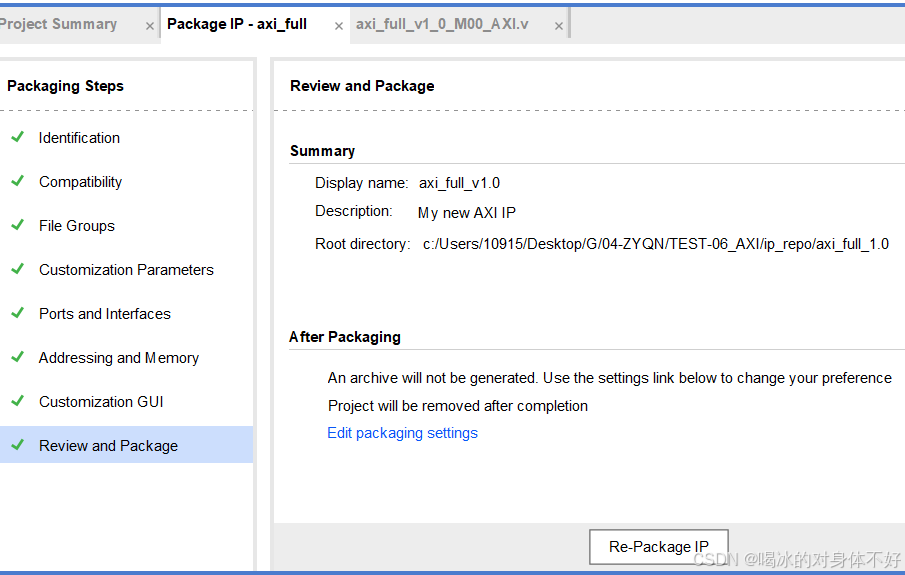

自己编写接口前打包一下IP

仿真一下IP

仿真一下IP

重开一个新的工程,create block design

将前述ip添加进来

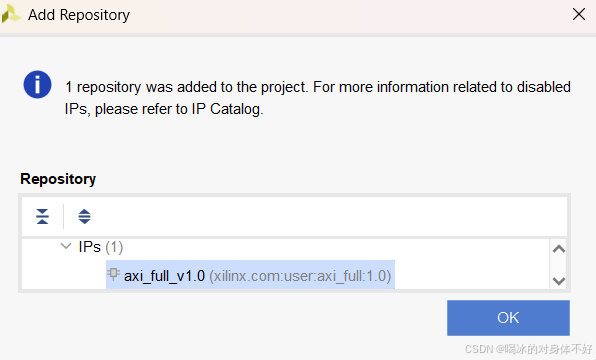

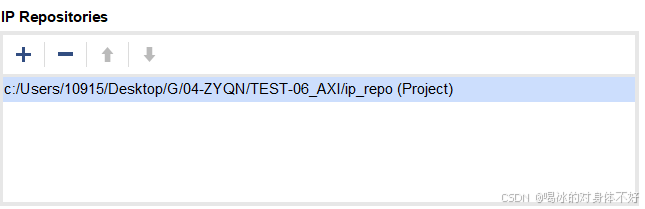

settings-IP-Repository-+-选择ip_repo文件夹

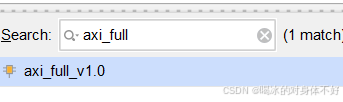

注意这里是灰色可能是因为打包好的IP器件型号和所添加到工程的器件不匹配,设置为同一器件型号,就有颜色了

添加ip

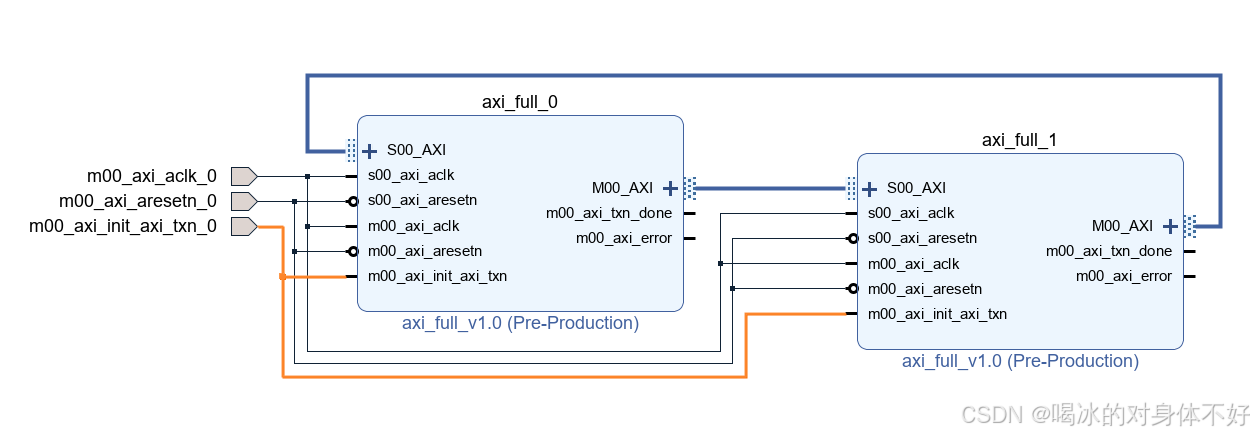

连线,设置时钟复位和触发引脚:

验证

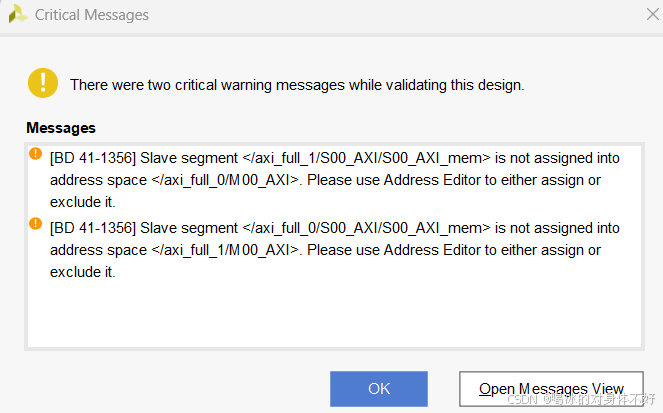

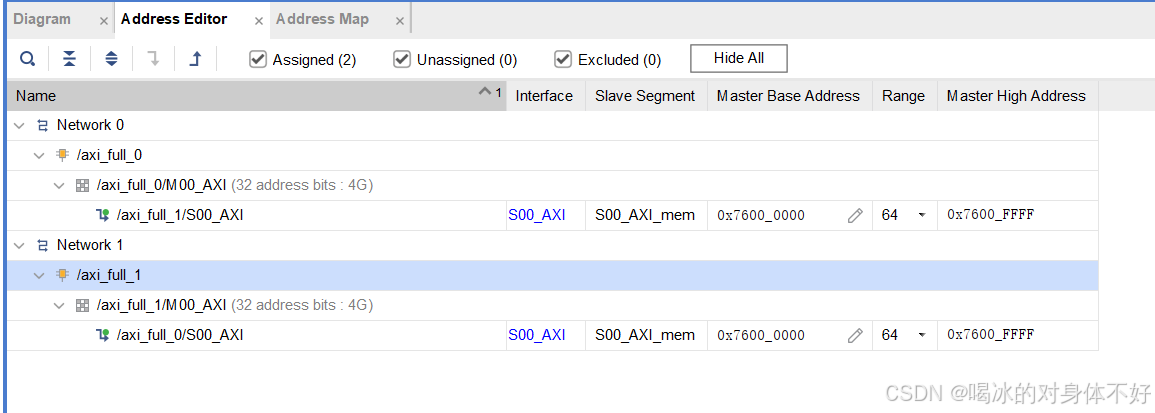

自动分配地址,点向下那个箭头

重新验证:

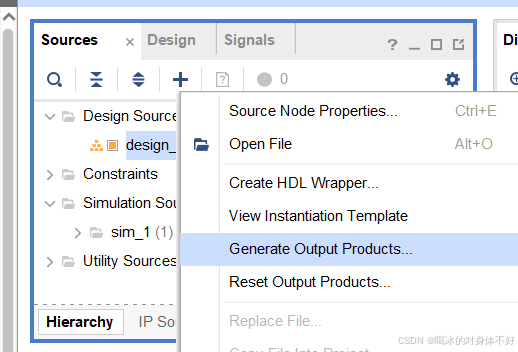

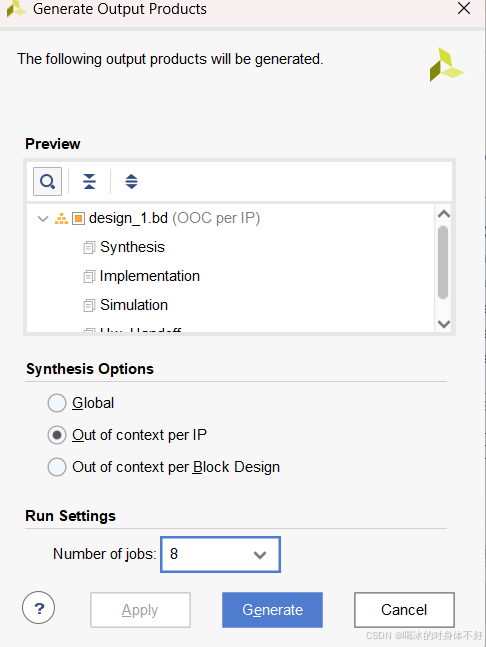

输出模块:

生成成功

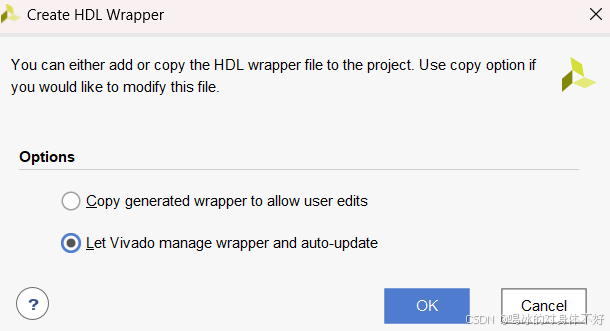

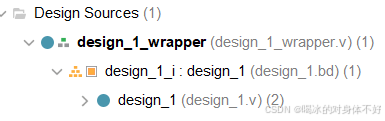

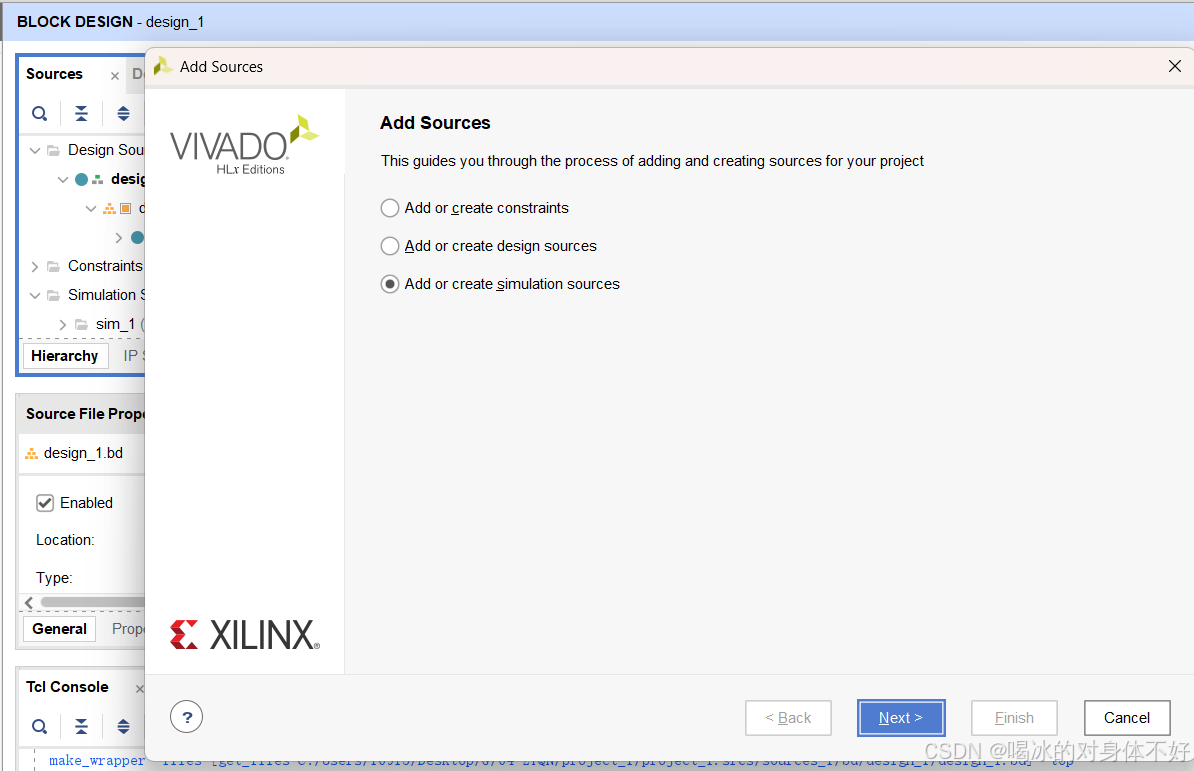

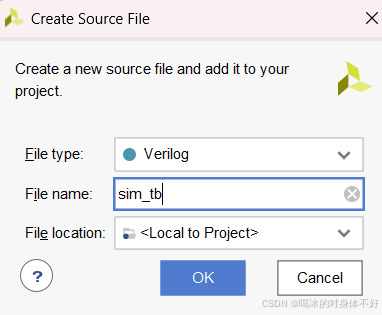

给模块加一个激励文件:

编写激励文件:

`timescale 1ns / 1ns

module sim_tb();

reg clk,rst_n;

reg txn;

design_1_wrapper design_1_wrapper_u0

(

.m00_axi_aclk_0 (clk),

.m00_axi_aresetn_0 (rst_n),

.m00_axi_init_axi_txn_0 (txn)

);

initial begin

rst_n=0;

txn=0;

#100;

rst_n=1;

#1000;

txn<='d1;

end

always begin

clk<='d0;

#10;

clk<='d1;

#10;

end

endmodule跑仿真

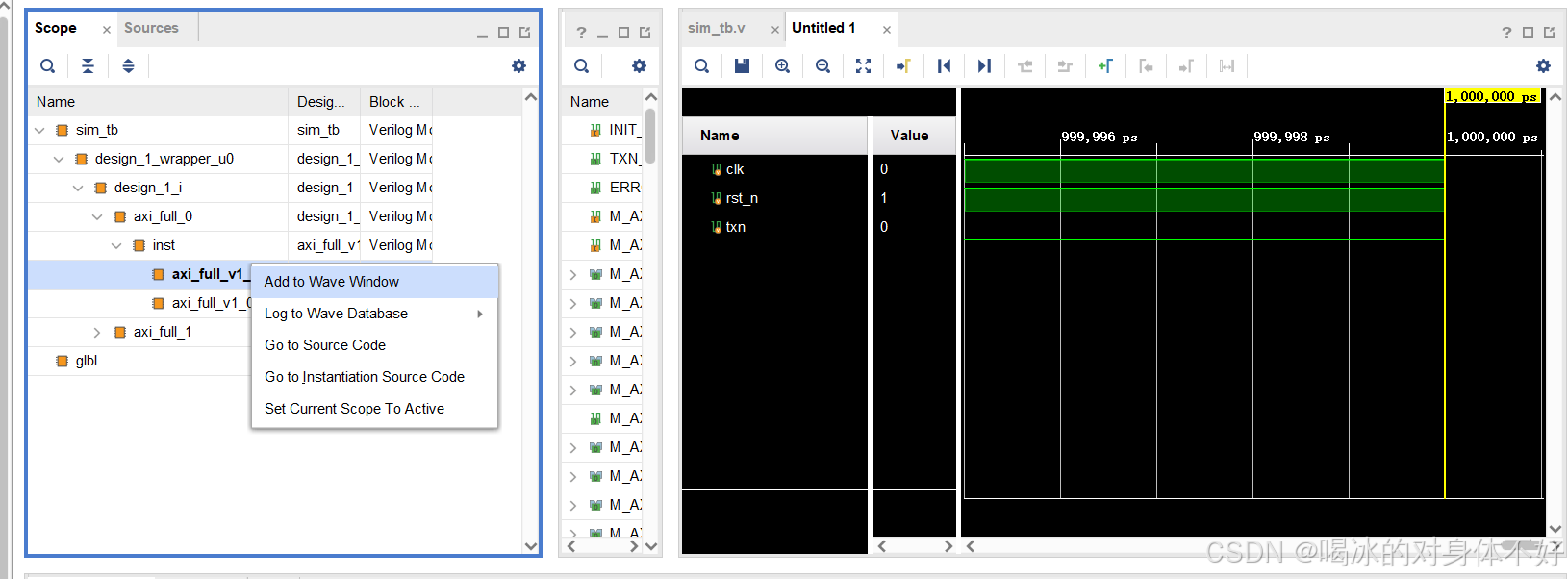

将主接口和从接口的信号添加进仿真

主接口和从接口的所有信号作为一个组并命名,选中所有信号,右键new group

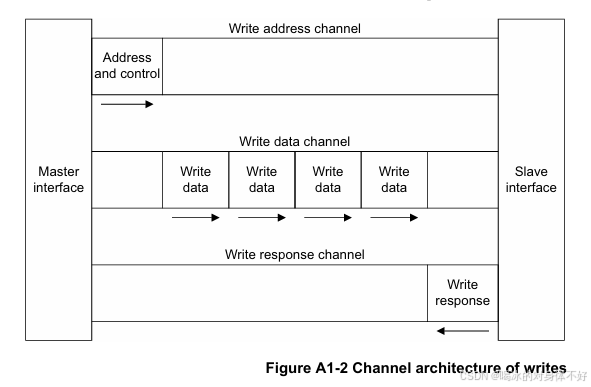

而后分析信号,官方文档写过程如下:

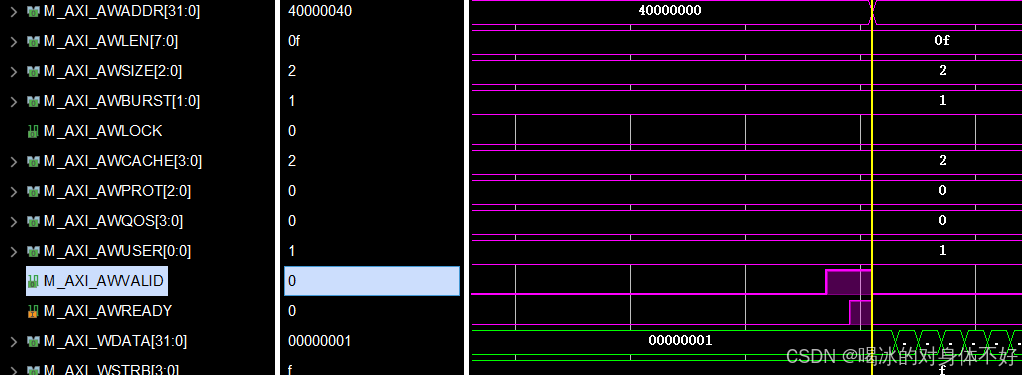

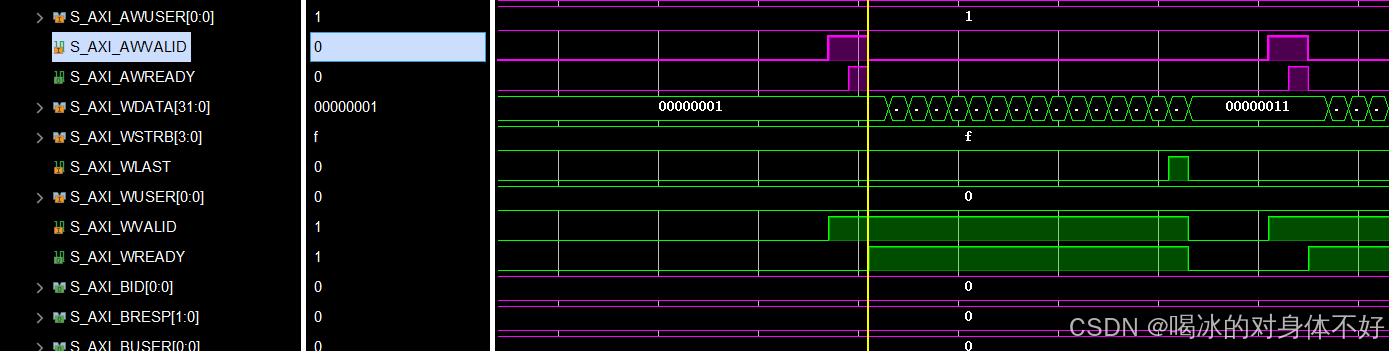

首先主机写地址,当触发信号触发后,AWVALID和AWREADY信号最先变化,同时为高时,地址AWADDR被写入

写完地址,紧接着写数据,WVALID拉高,WREADY拉高数据被写入

写完地址,紧接着写数据,WVALID拉高,WREADY拉高数据被写入

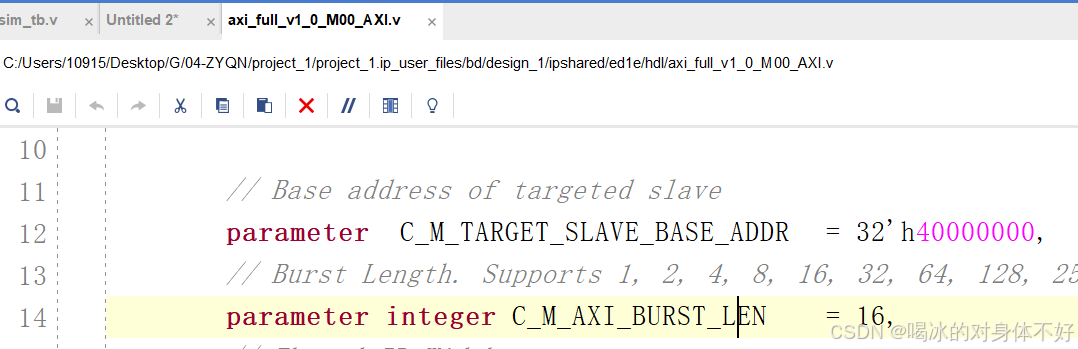

由于输入设置突发长度为16故,一次传16个数据

![]()

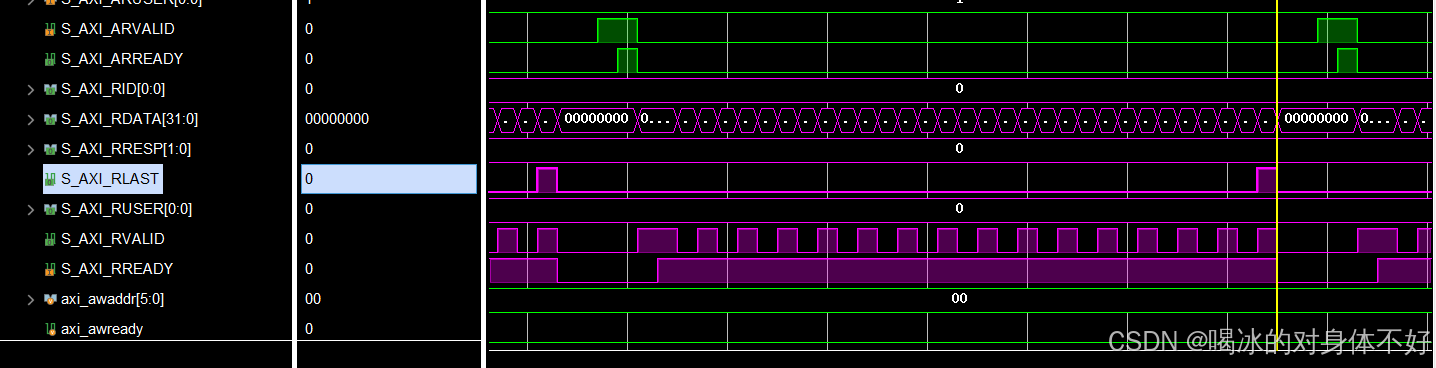

从机口

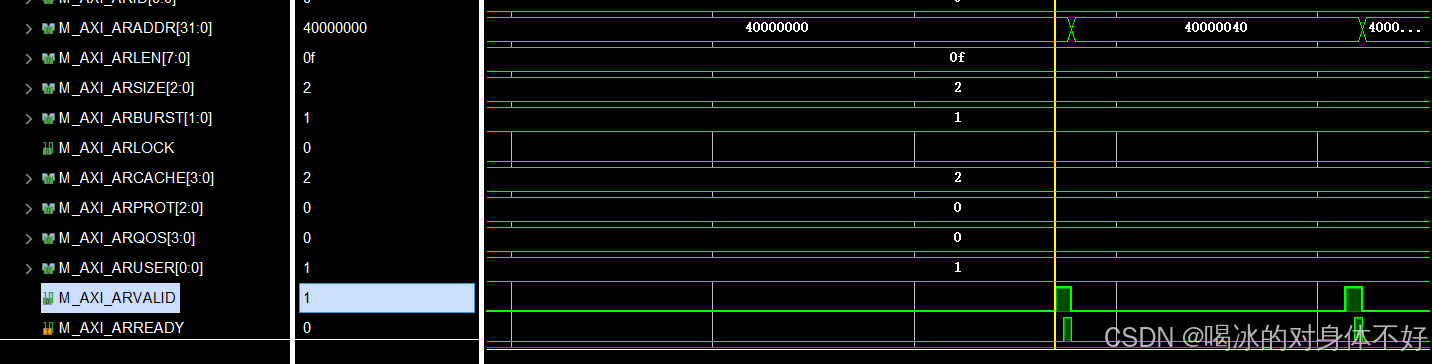

主机读地址数据,ARVALID和ARREADY同时拉高ARADDR被读入

主机读地址数据,ARVALID和ARREADY同时拉高ARADDR被读入

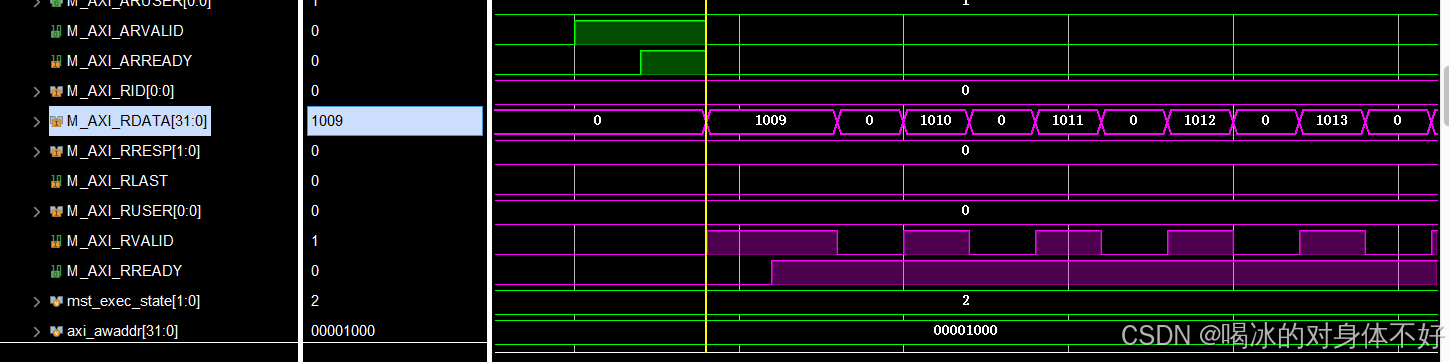

RVALID和RREADY同时为高时读入一次数据

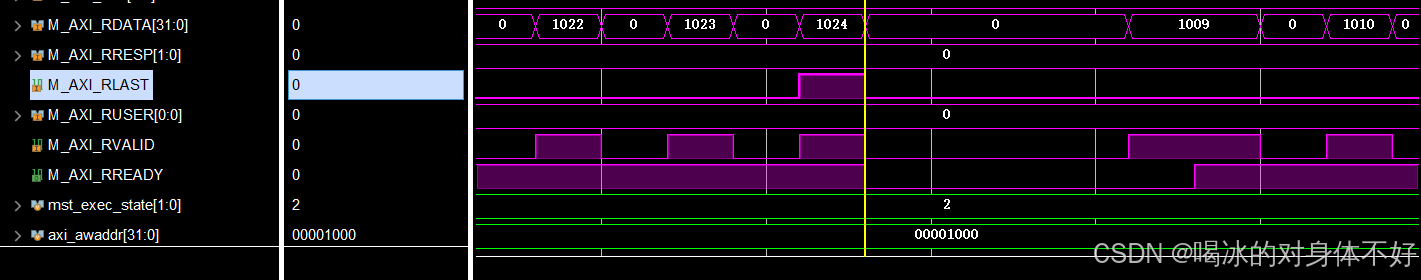

一直到最后一个信号1024,并且有LAST信号

同样从机口读数据

波形解读:

1)VALID和READY同时为高代表当前数据有效

2)先写地址,紧接着写数据,最后一个数据后LAST拉高

3)先读地址,紧接着读数据,最后一个数据后LAST拉高

4)写完数据有一个相应信号

509

509

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?