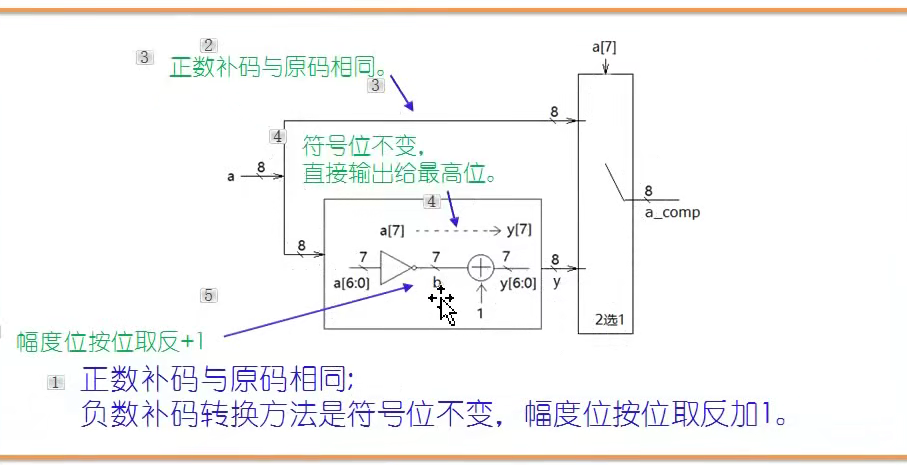

补码转换器示意图

代码:

//2023-5-17

//补码转换

module comp_conv(

a,

out_1

);

input[7:0] a;

output[7:0] out_1;

reg[7:0] out_1;

always@( * ) begin

if (a[7] == 0) begin

out_1 <= a;

end

else begin

out_1 <= {a[7],~a[6:0]+1};

end

end

//assign out_1 = a[7]?{a[7],~a[6:0]+1}:a;

endmodule

//-----testbench of comp_conv----

module comp_conv_tb ;

reg[7:0] a;

wire[7:0] out_1;

comp_conv comp_conv(

.a(a),

.out_1(out_1)

);

initial begin

a = 0;

#4000 $stop;//8位字节位0-255,256*15=3840

end

always #15 a <= a+1 ;

endmodulealways语句或者assign语句都可实现功能,但要注意变量是reg还是wire。不定义的话默认是wire

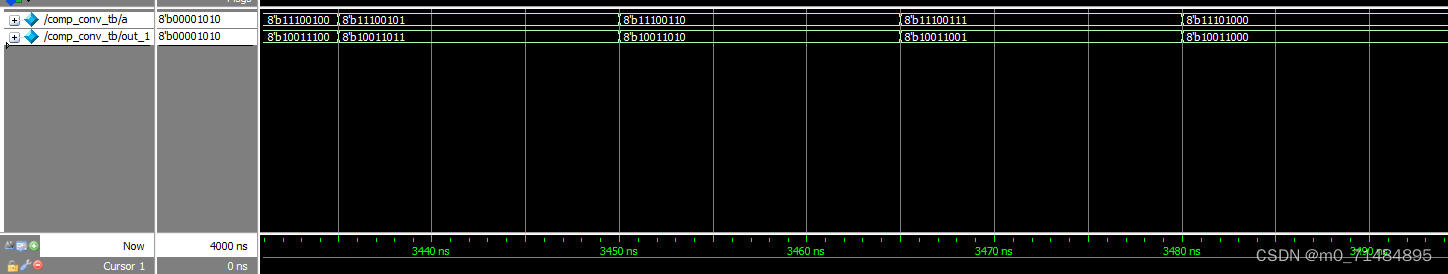

仿真波形

七段译码器示意图:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?