一、

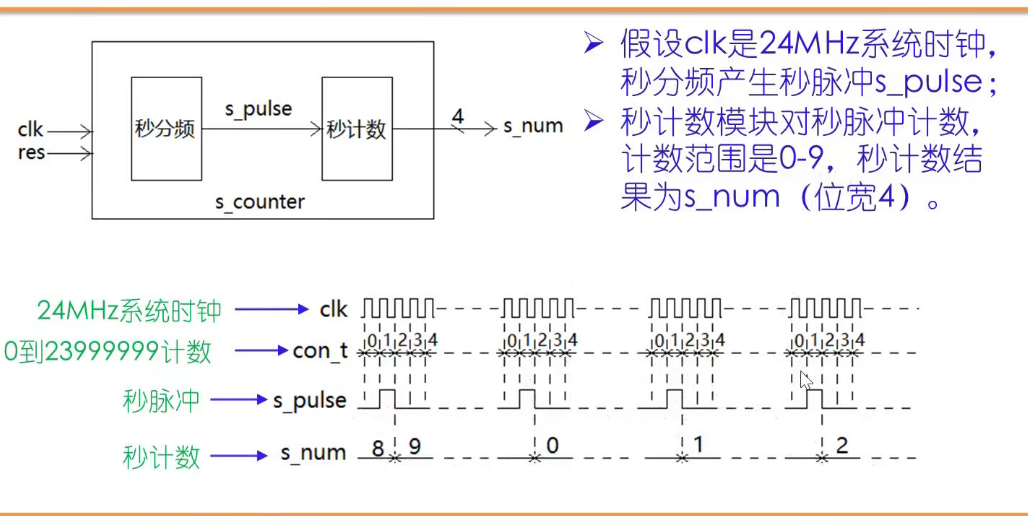

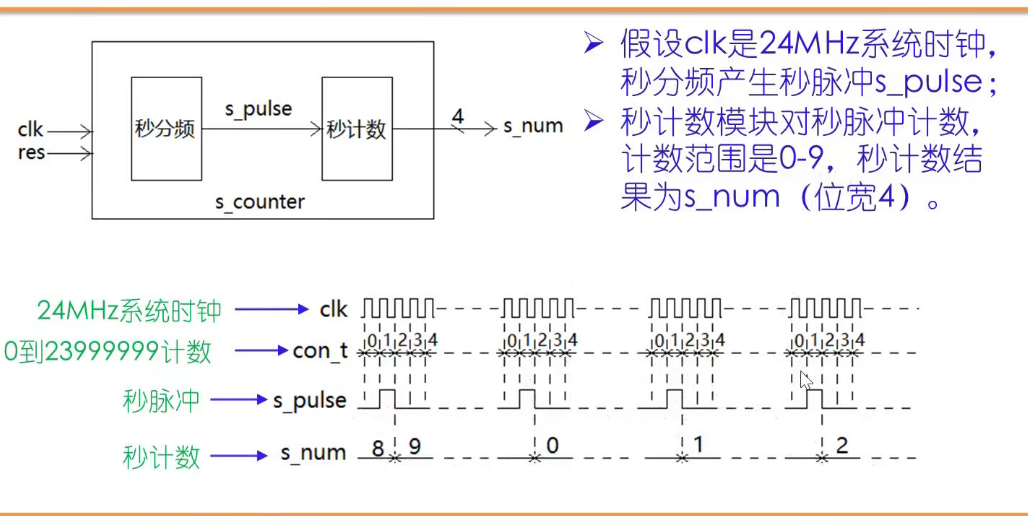

利用系统计算器将系统时钟分频,对秒脉冲进行计数。

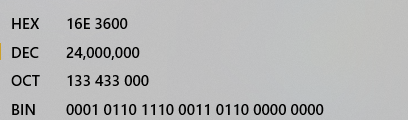

cont 是秒脉冲分频计数器,需要对 24M 来计数,至少需要 25 位。

spulse 是秒脉冲尖,cont 为 0 时为1,1 秒有 24M 个脉冲,但只有 1 个脉冲时 spulse=1。

sum 是秒计数器,看到 spulse 为 1 时计数。

仿真代码

//2023-5-17

//0-9循环的秒计数器

`timescale 1ns/10ps

module scounter(

clk,

res,

sum

);

input clk;

input res;

output[3:0] sum;

parameter frequency_clk=24;// 设置时钟的参数

reg[24:0] cont;

reg[3:0] sum;

reg spulse;

always@(posedge clk or negedge res) begin

if(~res)begin

cont = 0;

sum = 0;

spulse = 0;

end

else begin

if(cont==frequency_clk*1000-1)begin

cont = 0;

end

else begin

cont = cont+1;

end

if(cont==0)begin

spulse = 1;

end

else begin

spulse = 0;

end

if(spulse)begin

if(sum==9)begin

sum = 0;

end

else begin

sum = sum+1;

end

end

end

end

endmodule

//testbench of scounter

module scounter_tb ;

reg clk;

reg res;

wire[3:0] sum;

scounter scounter(

.clk(clk),

.res(res),

.sum(sum)

);

initial begin

clk <= 0;

res <= 0;

#15 res <= 1;

#2000 $stop;

end

always #5 clk = ~clk;

endmodule

仿真波形

PS:24MHz过长,直接点run-all无法显示波形,降低频率 改为24000即可展现波形

1241

1241

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?